Methods of forming semiconductor constructions and integrated circuits

a technology of integrated circuits and semiconductors, applied in the direction of pulse techniques, transistors, solid-state devices, etc., can solve the problems of limited performance of tfts, limited carrier mobilities, high power consumption, etc., and achieve the effect of reducing device area, suitable performance characteristics and wireability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

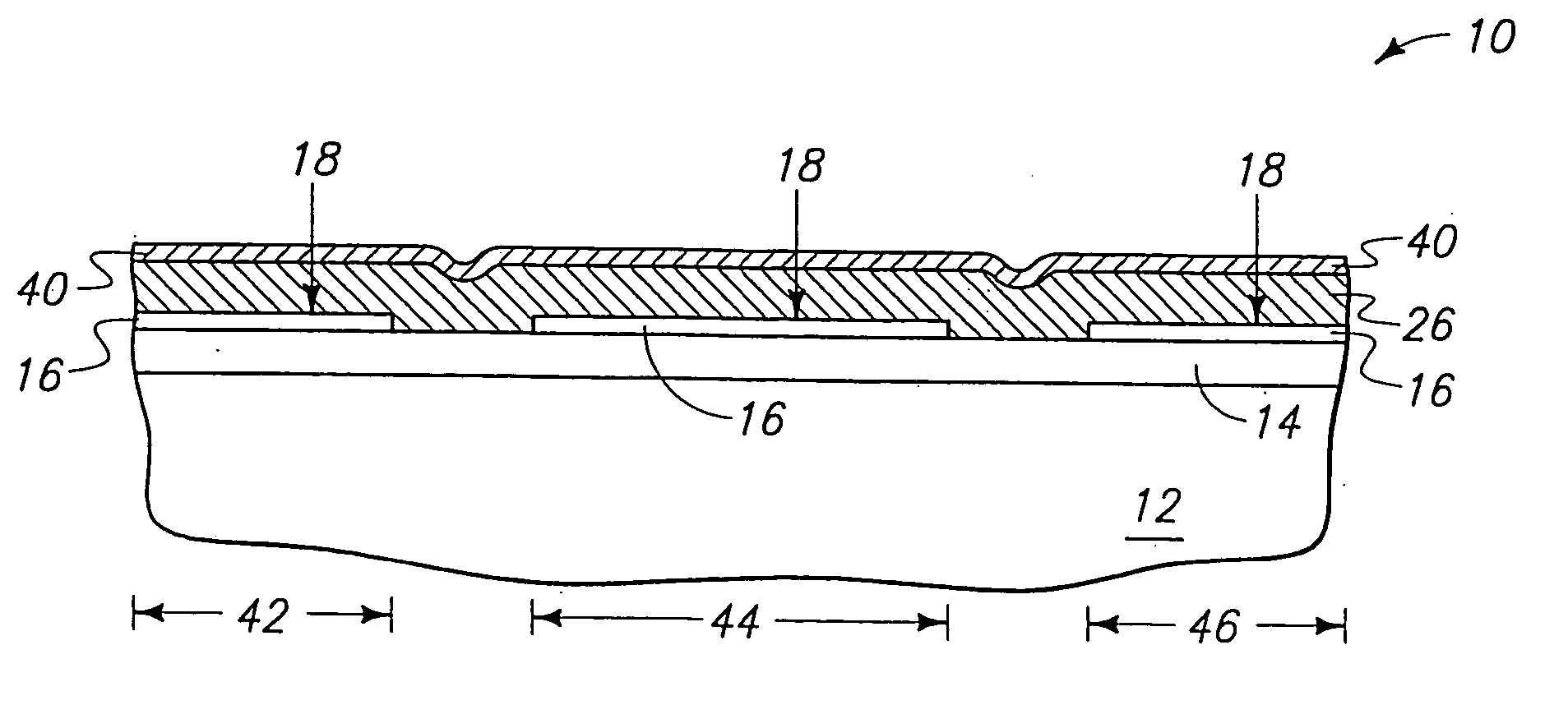

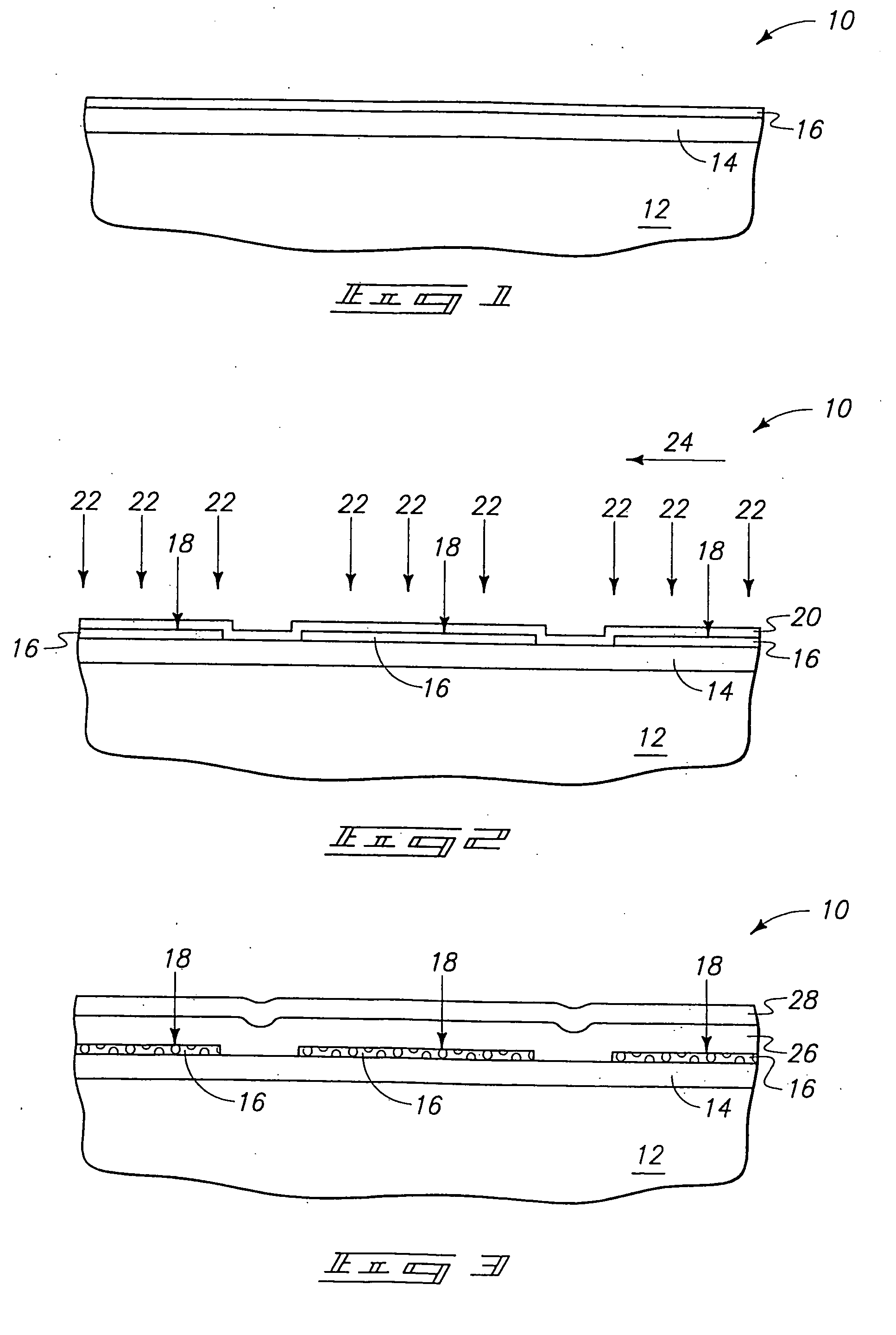

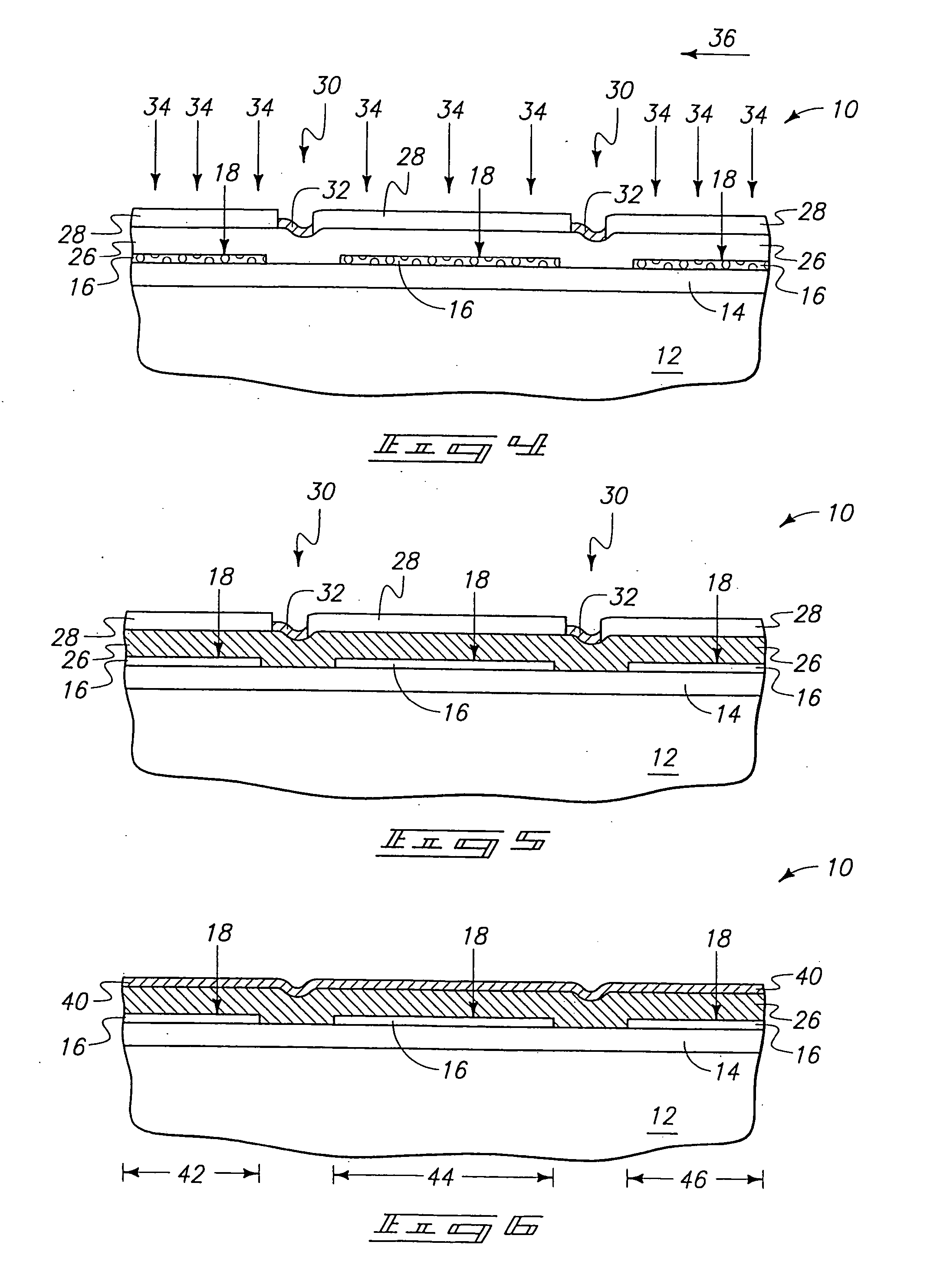

[0038] The invention pertains to logic devices. Exemplary logic devices are described with reference to FIGS. 10-17. Prior to the discussion of the exemplary logic devices, a processing sequence for forming and utilizing preferred TFT-based Si / Ge materials and device structures is described with reference to FIGS. 1-9.

[0039] Referring to FIG. 1, a fragment of a semiconductor construction 10 is illustrated at a preliminary processing stage. To aid in interpretation of the claims that follow, the terms “semiconductive substrate” and “semiconductor substrate” are defined to mean any construction comprising semiconductive material, including, but not limited to, bulk semiconductive materials such as a semiconductive wafer (either alone or in assemblies comprising other materials thereon), and semiconductive material layers (either alone or in assemblies comprising other materials). The term “substrate” refers to any supporting structure, including, but not limited to, the semiconductiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More