Circular Test Pads on Scribe Street Area

a technology of test pads and scribe streets, which is applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of increasing problems, reducing the overall yield of dies which can be fabricated from wafers, and damaged circuitry, so as to reduce reliability risks, increase wafer yield, and reduce yield loss at the wafer saw

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

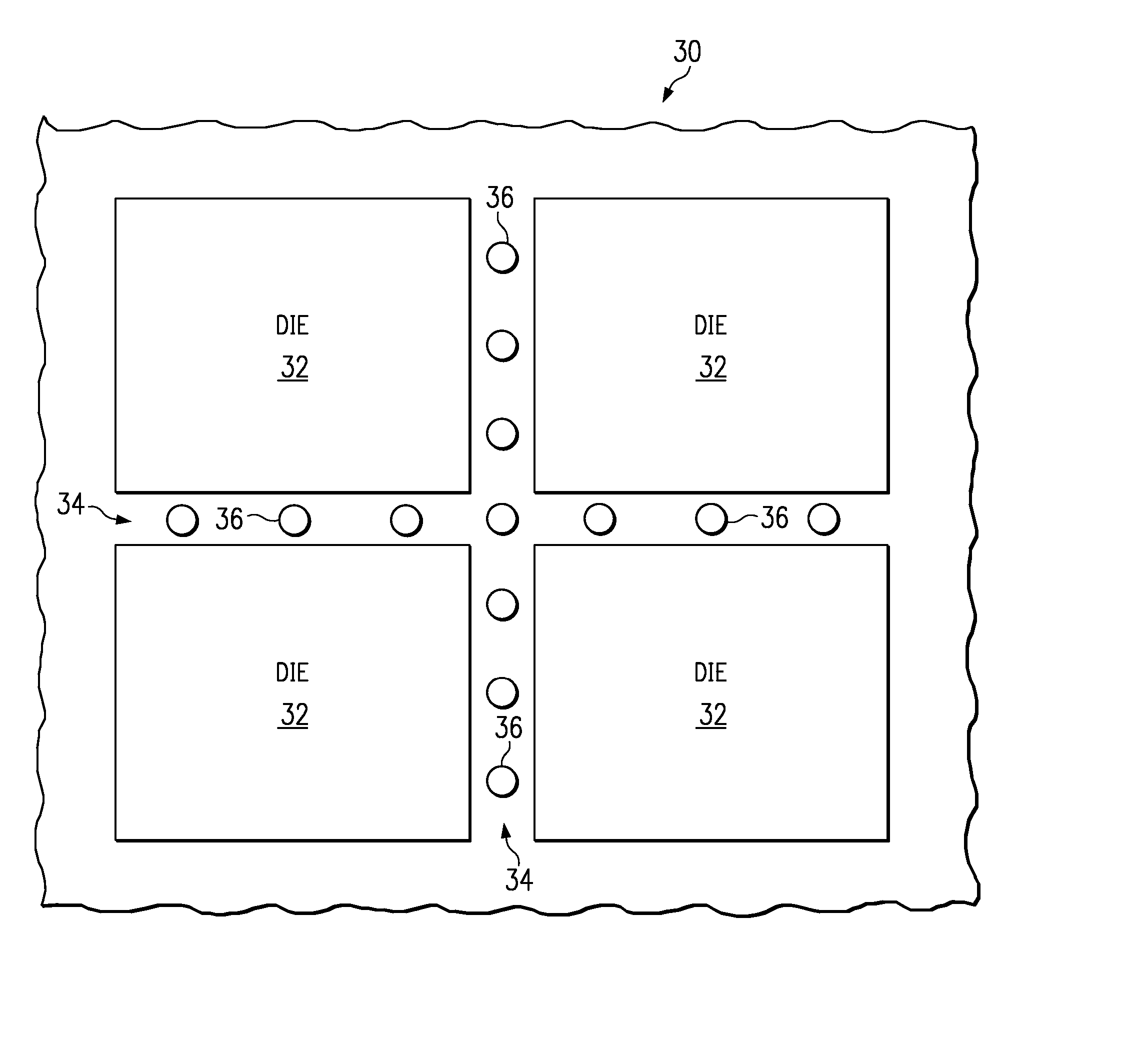

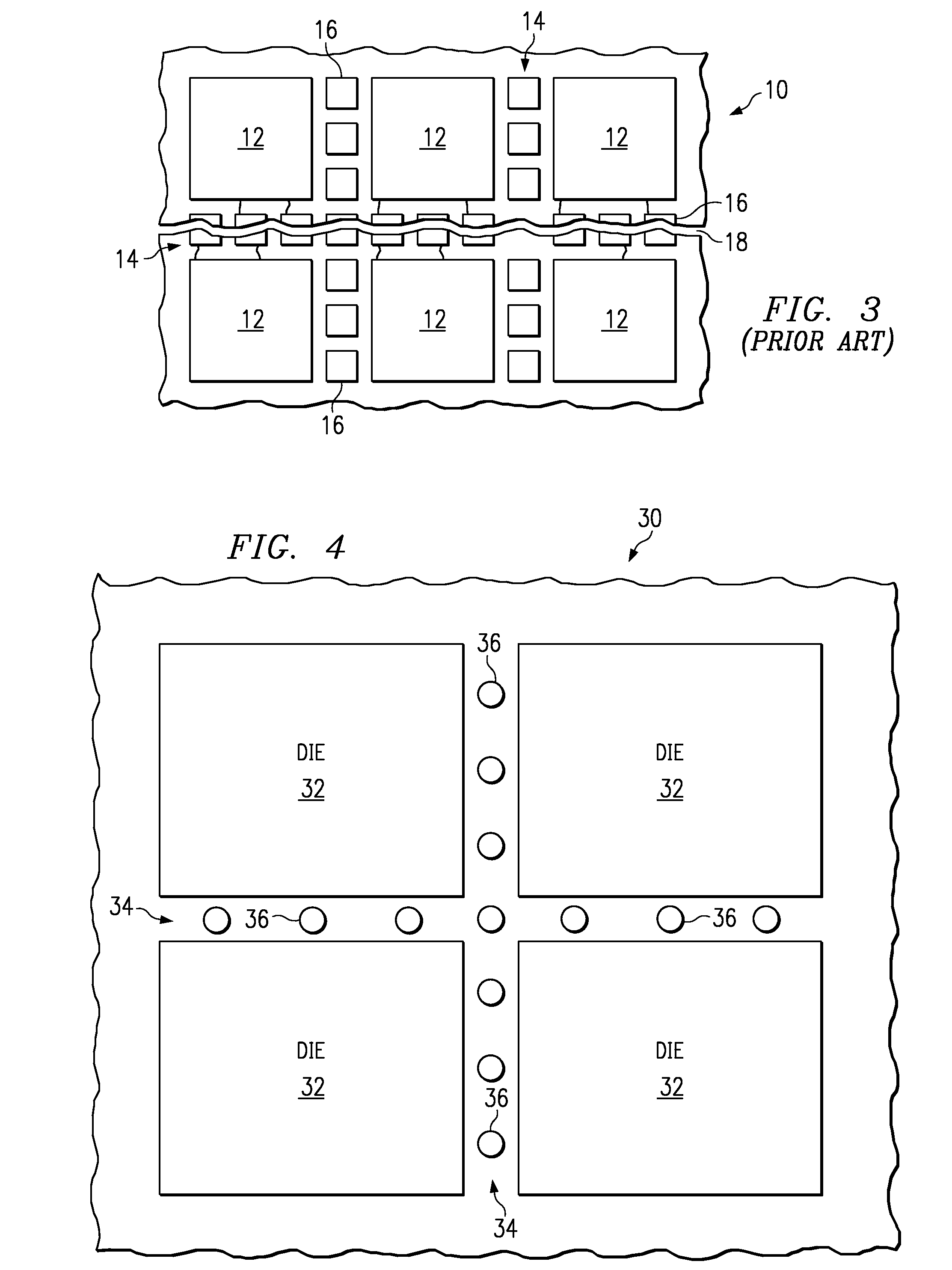

[0018] Referring now to FIG. 4, there is depicted at 30 a semiconductor wafer having a plurality of active circuits 32 (die) being formed upon the semiconductor wafer according to conventional semiconductor wafer fab processing. Defined in two dimensions between each of the formed die 32 are elongated scribe streets, generally shown at 34. Scribe streets 34 provide physical and electrical separation between the die 32, and are later cut using a wafer saw process to separate the active die for subsequent packaging.

[0019] Advantageously, as shown in FIG. 4, a plurality of test pads 36 are provided in the scribe street area 34 which have the curved profile, preferably shown as having a round periphery, as shown, but which could have other curved peripheries, such as oval or elliptical. Each of these test pads is electrically connected to one or more of the adjacent die 32, and provide a suitable electrical connection point for test equipment (not shown) to electrically test and operat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More