Patents

Literature

40 results about "Semiconductor fab" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

This is a list of semiconductor fabrication plants: A semiconductor fabrication plant is where integrated circuits (ICs), also known as microchips, are made.They are either operated by Integrated Device Manufacturers (IDMs) who design and manufacture ICs in-house and may also manufacture designs from design only firms (fabless companies), or by Pure Play foundries, who manufacture designs from ...

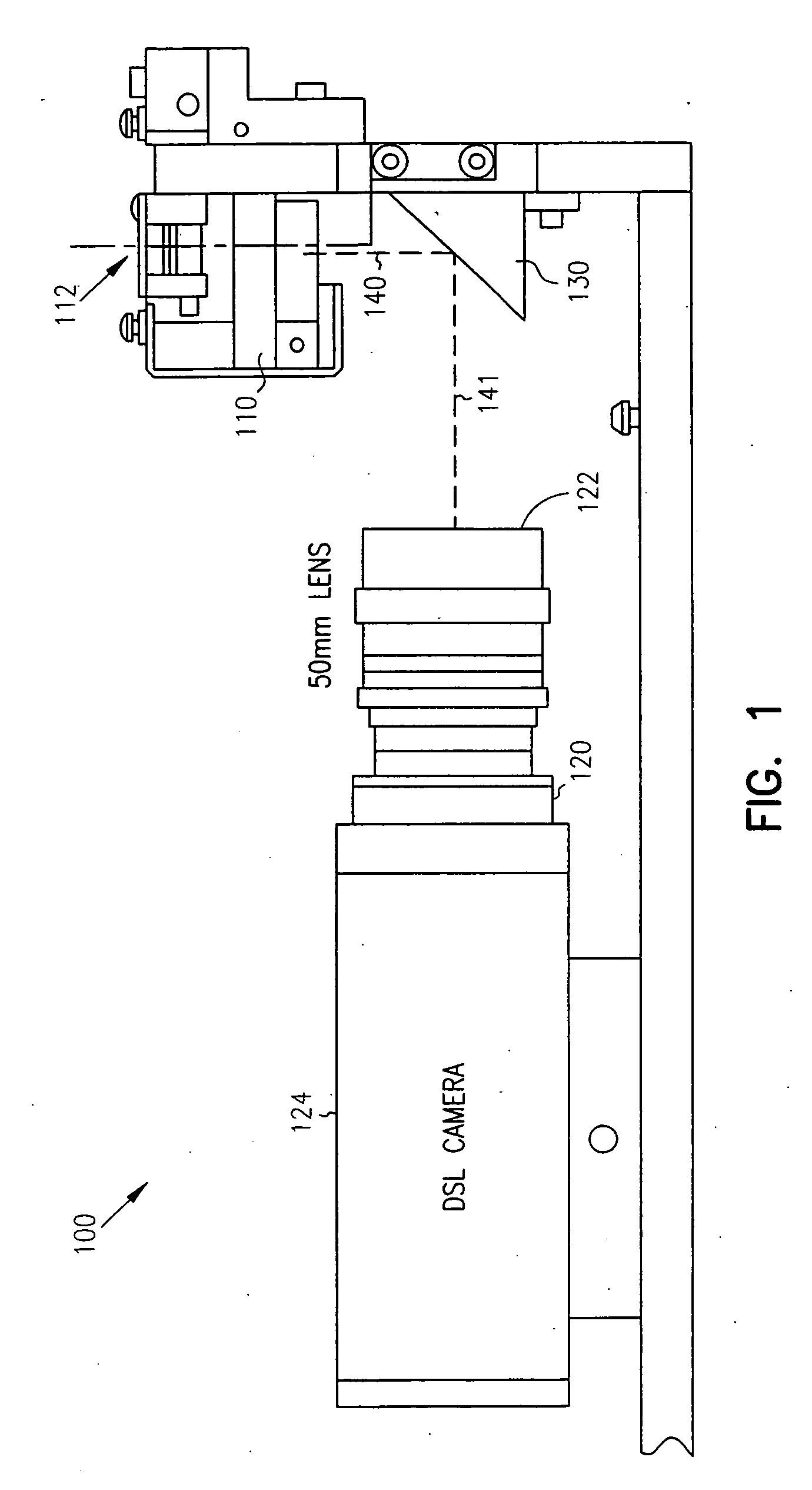

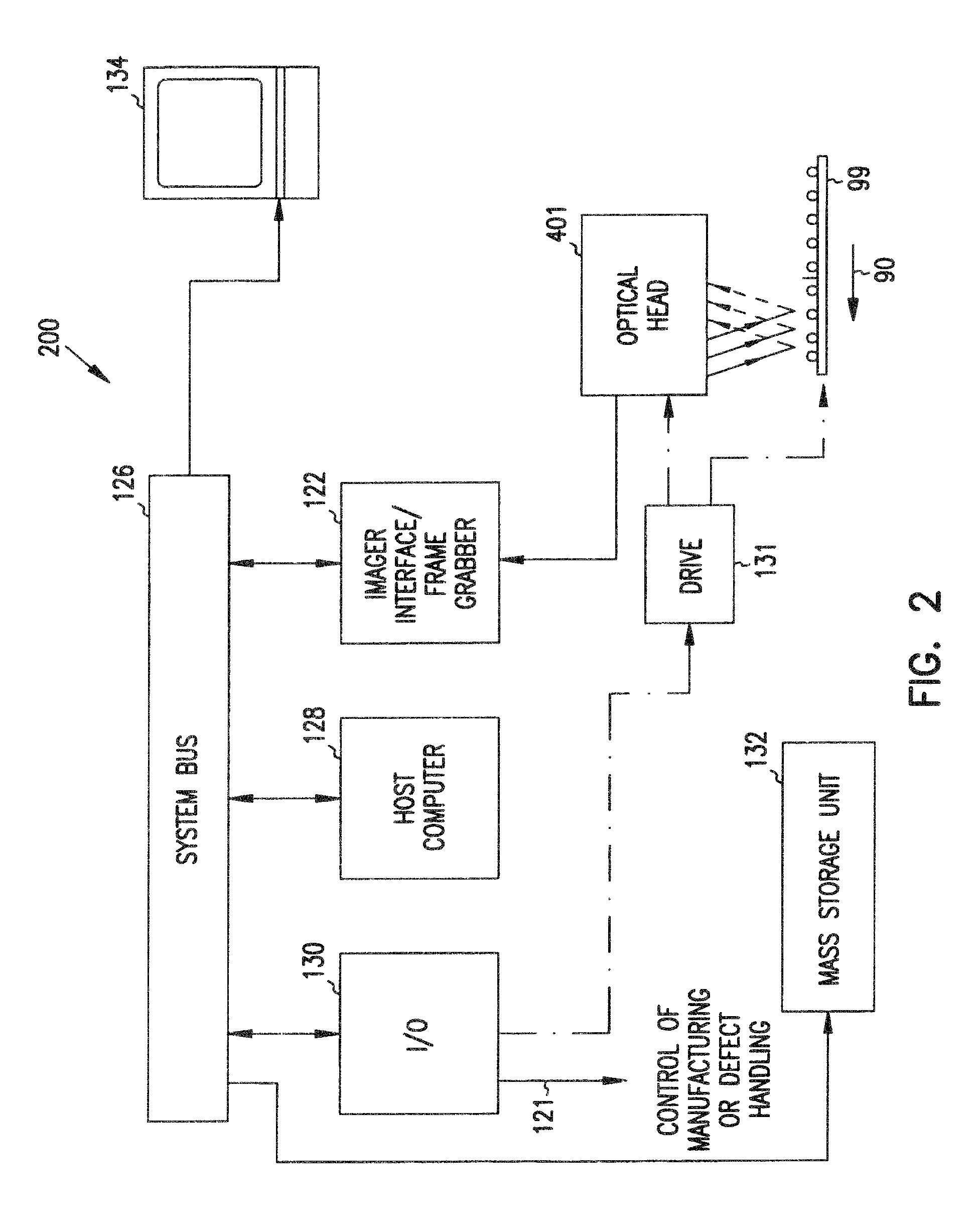

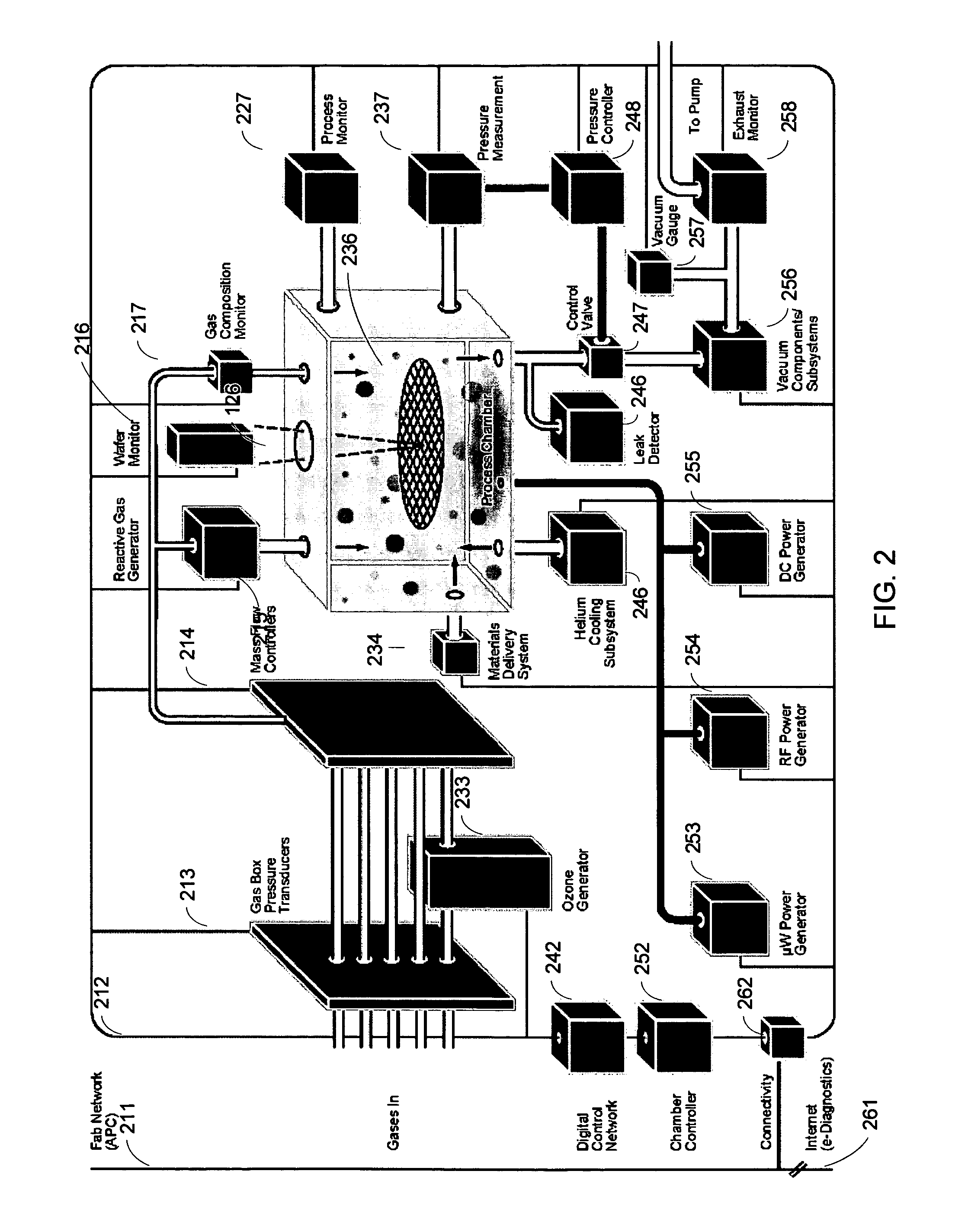

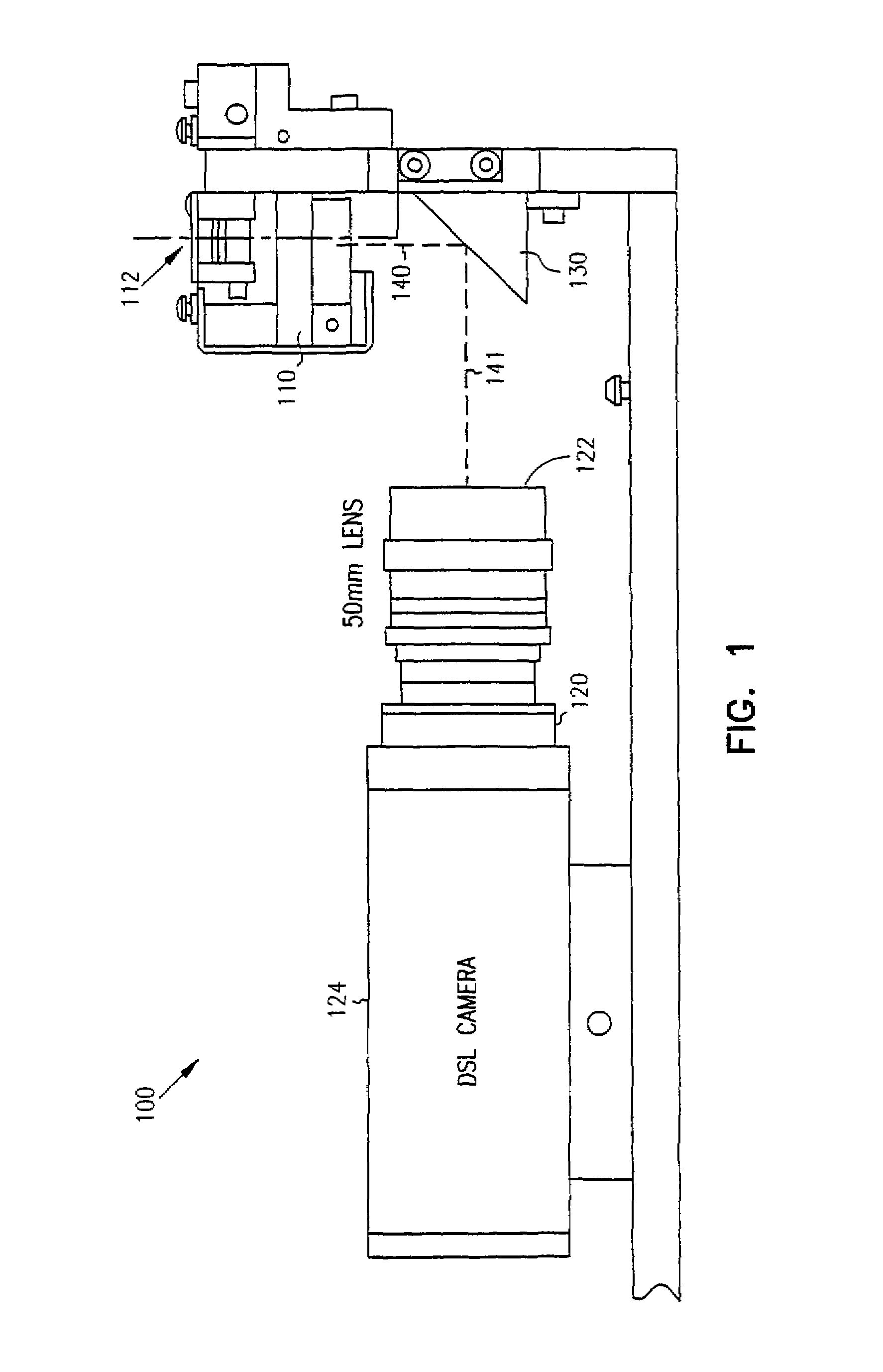

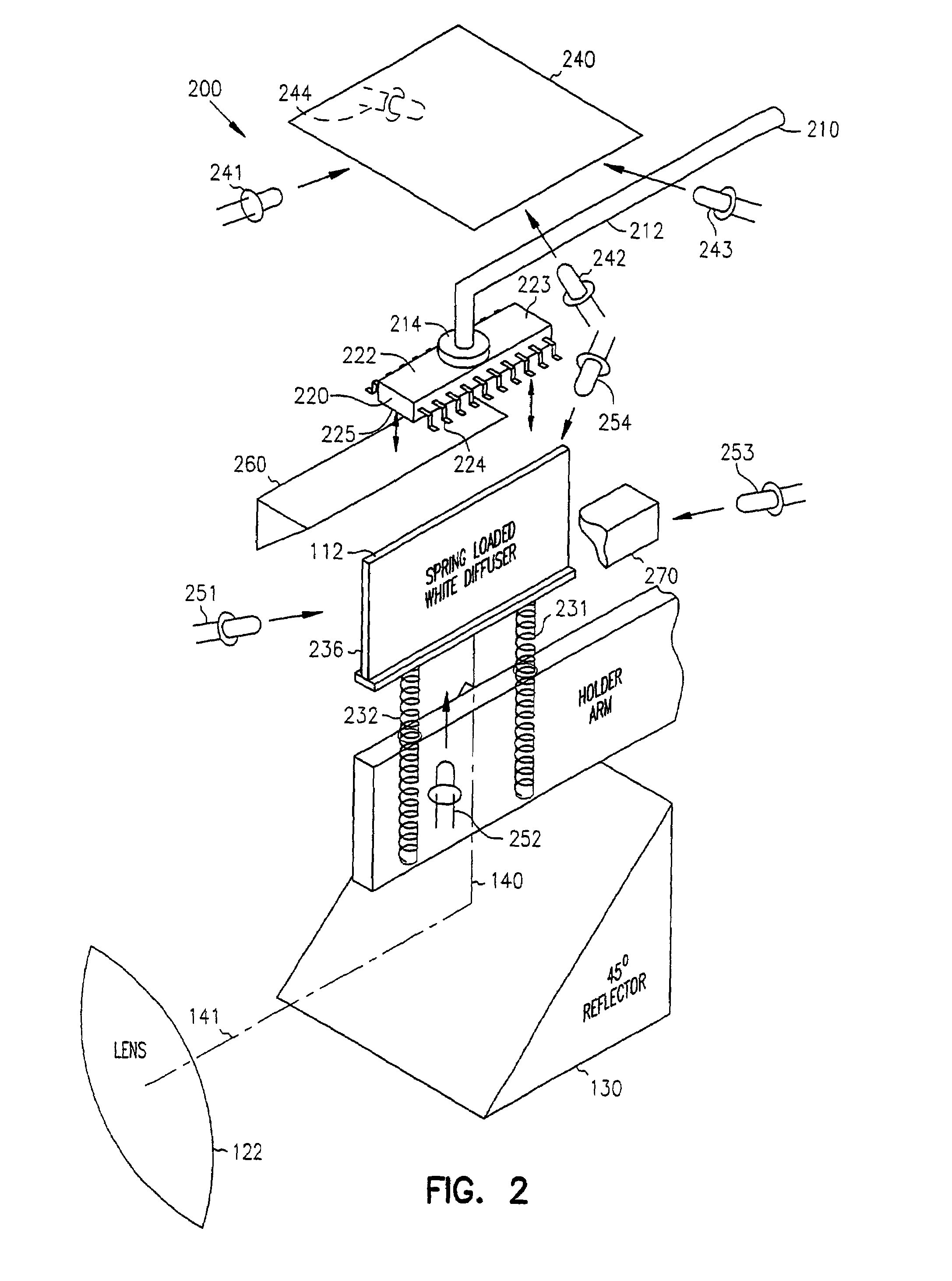

Imaging for a machine-vision system

InactiveUS6956963B2Prevents thermal driftLow variabilityImage analysisSemiconductor/solid-state device manufacturingImage detectionSemiconductor fab

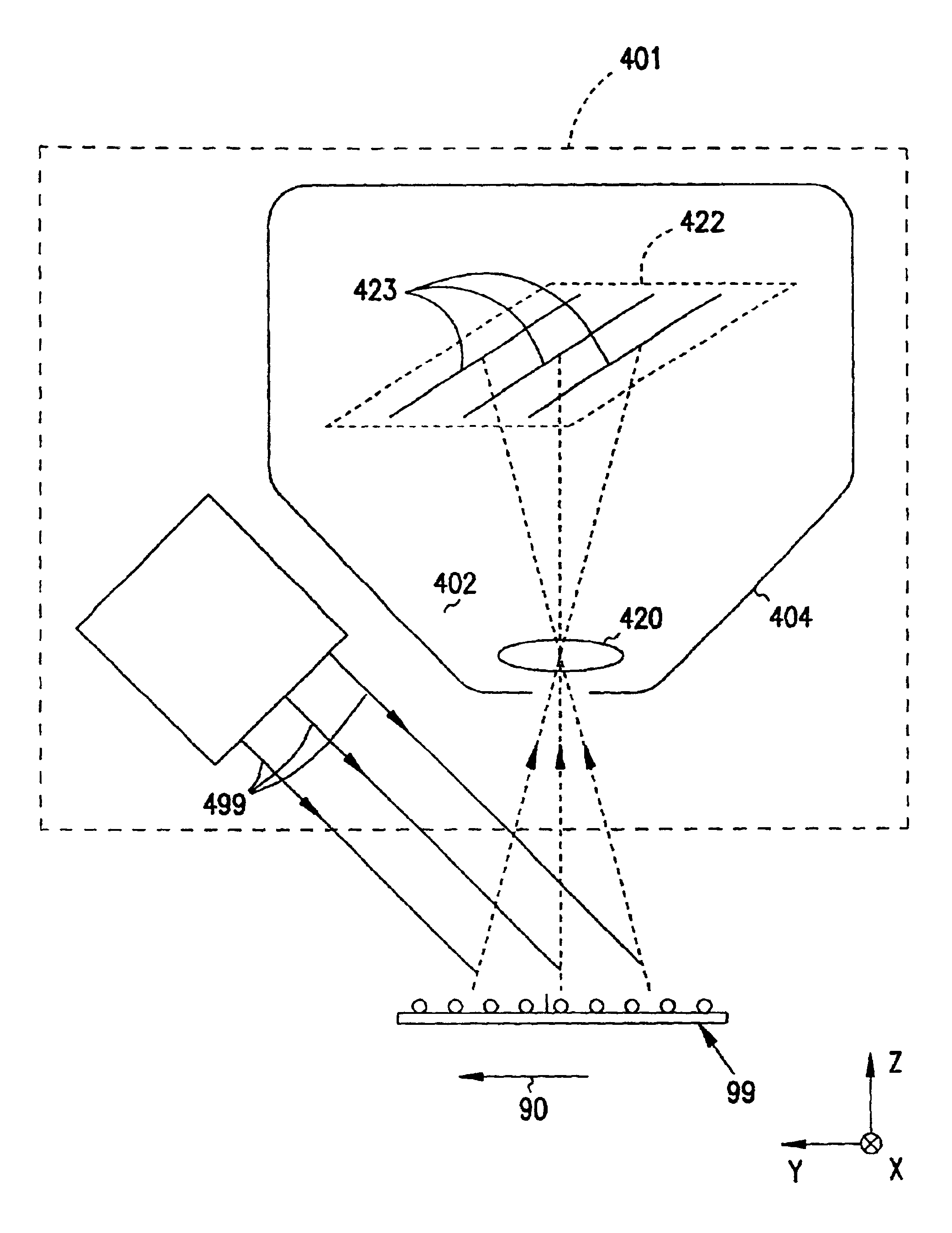

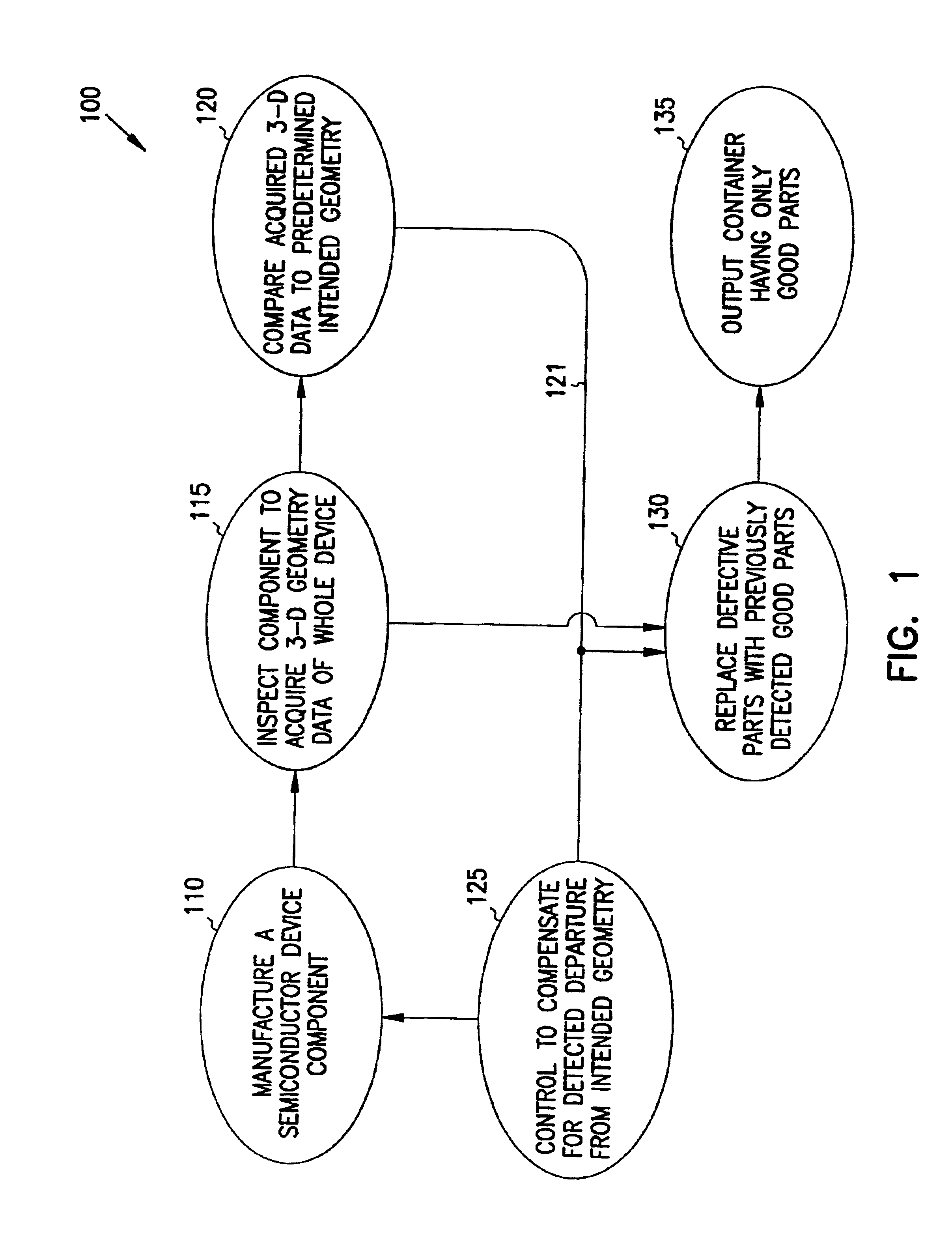

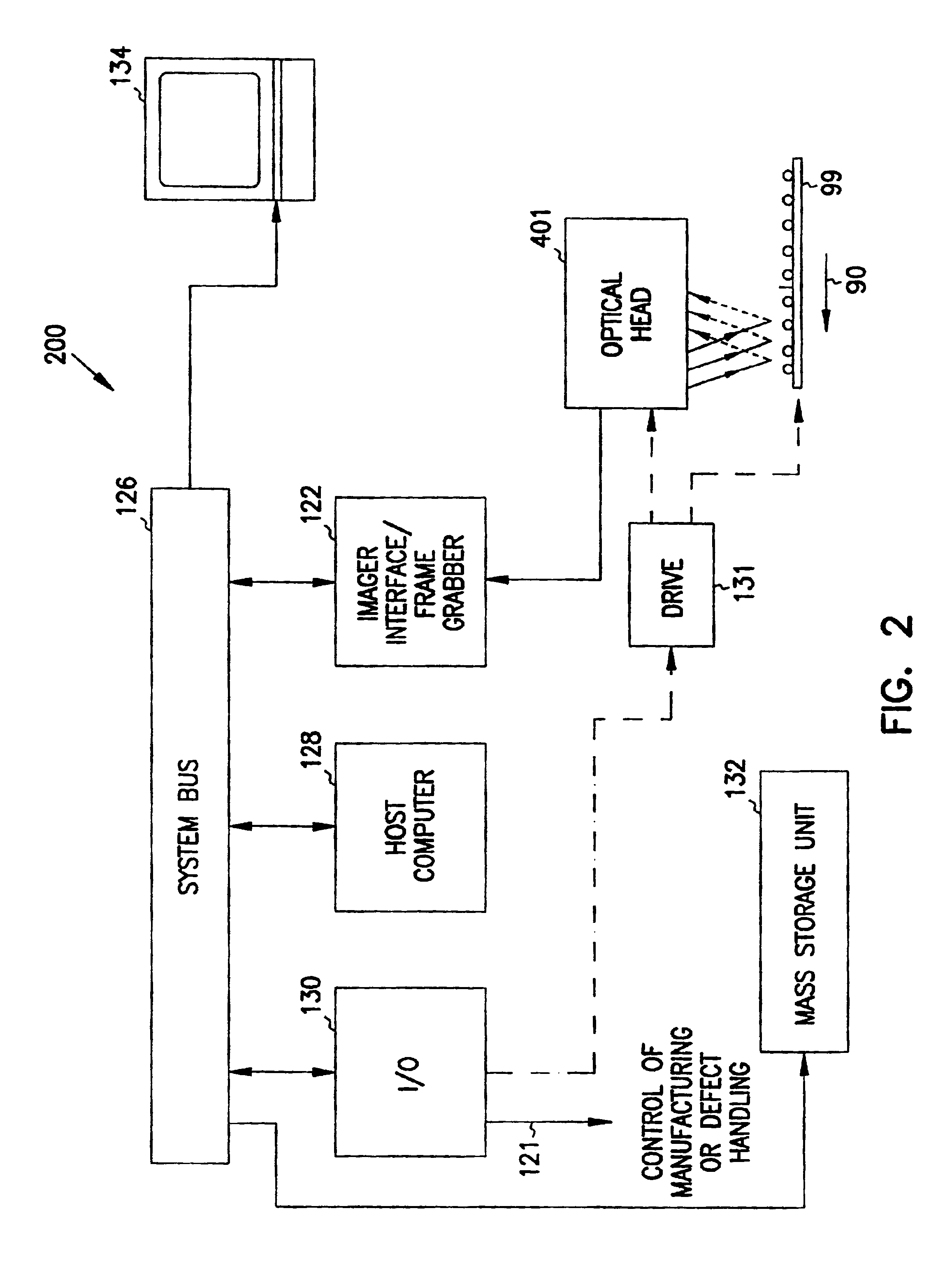

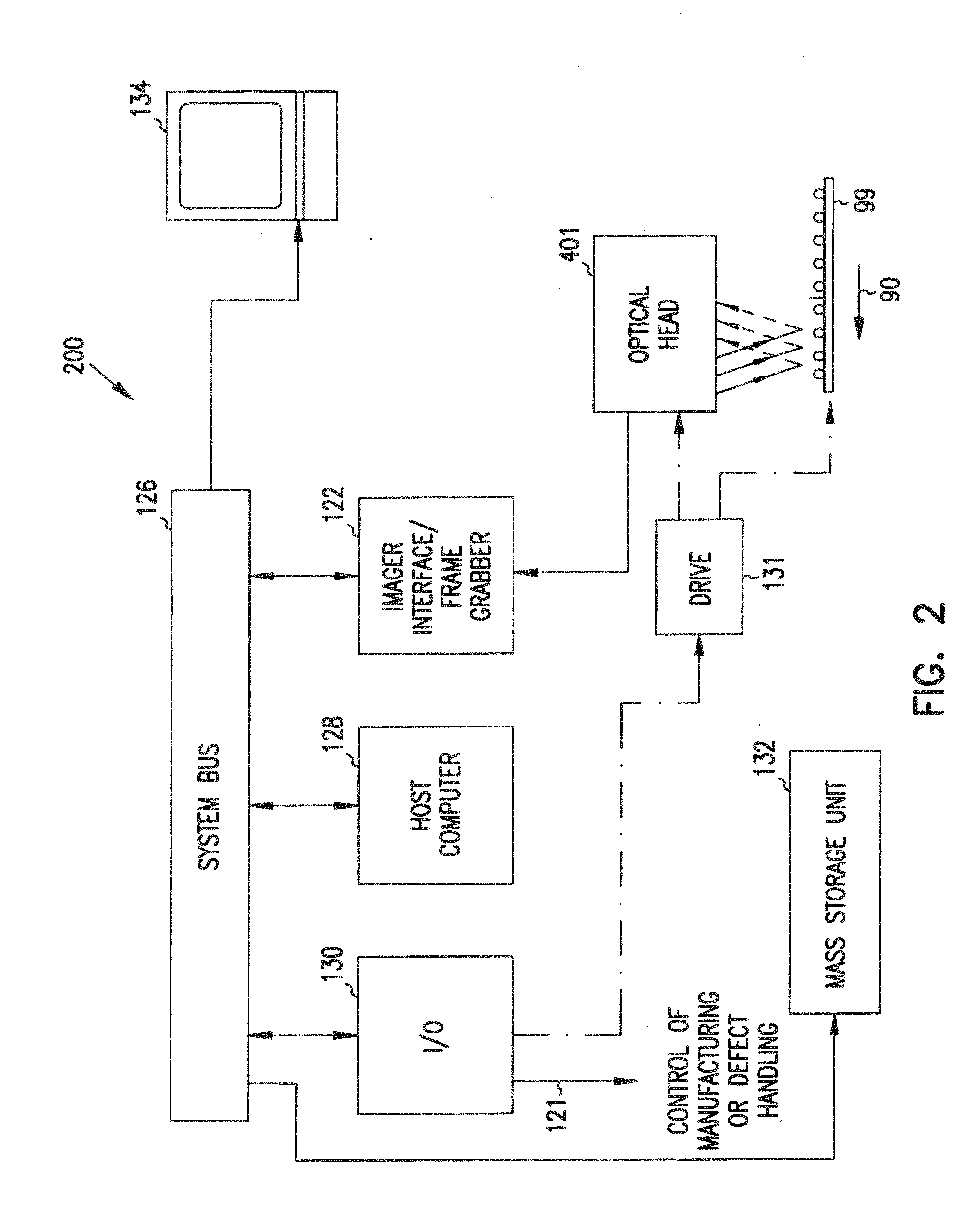

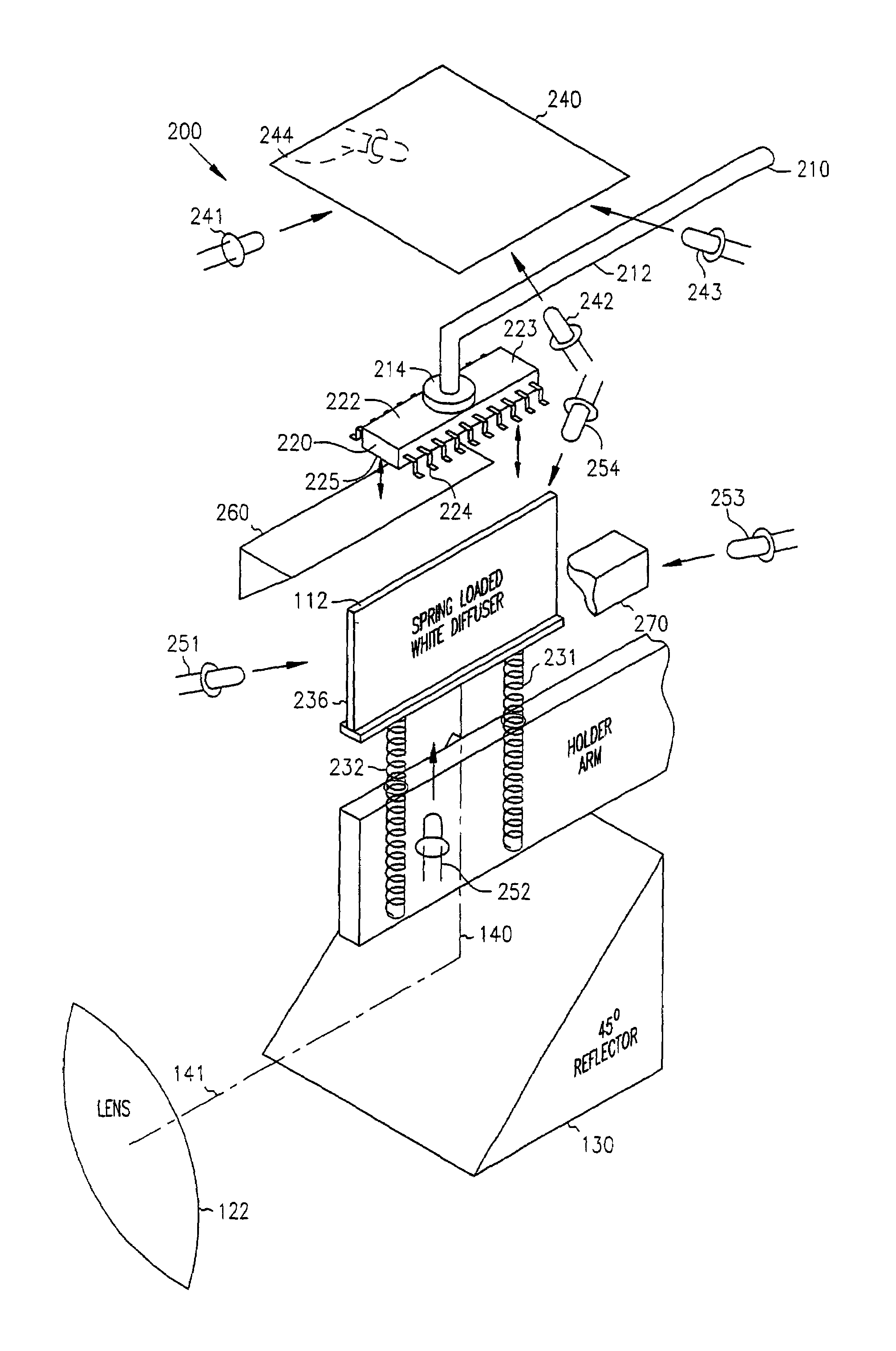

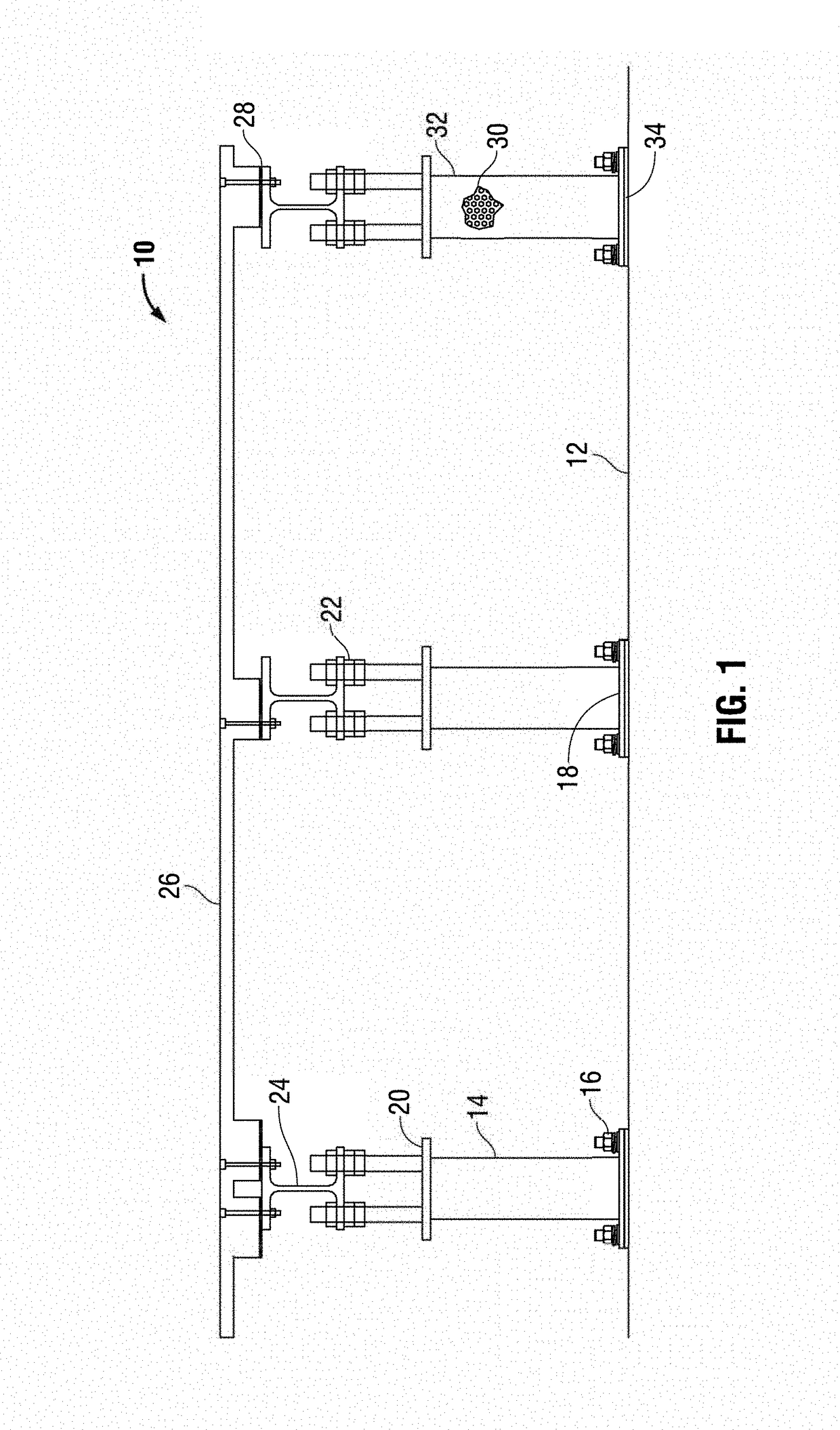

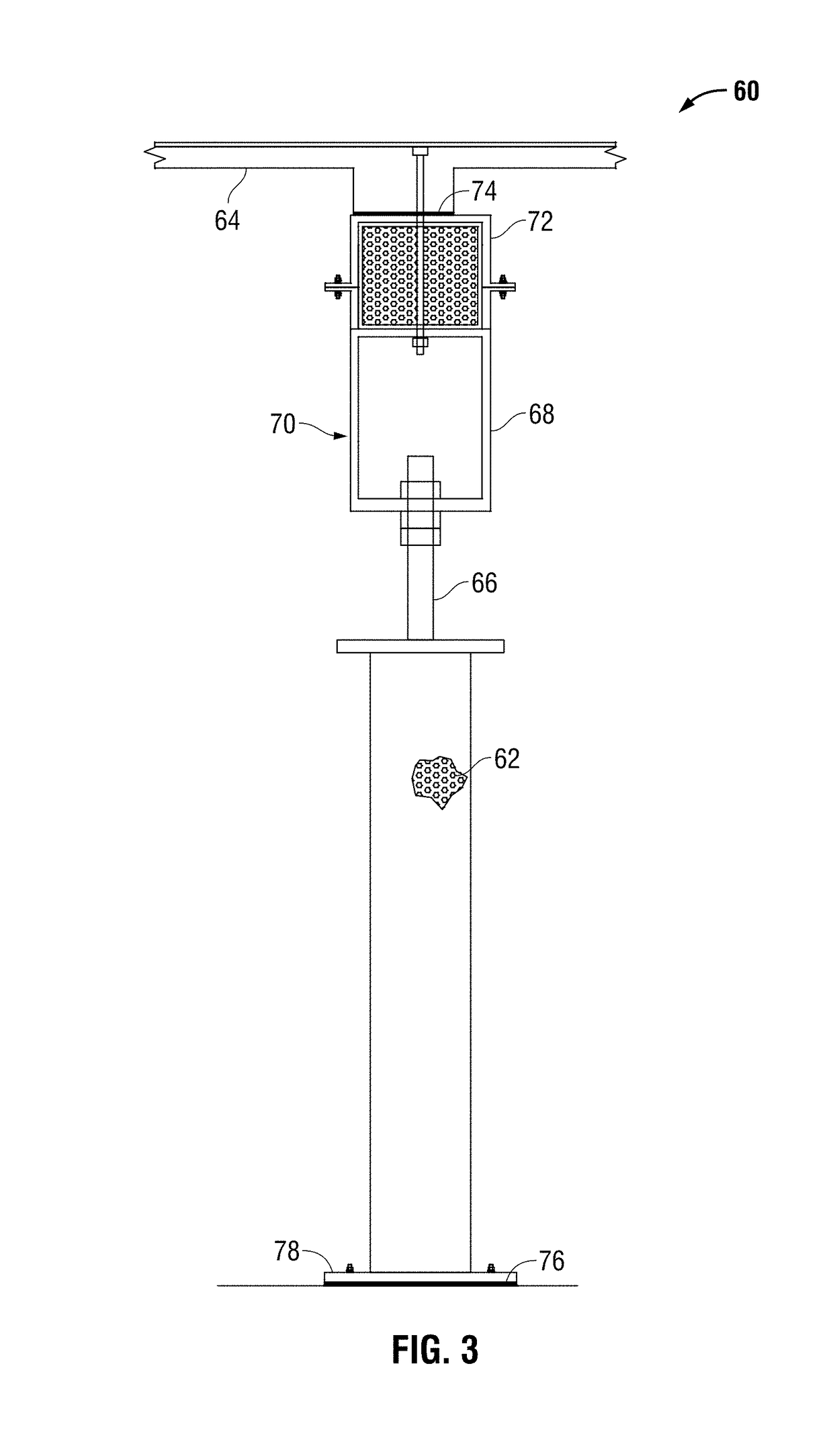

Manufacturing lines include inspection systems for monitoring the quality of parts produced. Manufacturing lines for making semiconductor devices generally inspect each fabricated part. The information obtained is used to fix manufacturing problems in the semiconductor fab plant. A machine-vision system for inspecting devices includes a light source for propagating light to the device and an image detector that receives light from the device. Also included is a light sensor assembly for receiving a portion of the light from the light source. The light sensor assembly produces an output signal responsive to the intensity of the light received at the light sensor assembly. A controller controls the amount of light received by the image detector to a desired intensity range in response to the output from the light sensor. The image detector may include an array of imaging pixels. The imaging system may also include a memory device which stores correction values for at least one of the pixels in the array of imaging pixels. To minimize or control thermal drift of signals output from an array of imaging pixels, the machine-vision system may also include a cooling element attached to the imaging device. The light source for propagating light to the device may be strobed. The image detector that receives light from the device remains in a fixed position with respect to the strobed light source. A translation element moves the strobed light source and image detector with respect to the device. The strobed light may be alternated between a first and second level.

Owner:ISMECA SEMICONDUCTOR HOLDING SA

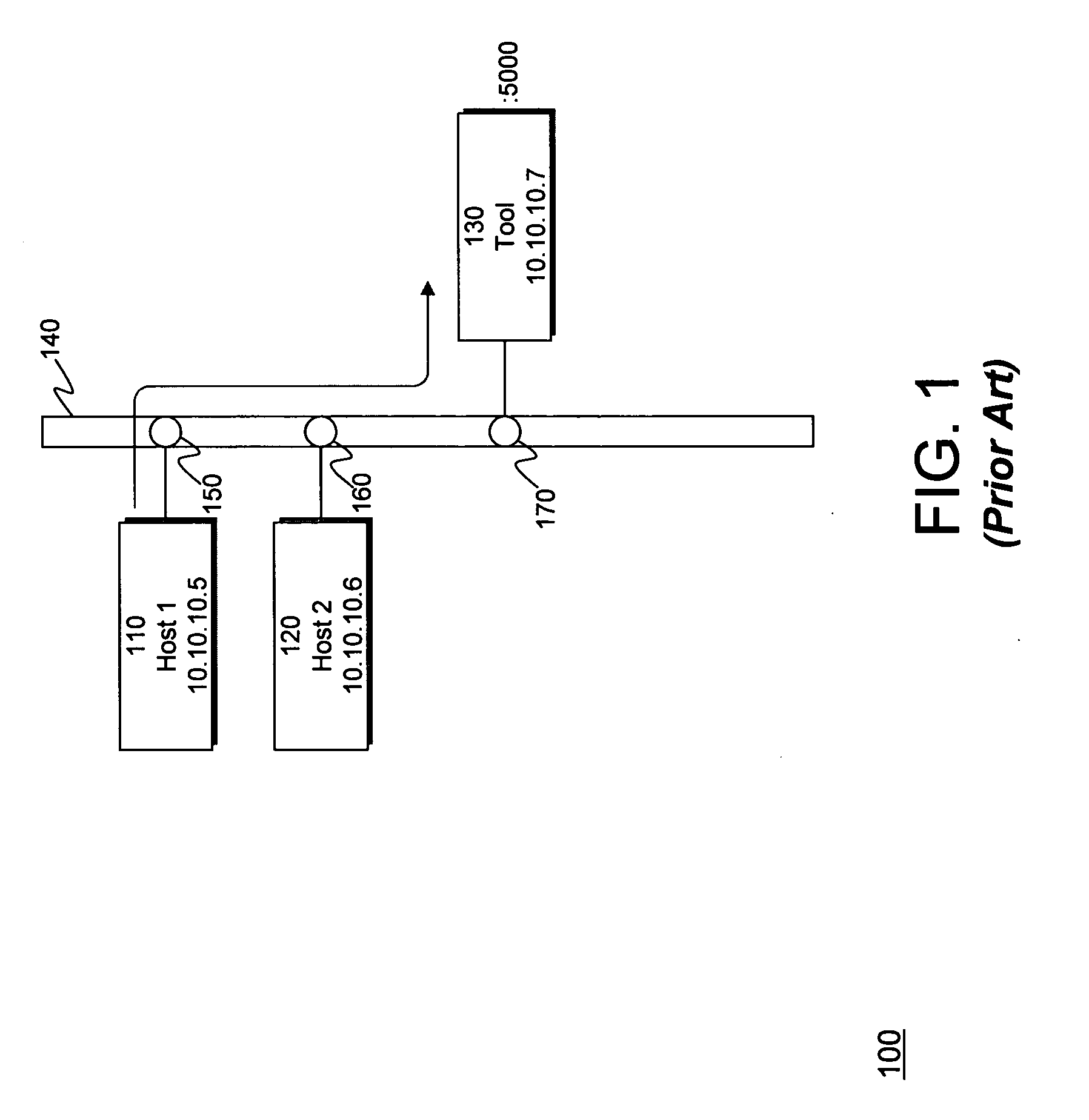

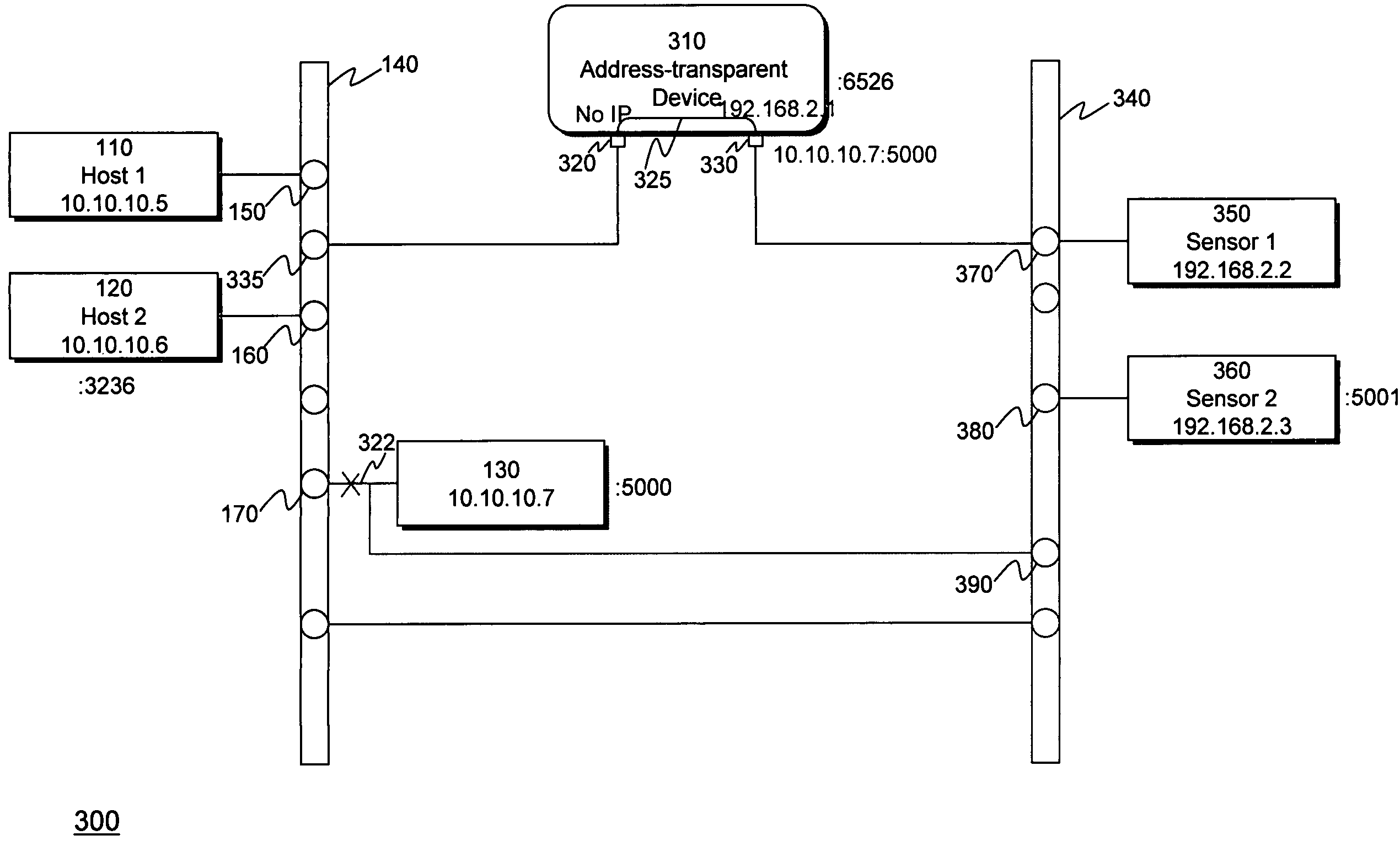

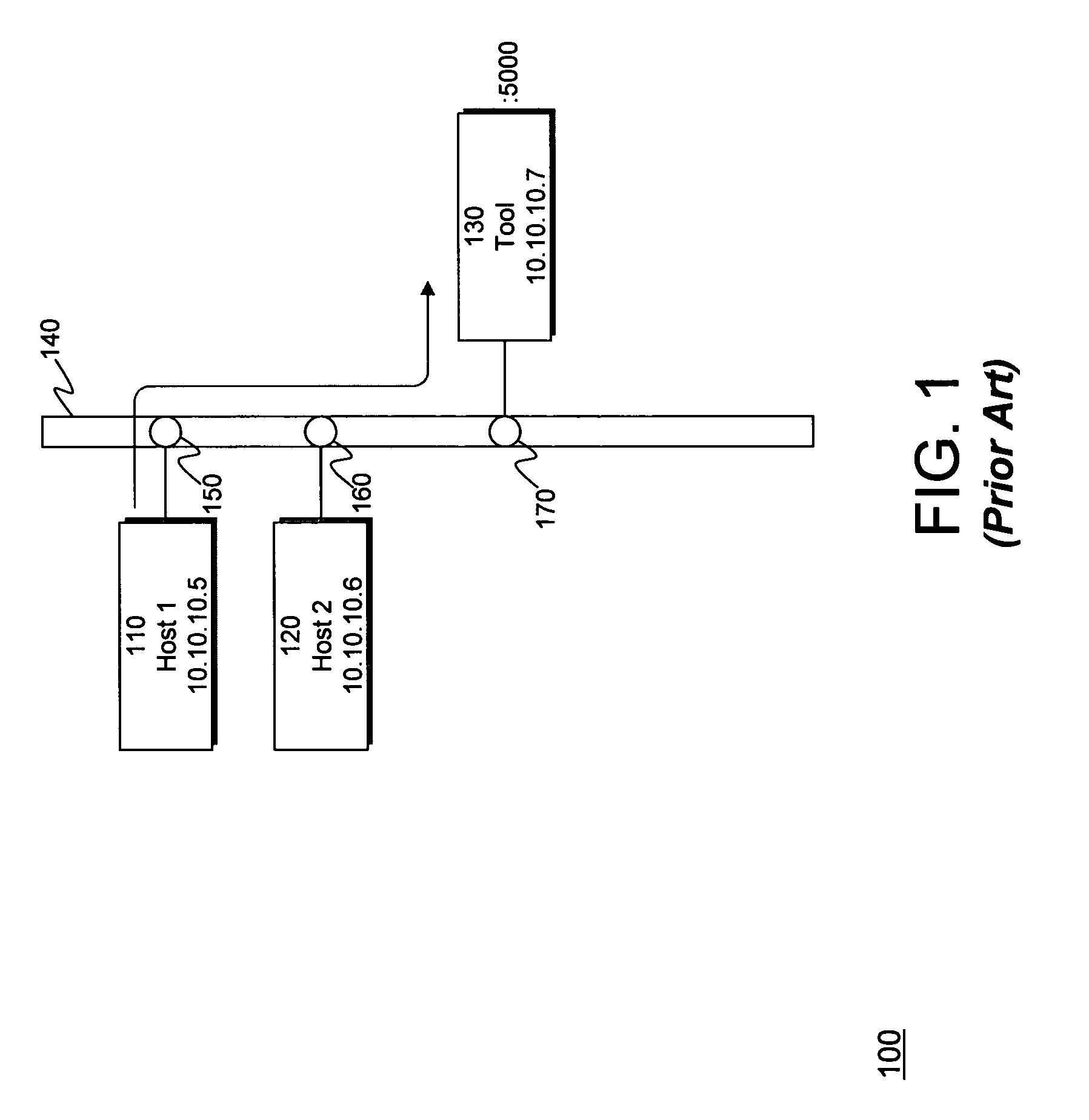

Address-transparent device and method

ActiveUS20070008972A1Significant delaySignificant feeSemiconductor/solid-state device manufacturingData switching by path configurationData streamIp address

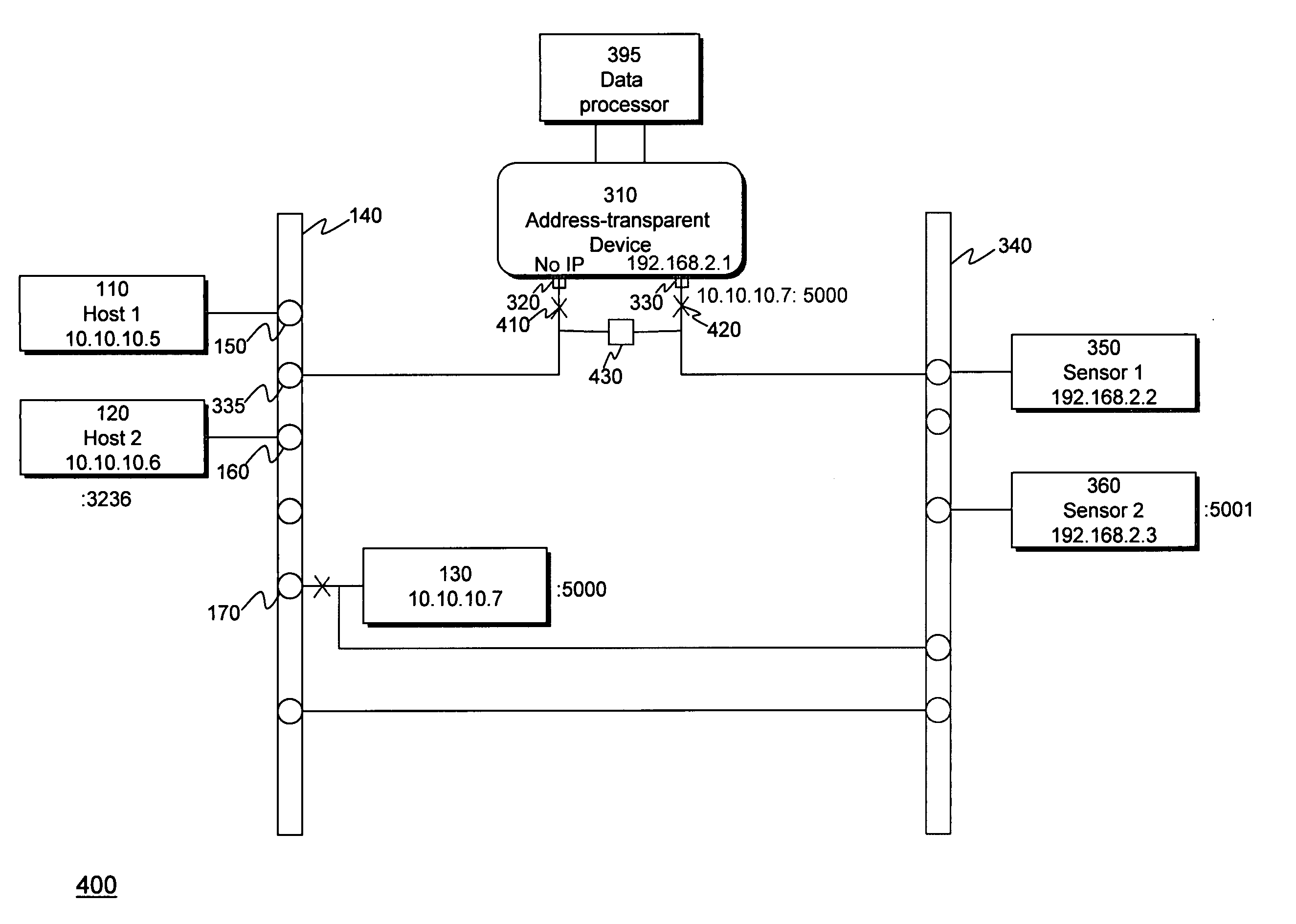

An address-transparent device is disclosed that couples between two network interfaces in a semiconductor fab for communicating packets between a host coupled to a first network interface and a tool coupled to a second network interface. Alternatively, the address-transparent device couples between two networks in a semiconductor fab for communicating packets between a host on a first network and a tool on a second network. In a first aspect of the invention, the address-transparent device routes packets between the first network and the second network that is independent of any protocol. The address-transparent device couples to the host through the first network and couples to the tool through the second network where the address-transparent device having a first port with no IP address and a second port with a subnet IP address. In a second aspect of the invention, the address-transparent device intercepts packets for local use by a data consumer that resides within or outside of the address-transparent device. The address-transparent device can intercept all or a portion of data streams, while forwards other portions of data streams to a destination. The header of the original packet is stored for subsequent use for sending a reply to an intercepted packet. In a third aspect of the invention, the address-transparent device reroutes packet to another destination by changing the header of the received packet. The header of the original packet is modified, replacing the original header information with the header information of the destination device. The header of the original packet is stored for subsequent use for sending a reply to a rerouted packet.

Owner:MKS INSTR INC

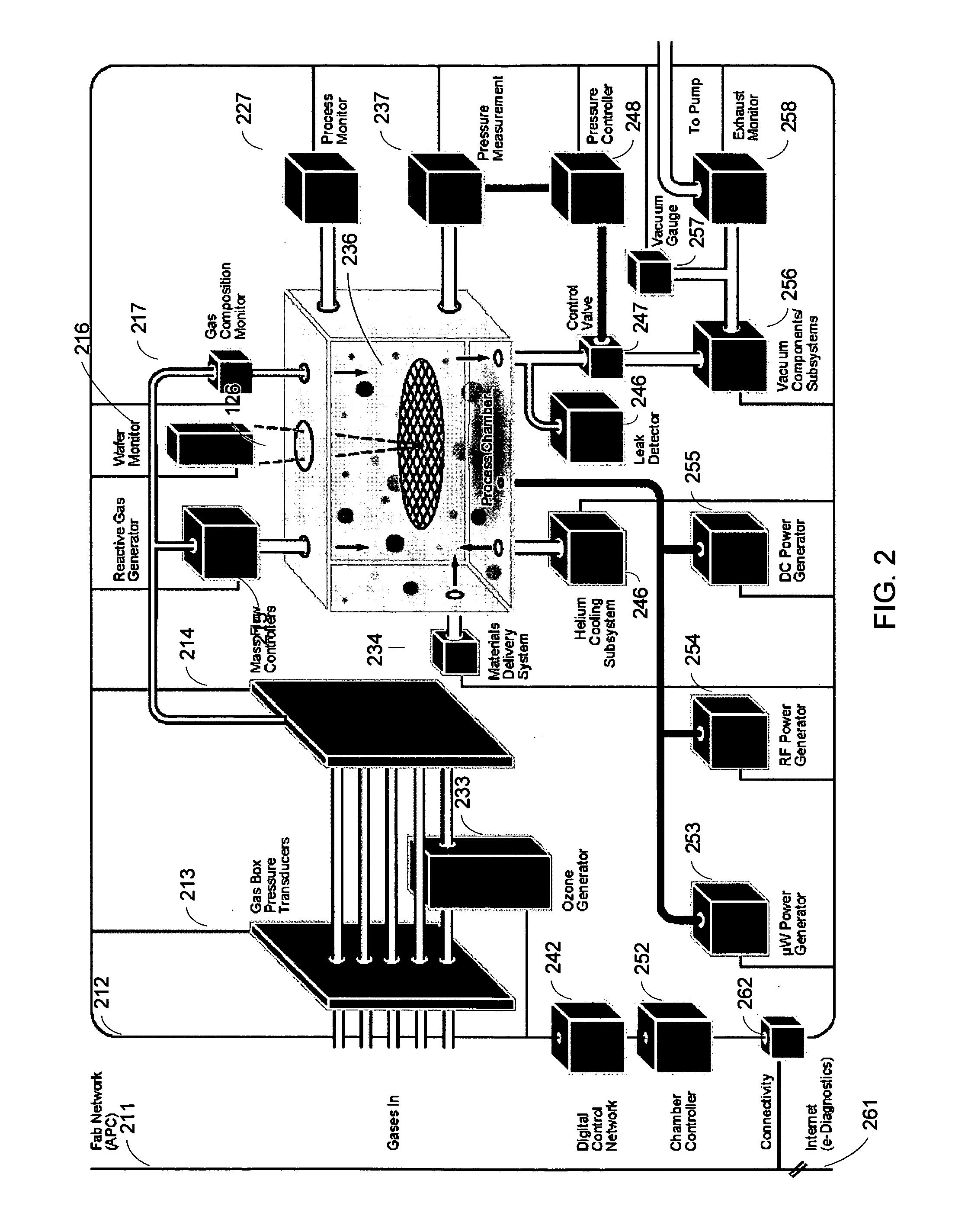

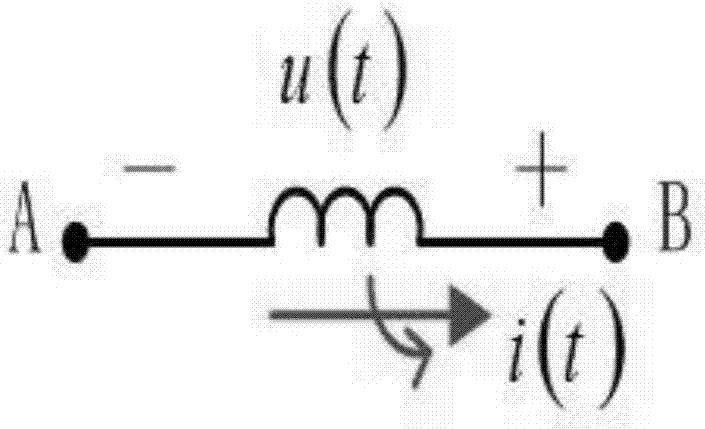

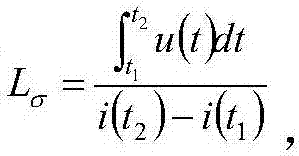

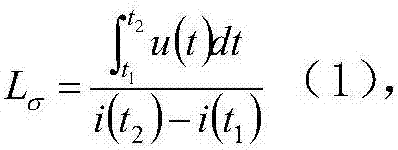

Measurement device and measurement method for stray inductance in IGBT module

PendingCN107102211AEasy to buildAccurate Parasitic InductanceResistance/reactance/impedenceStray inductanceDc capacitor

The invention relates to a measurement device for stray inductance in an IGBT module. The measurement device is characterized in that the measurement device comprises a power supply device, a to-be-measured IGBT module, a current probe, a voltage probe, an oscilloscope, a pulse triggering device, controllable switches S1, S2, S3, a DC capacitor C1, a DC discharging resistor R1, a load inductor L1 and a freewheeling diode D1; the controllable switch S2 is serially connected with the DC discharging resistor R1 and is parallelly connected with the DC capacitor C1; the freewheeling diode D1, the controllable switch S3 and the to-be-measured IGBT module are serially connected; the pulse triggering device is connected with the controllable switch S3; and the load inductor L1 is parallelly connected with two sides of the freewheeling diode D1. The measurement device can effectively evaluate induction voltage of an inner packaging parasitic parameter when the IGBT module is in a switching-off transient state. The packaged stray inductance which is calculated according to the voltage and current over two ends of a parasitic inductor is more practical and can be used for evaluating an IGBT safety margin, and furthermore can be used for verifying IGBT module designing. The measurement device and the measurement method have a certain meaning to semiconductor manufacturers and IGBT application parties.

Owner:CHINA UNIV OF MINING & TECH

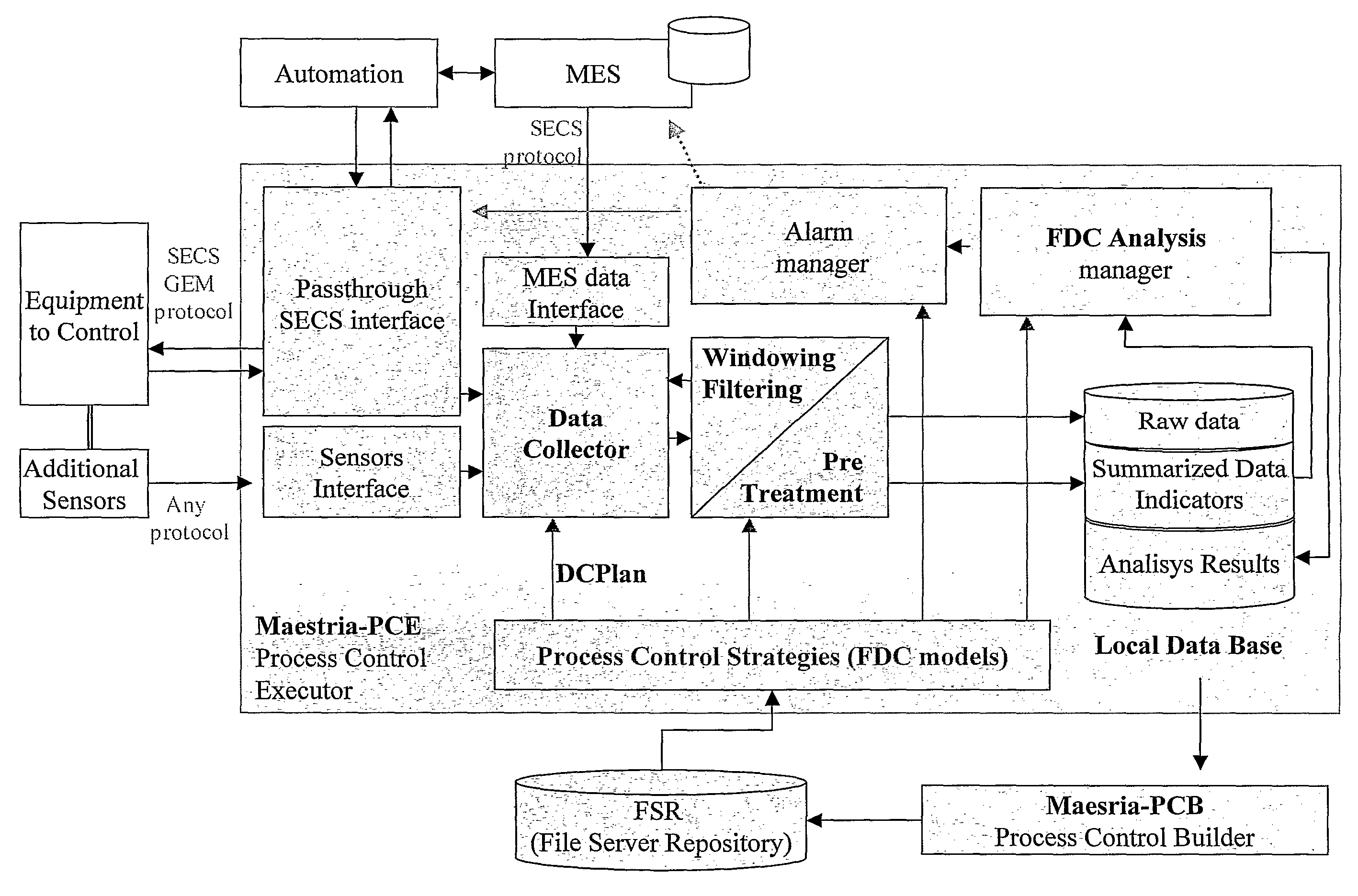

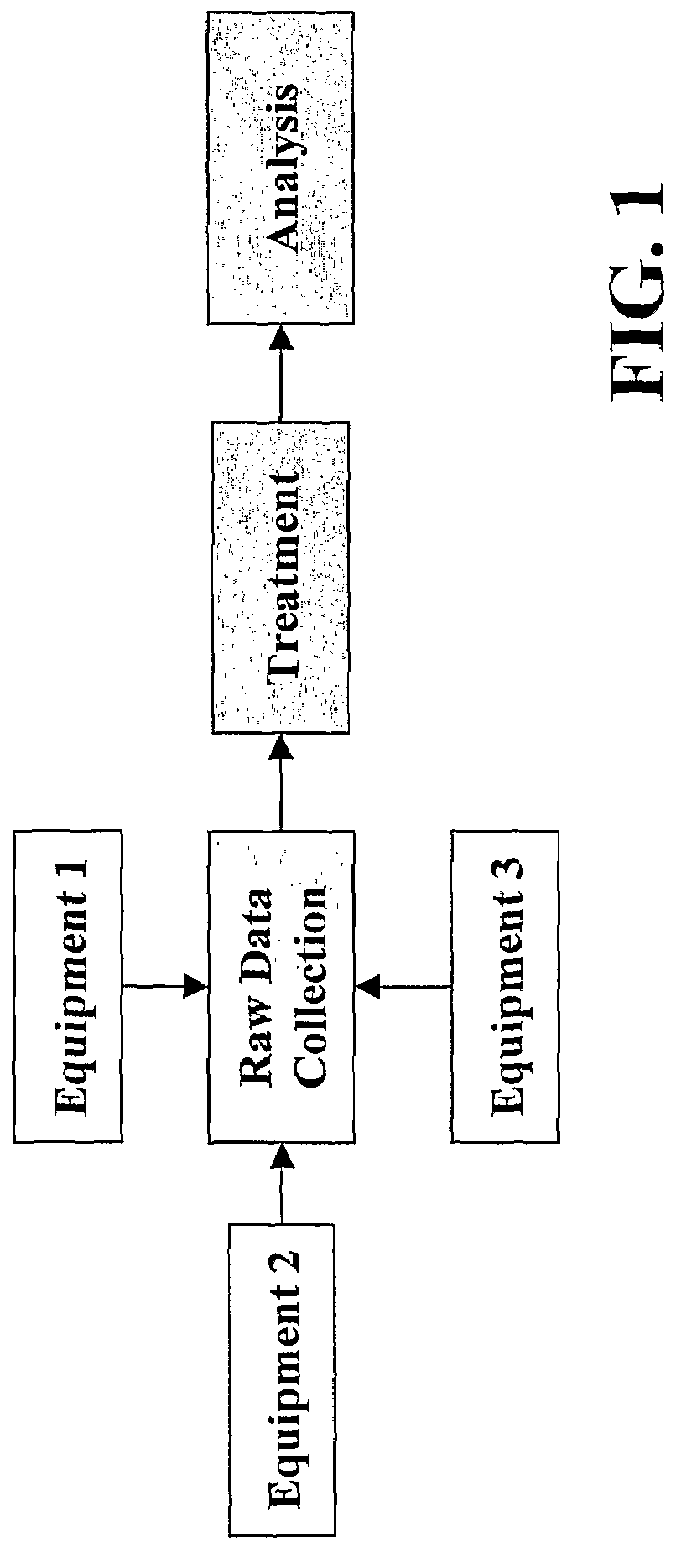

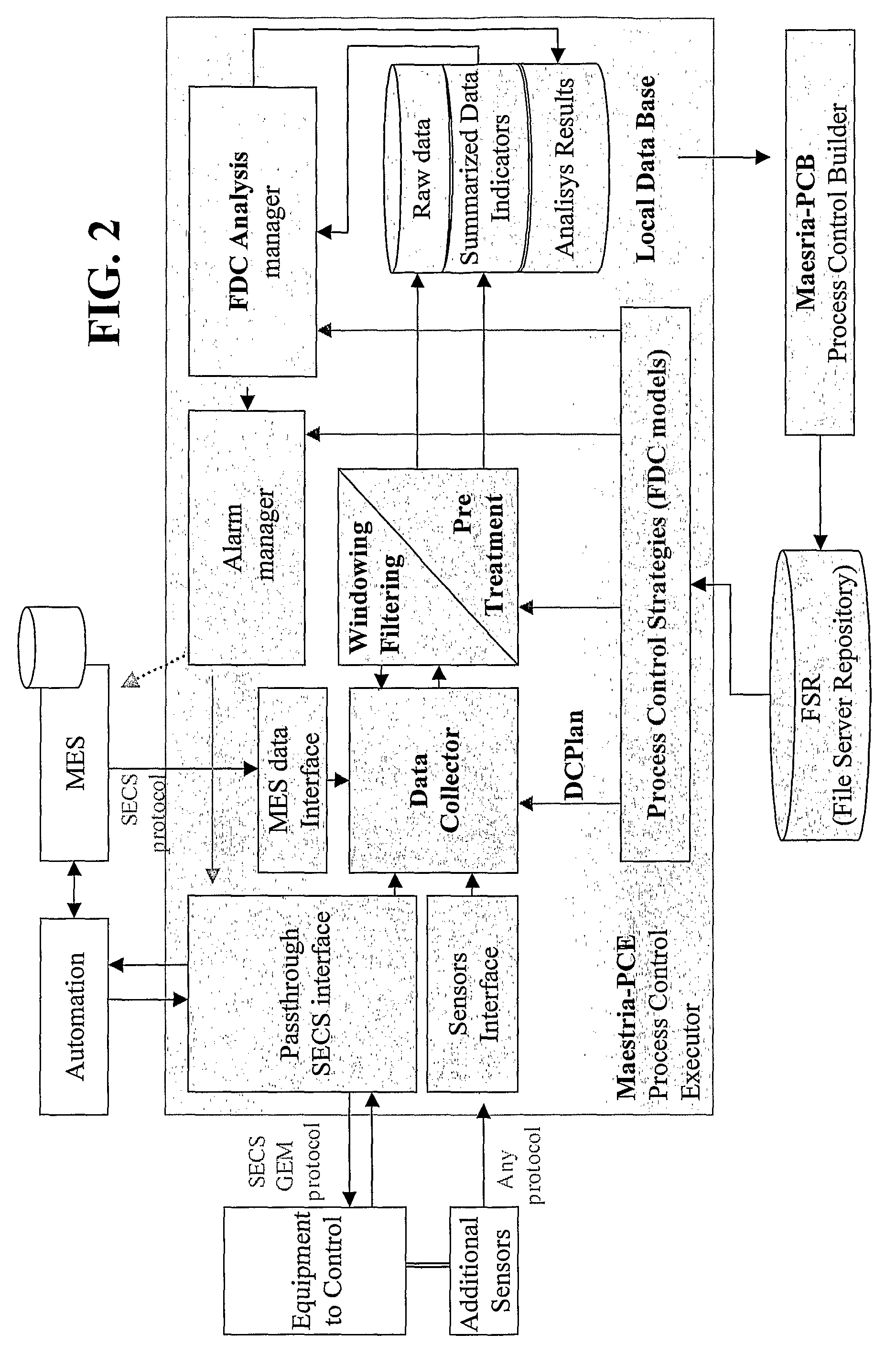

Method for evaluating the quality of data collection in a manufacturing environment

ActiveUS7529642B2Improve the level ofGood reproducibilitySampled-variable control systemsTesting/monitoring control systemsTimestampSemiconductor fab

Owner:PDF SOLUTIONS SA

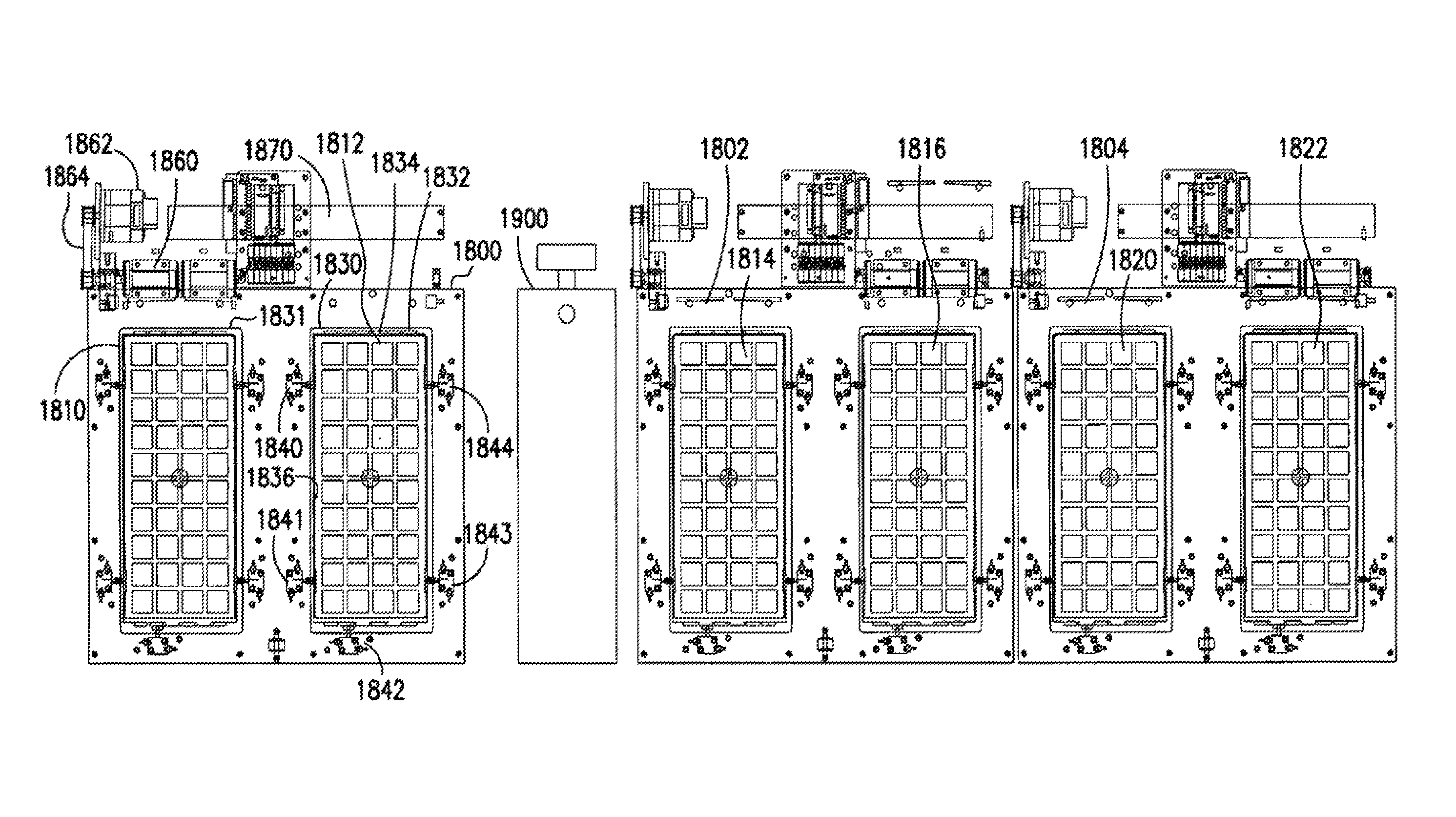

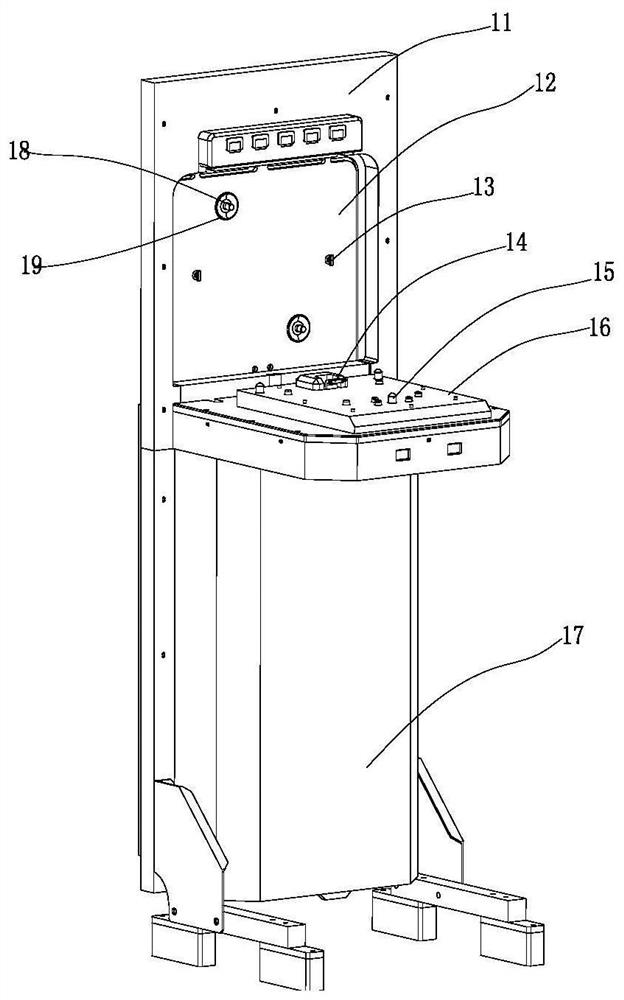

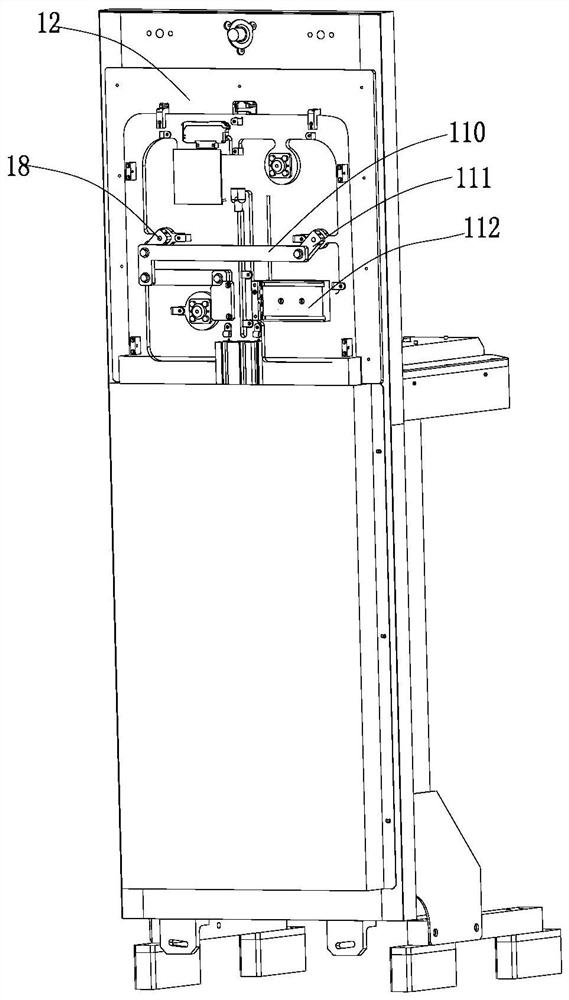

Tray flipper, tray, and method for parts inspection

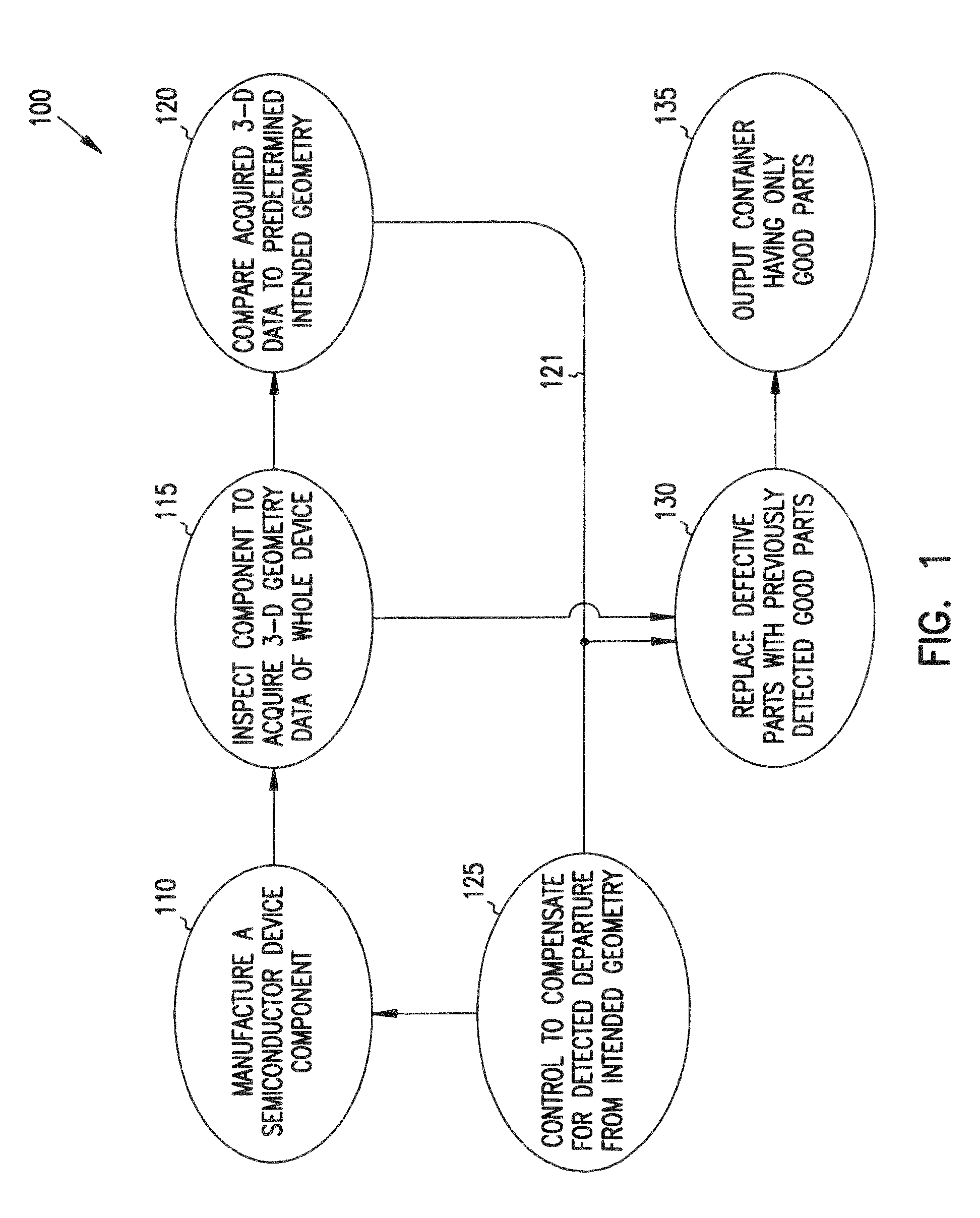

InactiveUS20090078620A1Facilitates automated high-speed three-dimensional inspectionConvenient to accommodateInvestigation of vegetal materialSeparation devicesSemiconductor fabEngineering

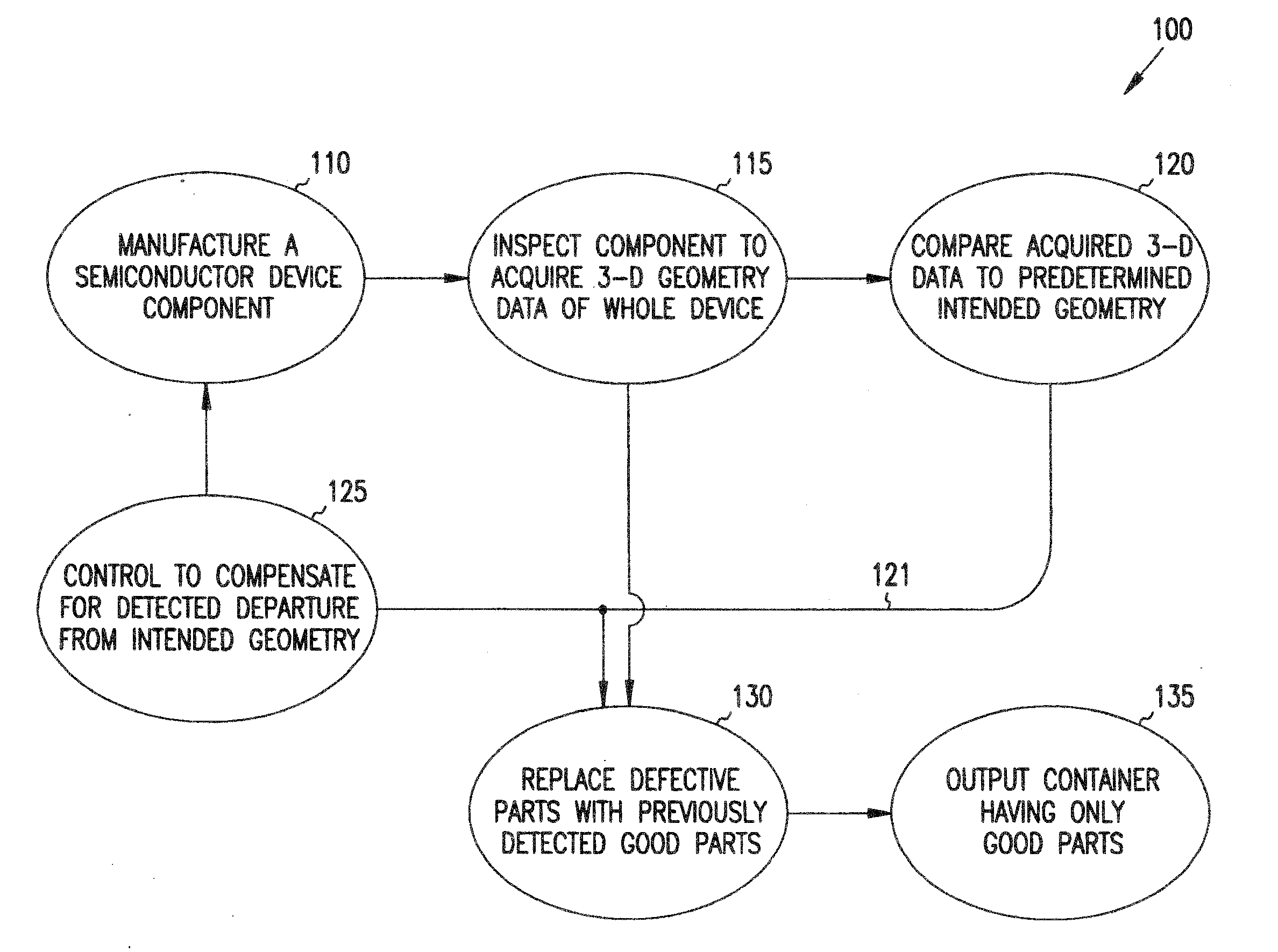

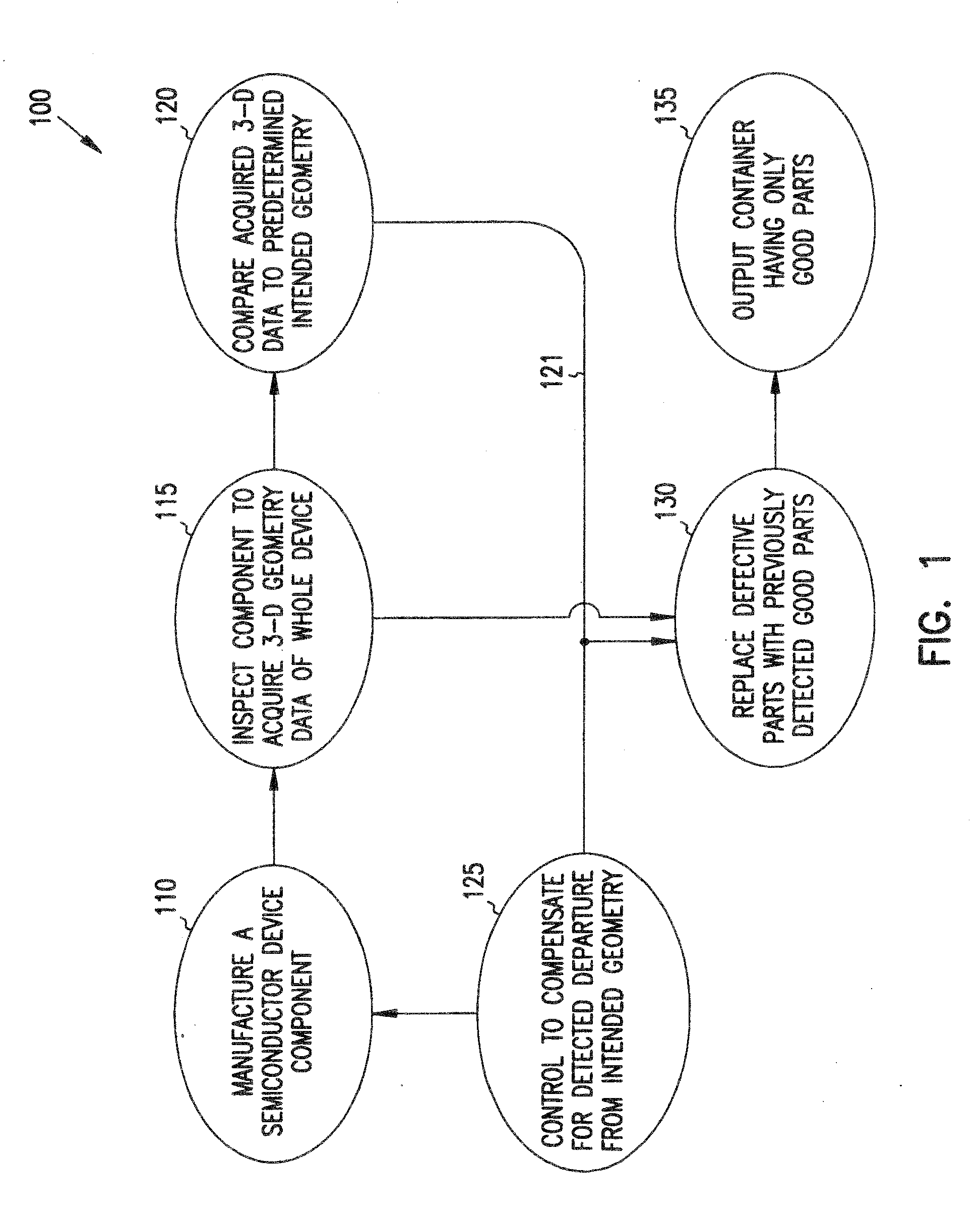

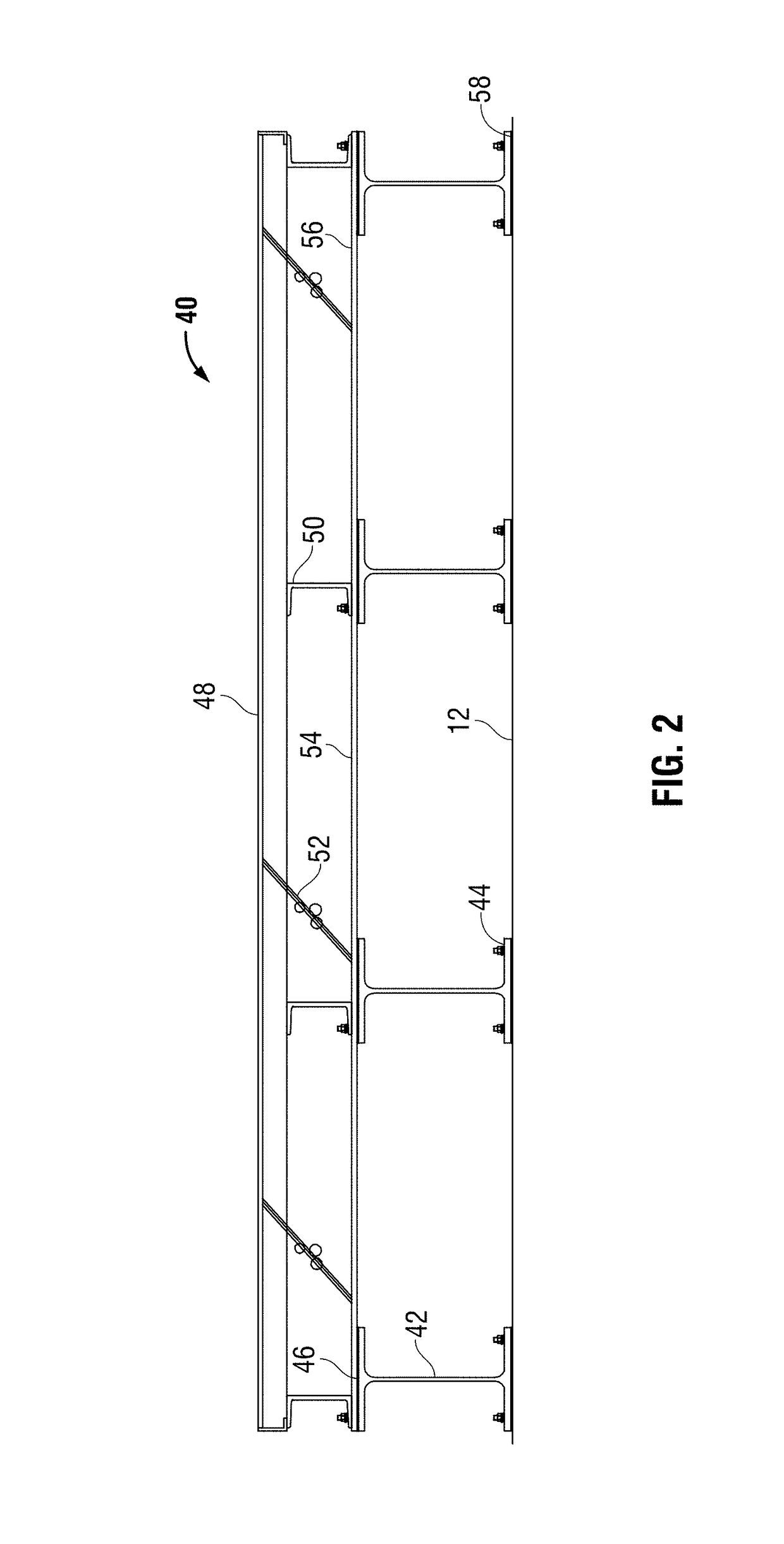

Manufacturing lines include inspection systems for monitoring the quality of parts produced. Manufacturing lines for making semiconductor devices generally inspect each fabricated part. The information obtained is used to fix manufacturing problems in the semiconductor fab plant. A machine-vision system for inspecting devices includes a flipper mechanism. After being inspected at a first station, a tray-transfer device moves the tray from the first inspection station to a flipper mechanism. The flipper mechanism includes two jaws, a mover, and a rotator. The flipper mechanism turns the devices over and places the devices in a second tray so that another surface of the device can be inspected. A second tray-transfer device moves the second tray from the flipper to a second inspection station. The mover of the flipper mechanism removes the tray from the first inspection surface and places a tray at the second inspection surface.

Owner:LEMAIRE CHARLES A

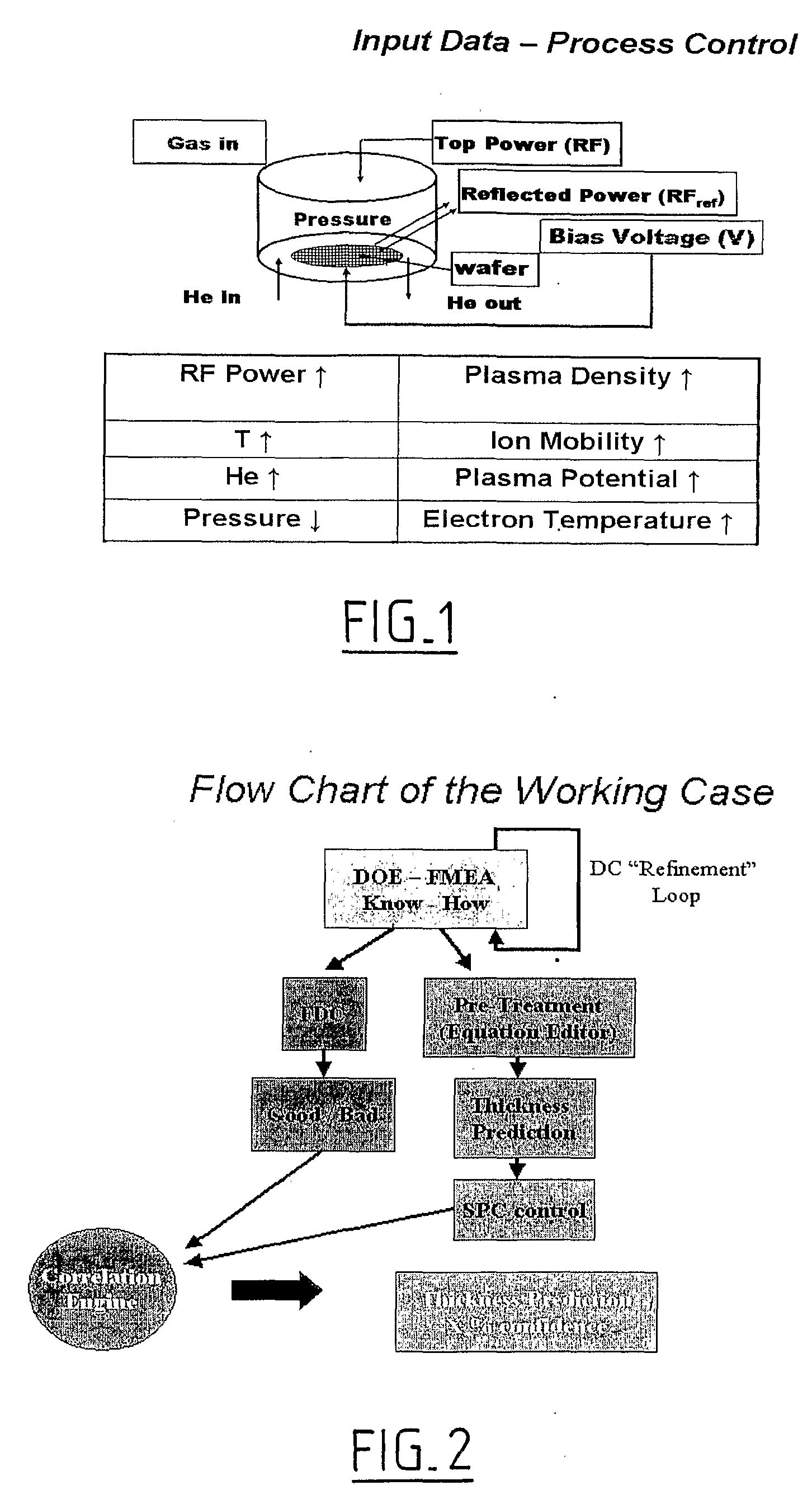

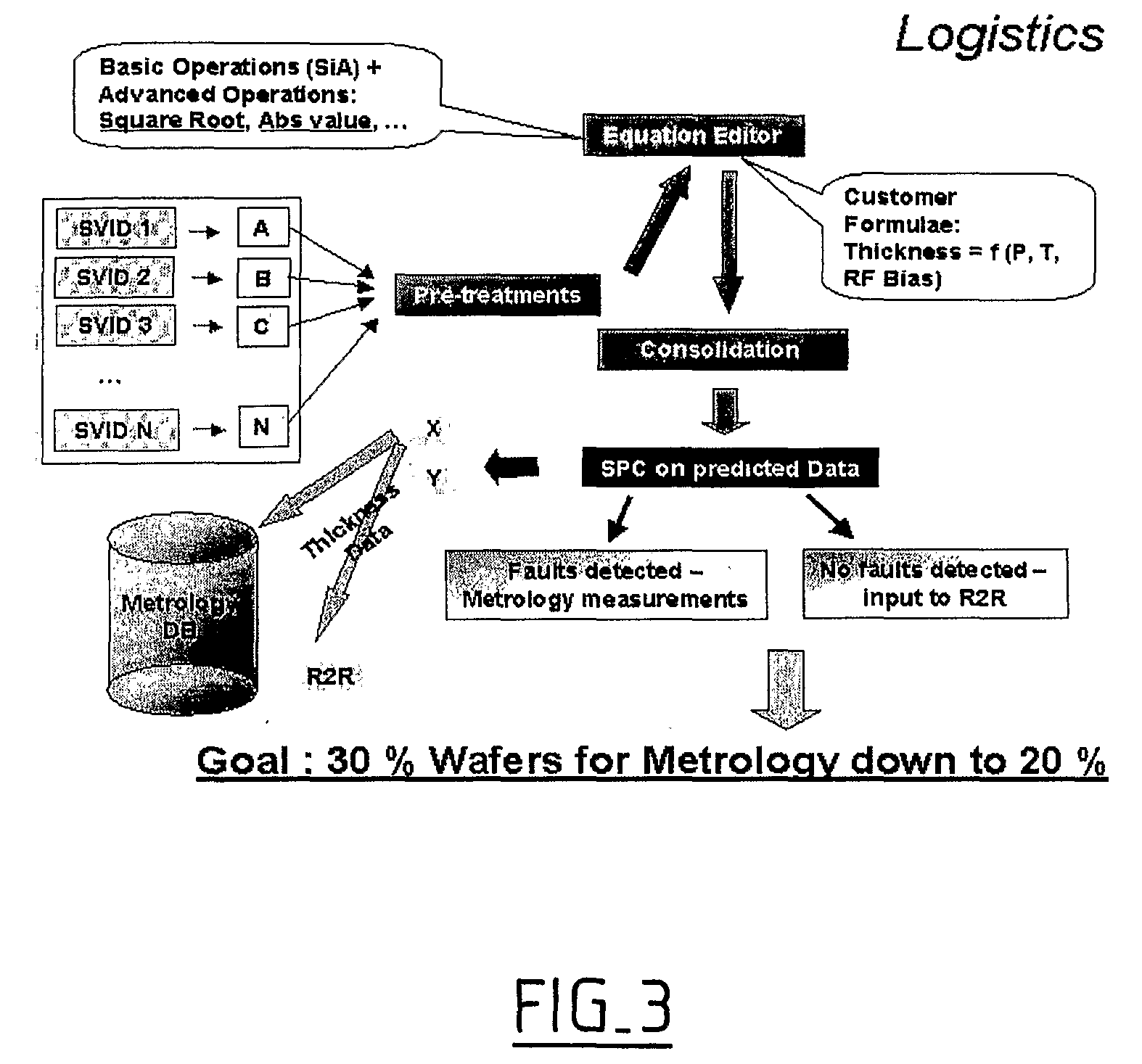

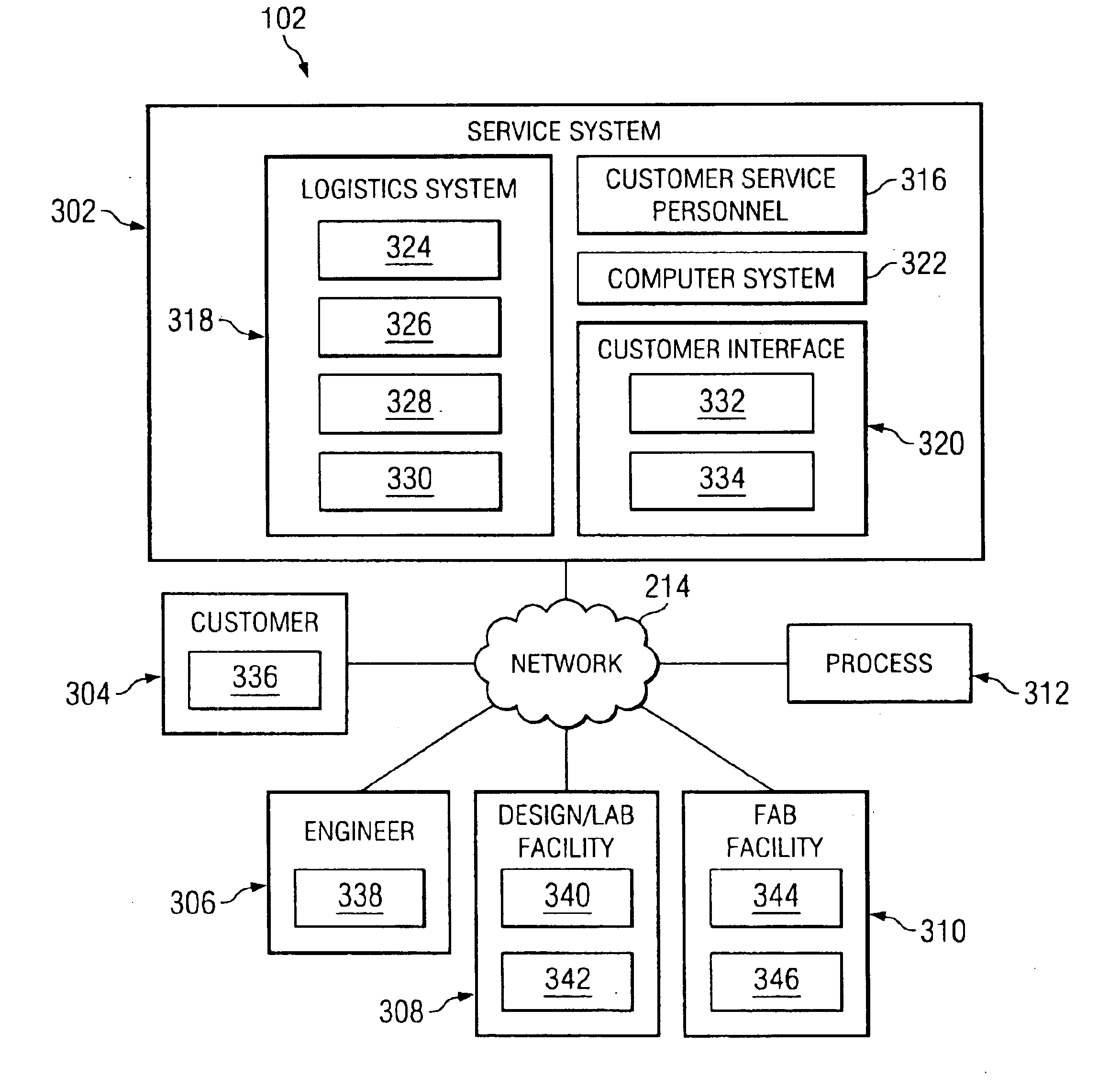

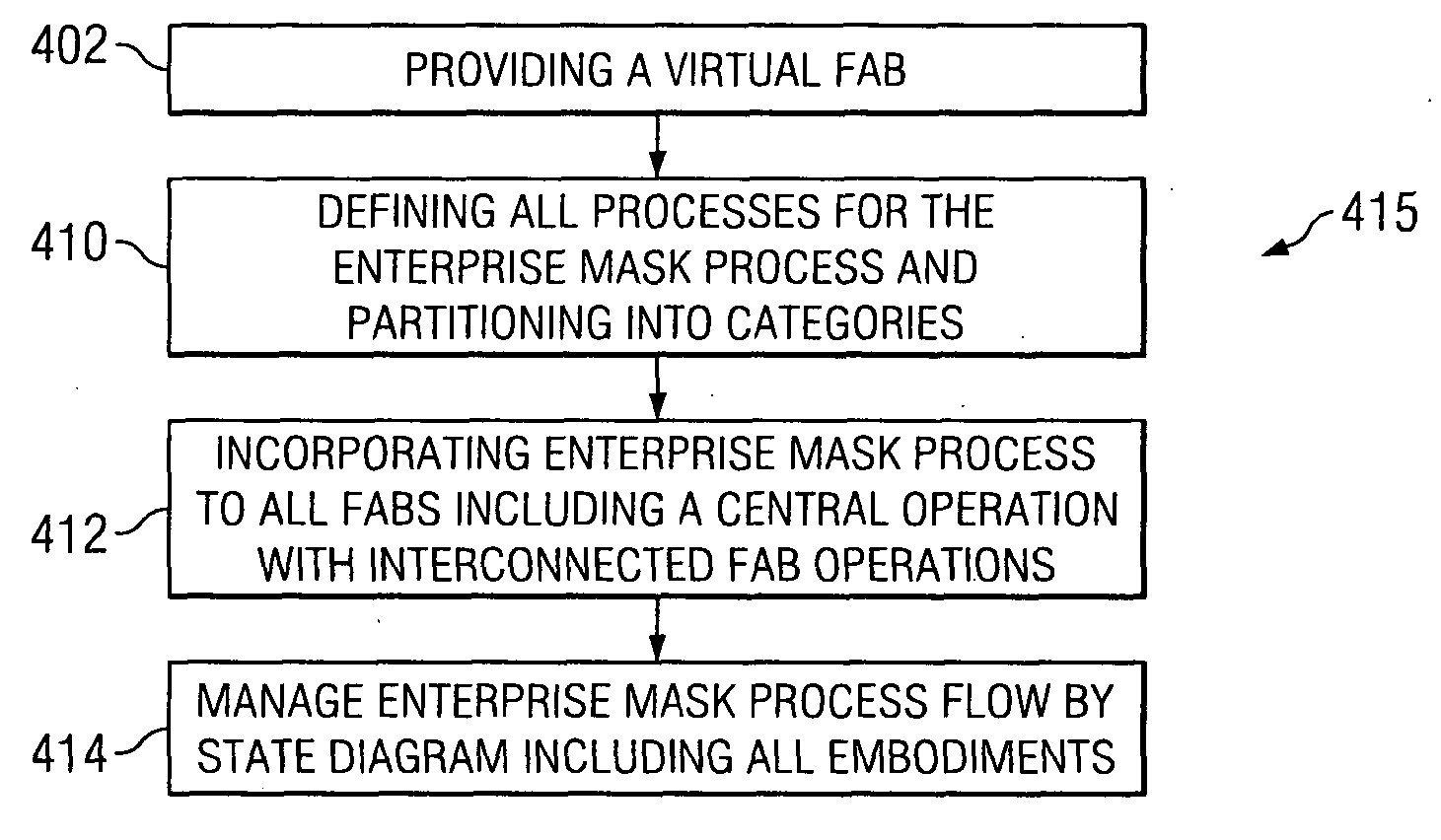

Method for Improving Efficiency of a Manufacturing Process Such as a Semiconductor Fab Process

InactiveUS20070260350A1Improve efficiencyTotal factory controlSpecial data processing applicationsManufacturing technologyControl system

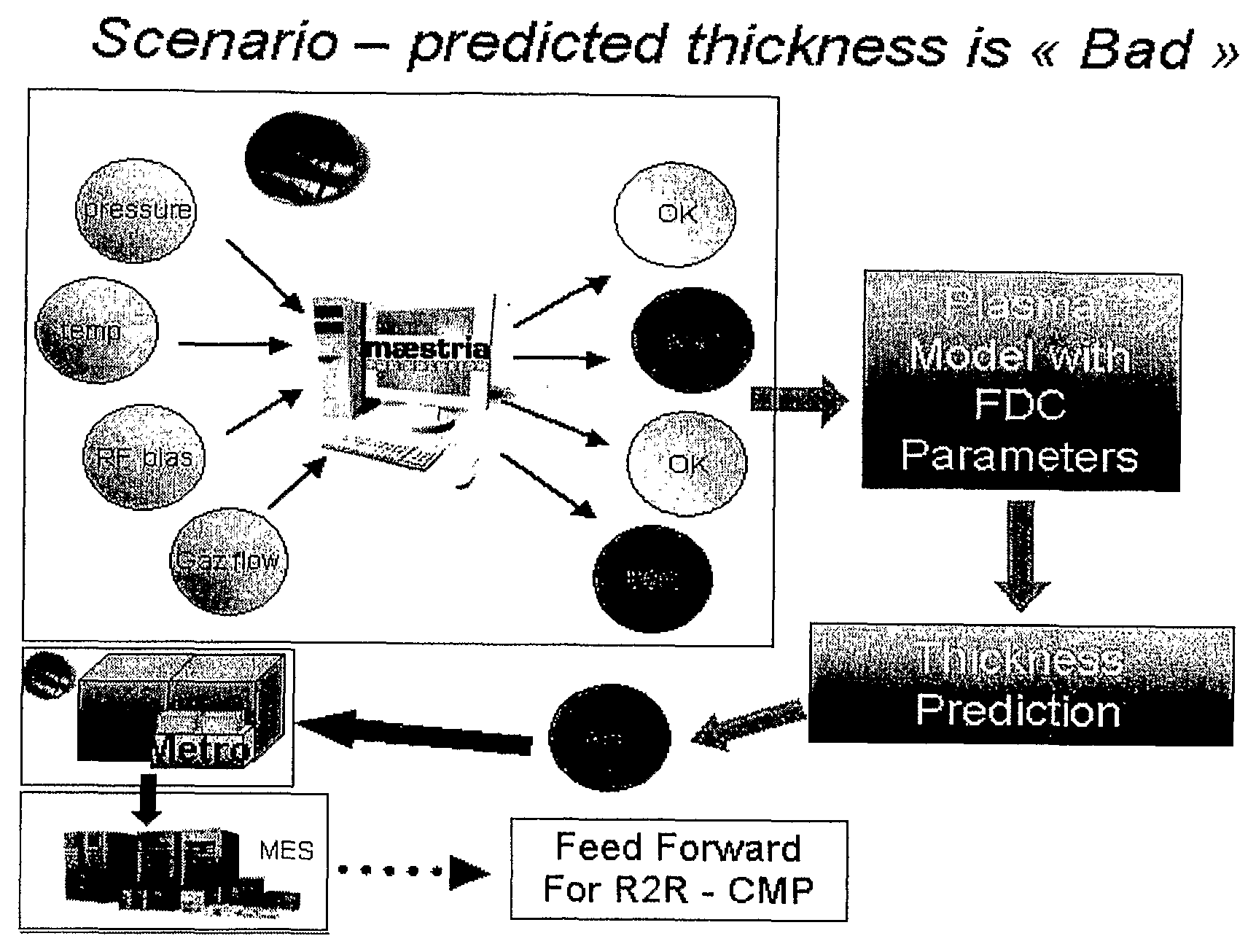

The present invention provides a method for improving the efficiency of a product manufacturing process such as a semiconductor fab process, wherein a given step of the process has a quality result which can be actually measured on each product or group of products, and wherein the process comprises a subsequent, adjustable step, the method comprising:—providing a correlation model of the behavior of said given step as a function of available parameters;—for each product or group of products at the output of said manufacturing step, computing a predicted quality result based on said correlation model as a function of the actual values of the parameters during the manufacturing step, and—providing the quality result to a control system for adjusting said subsequent step.

Owner:PDF SOLUTIONS SA

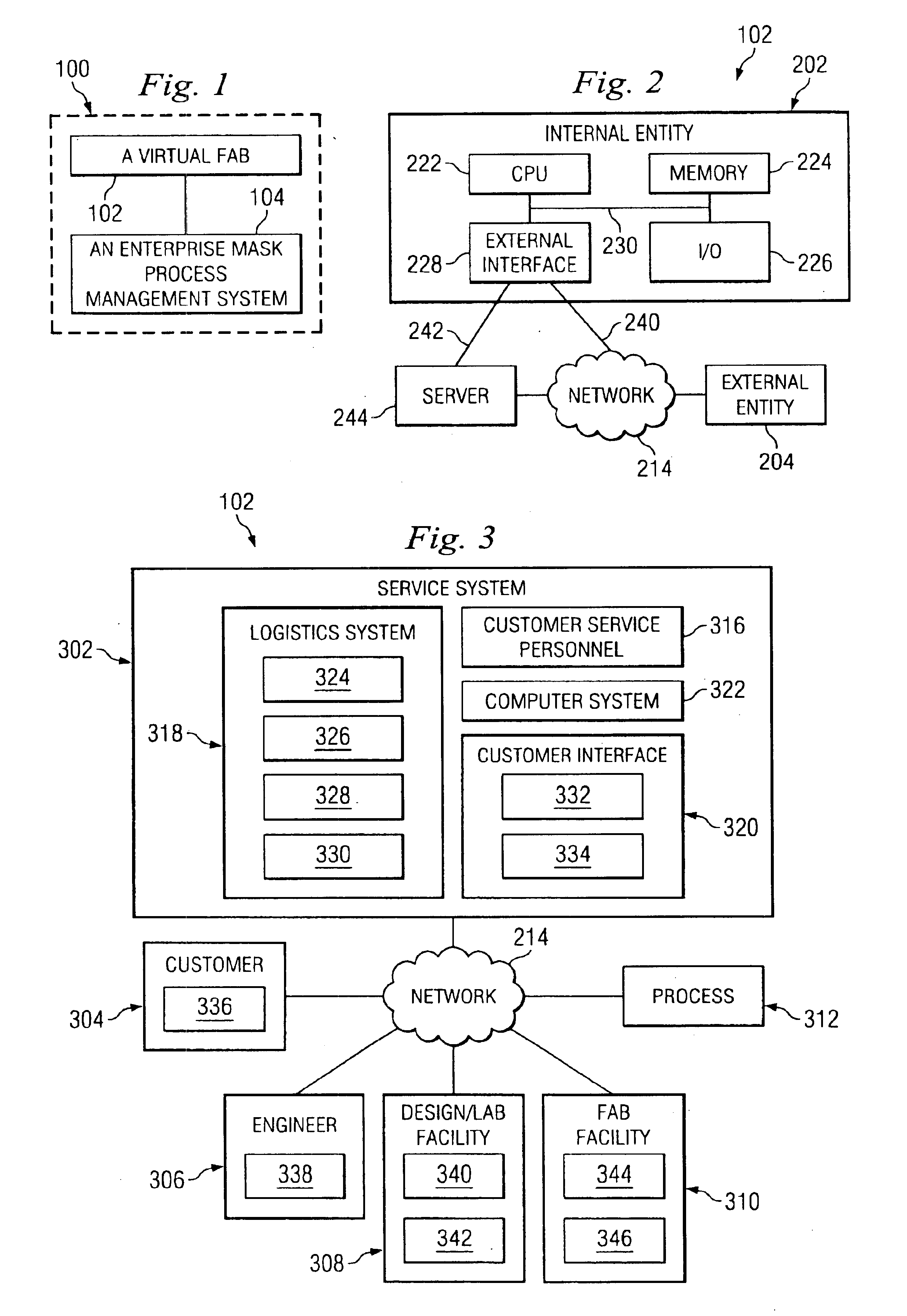

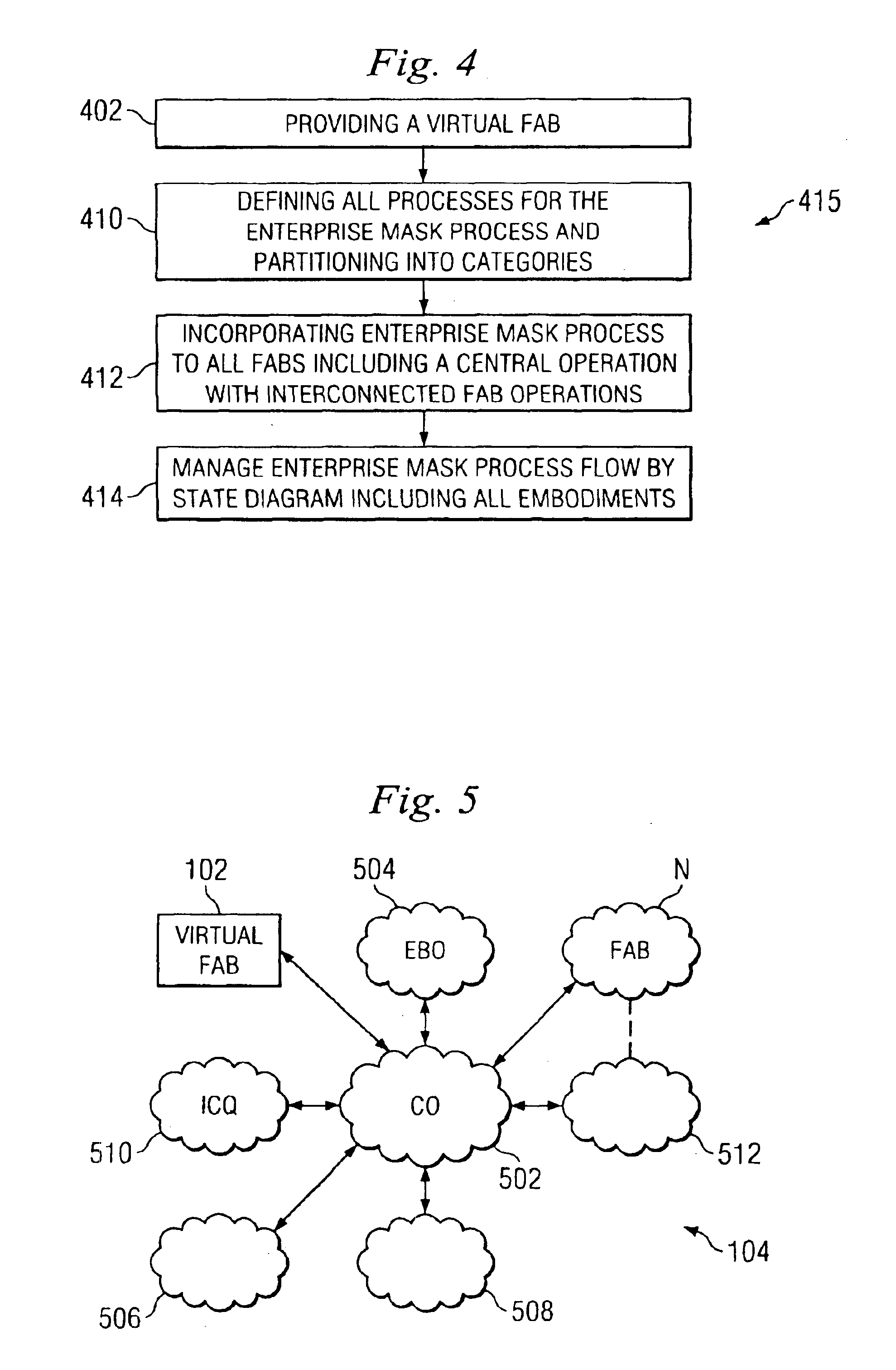

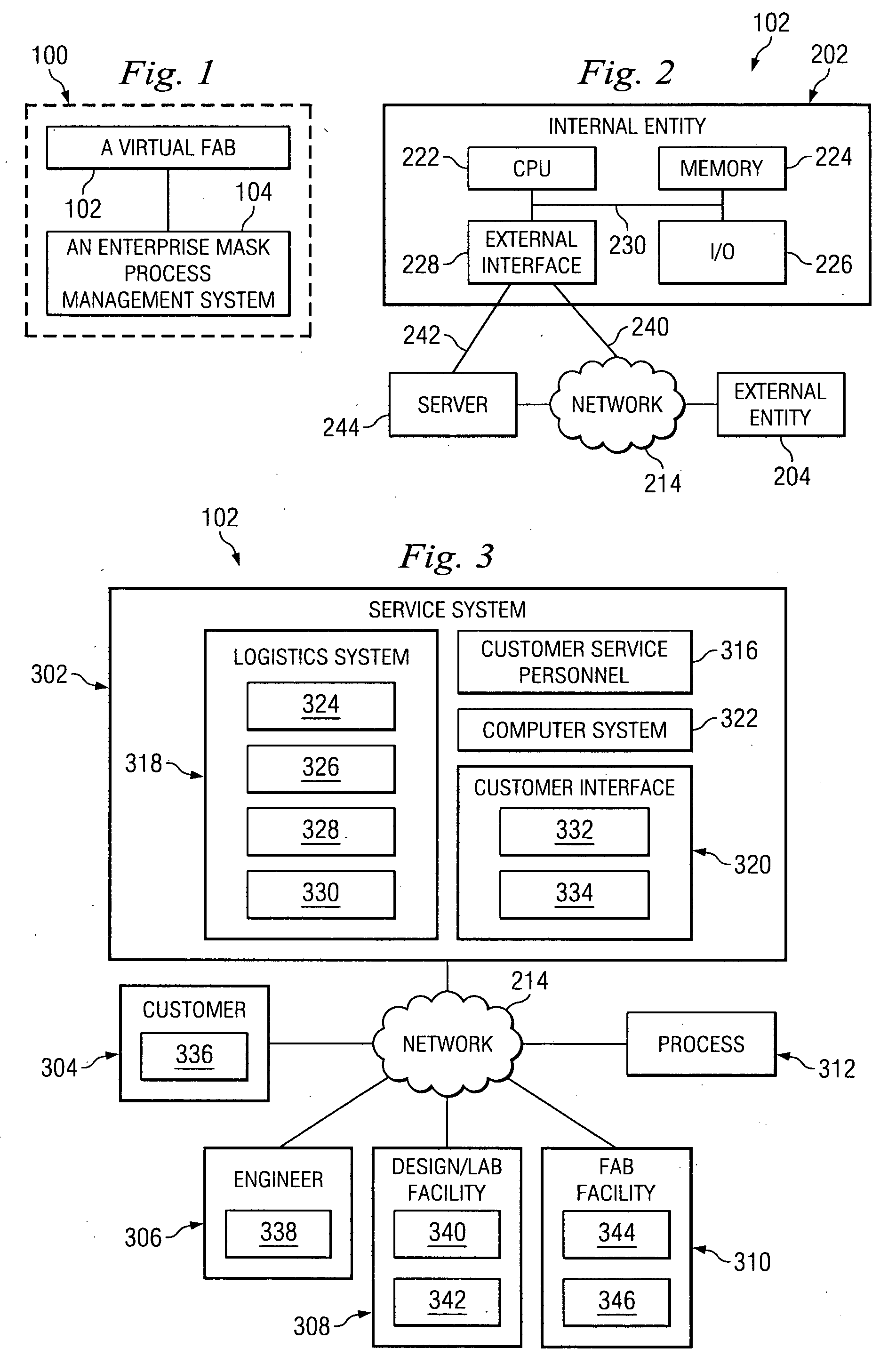

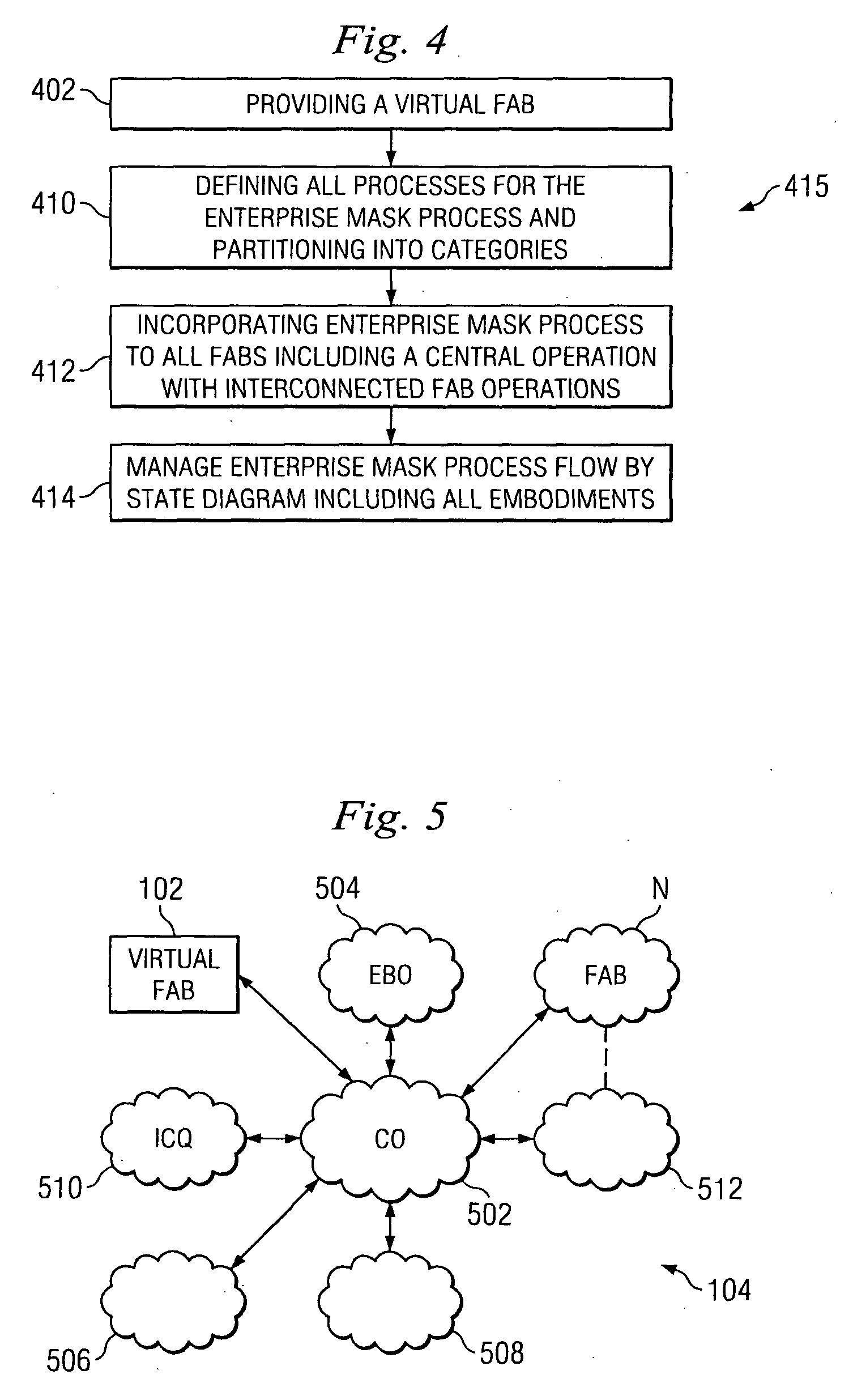

Mechanism for inter-fab mask process management

InactiveUS6928334B2Semiconductor/solid-state device manufacturingSpecial data processing applicationsVirtual plantSemiconductor fab

Owner:TAIWAN SEMICON MFG CO LTD

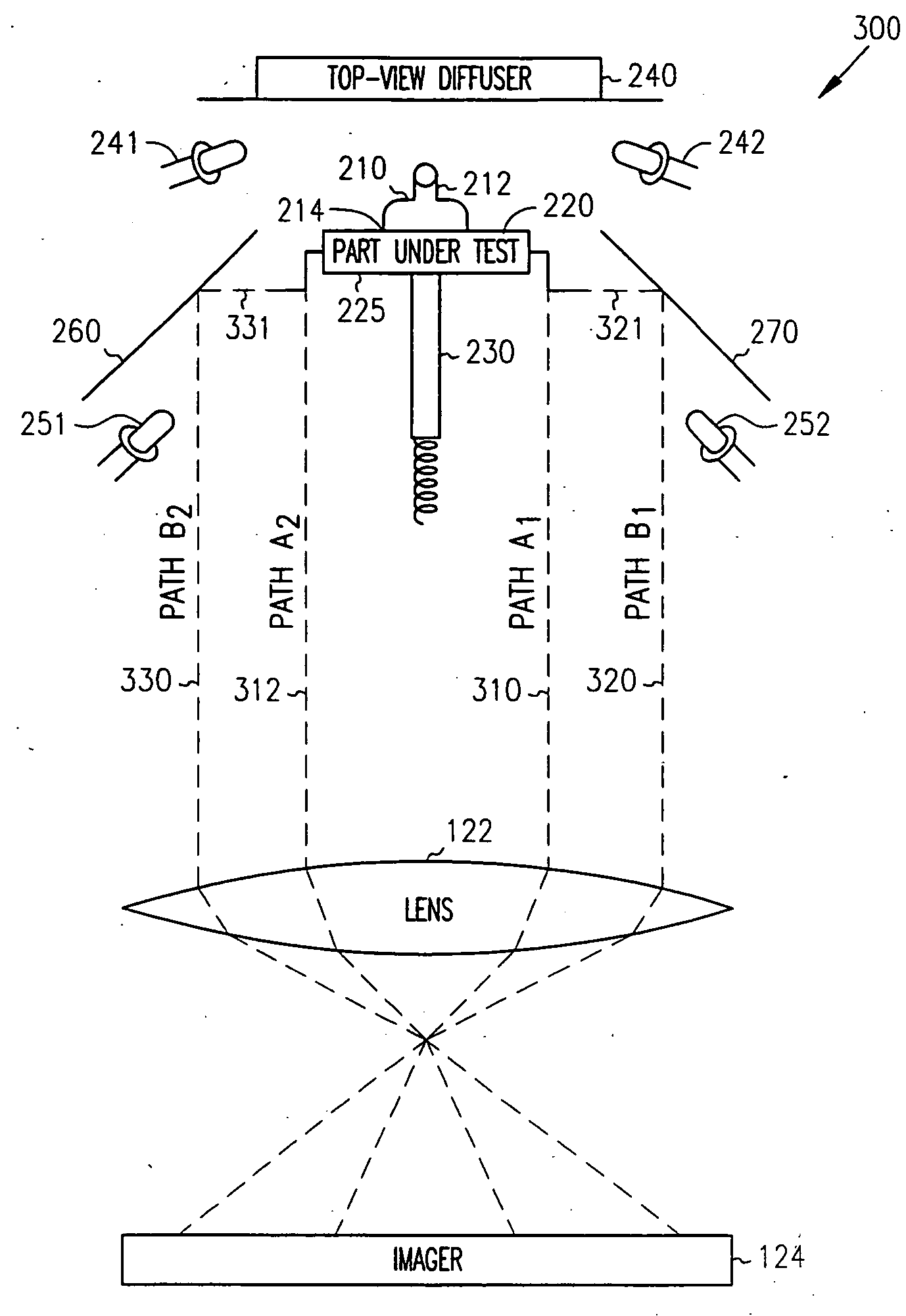

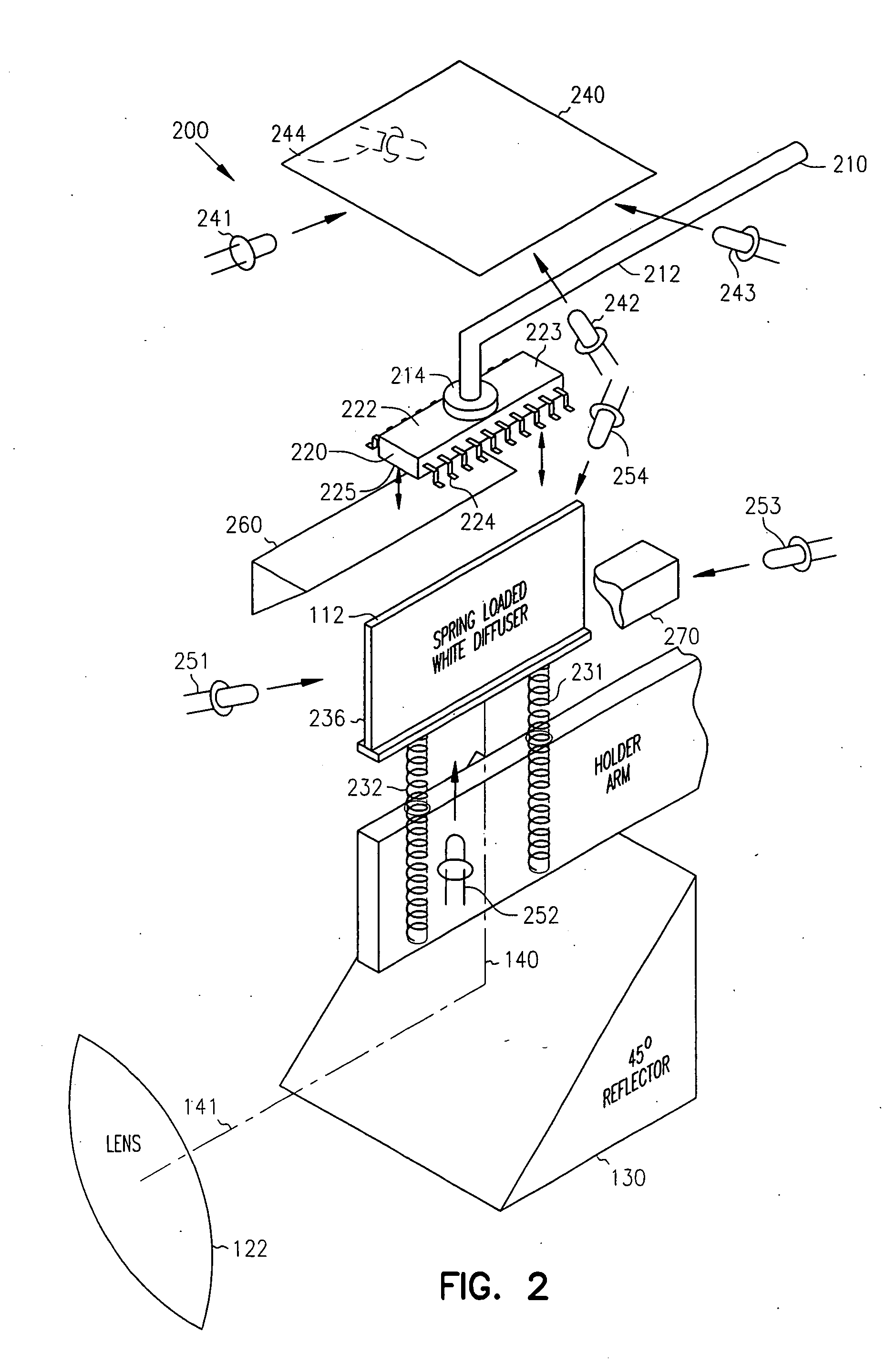

Method and apparatus for backlighting and imaging multiple views of isolated features of an object

InactiveUS20060152741A1Minimize and substantially eliminate problemAccurate measurementMaterial analysis by optical meansUsing optical meansDevice materialEngineering

Owner:LEMAIRE CHARLES A

Mechanism for inter-fab mask process management

InactiveUS20050021165A1Semiconductor/solid-state device manufacturingSpecial data processing applicationsVirtual plantEngineering

A software mechanism is provided for inter-fab mask process management. The mechanism is used for tracking and managing a plurality of lithographic masks through a semiconductor manufacturing environment. A virtual fab is established with a plurality of entities, each entity associated with an internal process to a semiconductor fab or an external process to the semiconductor fab. A state diagram tracks the plurality of lithographic masks through the plurality of entities of the virtual fab. Each of the plurality of lithographic masks is placed at a pre-determined state of the state diagram and a future location for each of the masks in the virtual fab is determined via the state diagram.

Owner:TAIWAN SEMICON MFG CO LTD

Tray flipper, tray, and method for parts inspection

InactiveUS8056700B2Facilitates automated high-speed three-dimensional inspectionConvenient to accommodateInvestigation of vegetal materialSeparation devicesSemiconductor fabManufacturing line

Manufacturing lines include inspection systems for monitoring the quality of parts produced. Manufacturing lines for making semiconductor devices generally inspect each fabricated part. The information obtained is used to fix manufacturing problems in the semiconductor fab plant. A machine-vision system for inspecting devices includes a flipper mechanism. After being inspected at a first station, a tray-transfer device moves the tray from the first inspection station to a flipper mechanism. The flipper mechanism includes two jaws, a mover, and a rotator. The flipper mechanism turns the devices over and places the devices in a second tray so that another surface of the device can be inspected. A second tray-transfer device moves the second tray from the flipper to a second inspection station. The mover of the flipper mechanism removes the tray from the first inspection surface and places a tray at the second inspection surface.

Owner:LEMAIRE CHARLES A

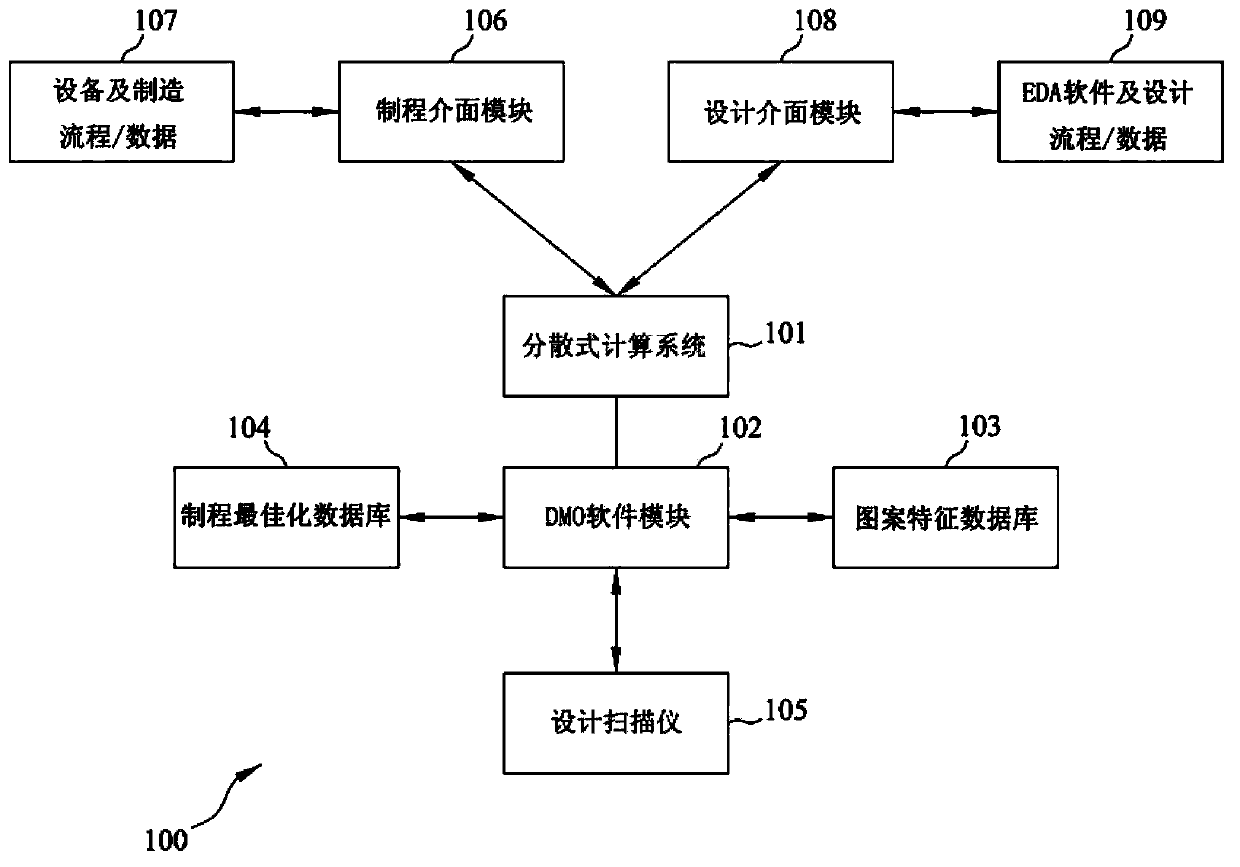

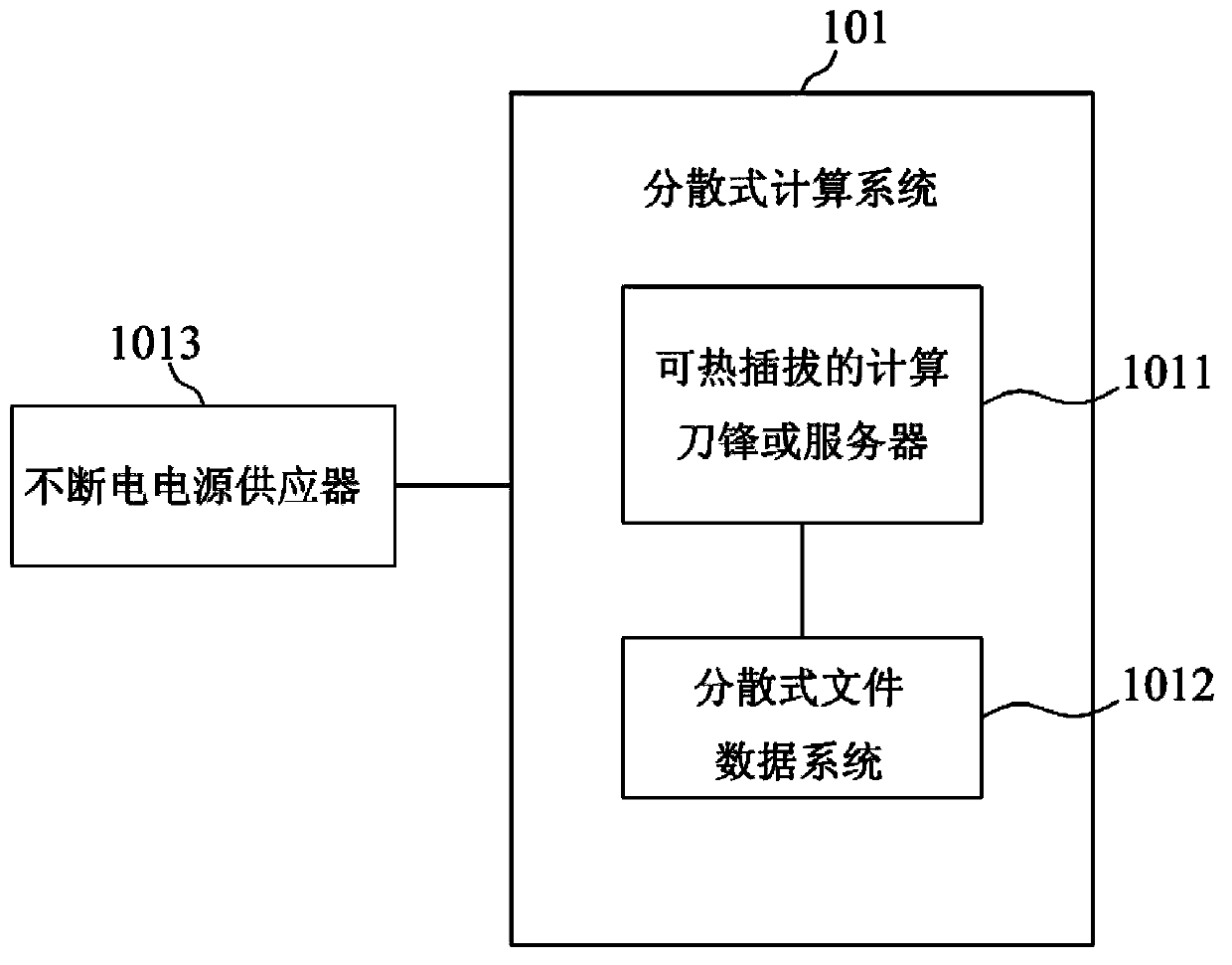

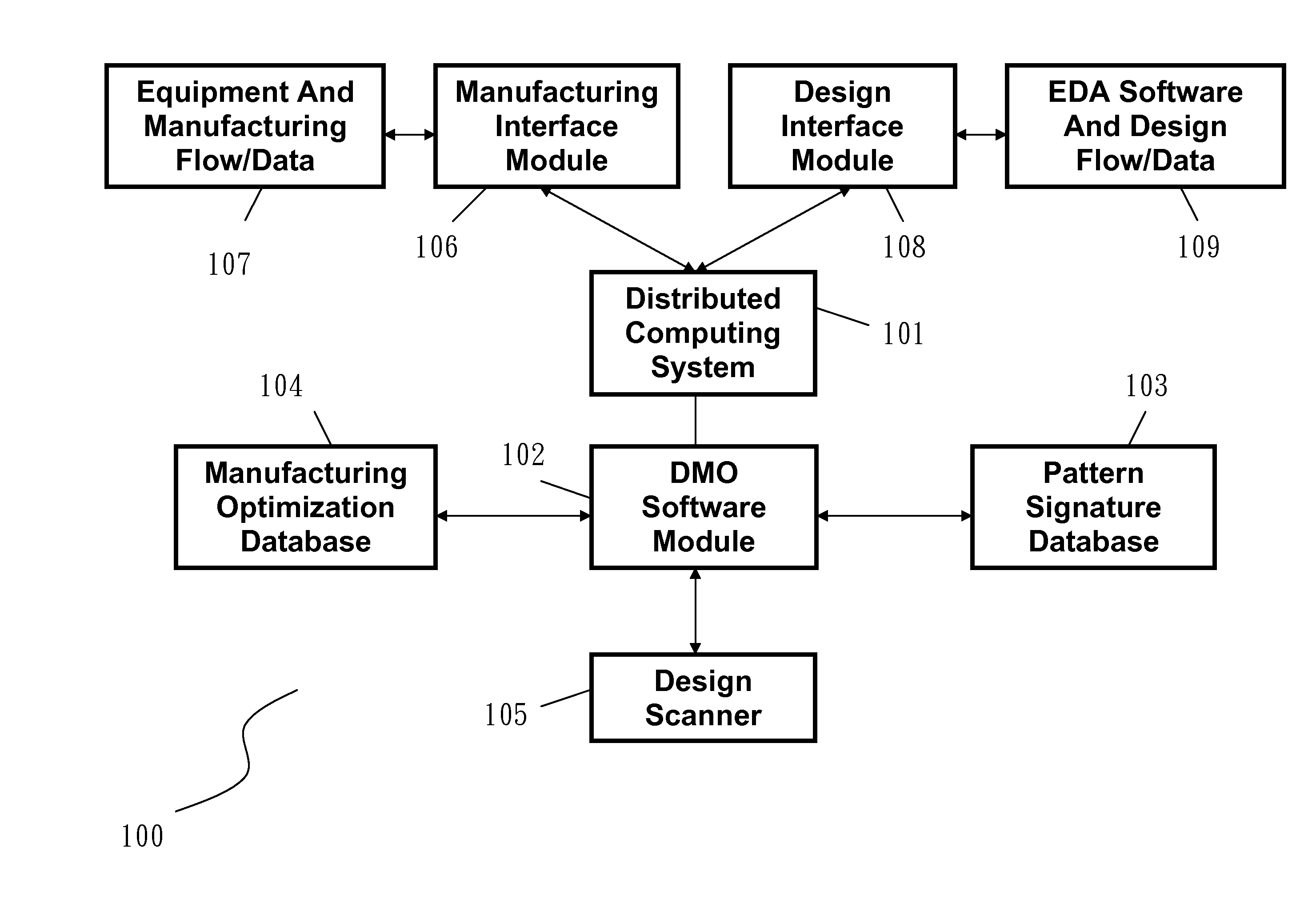

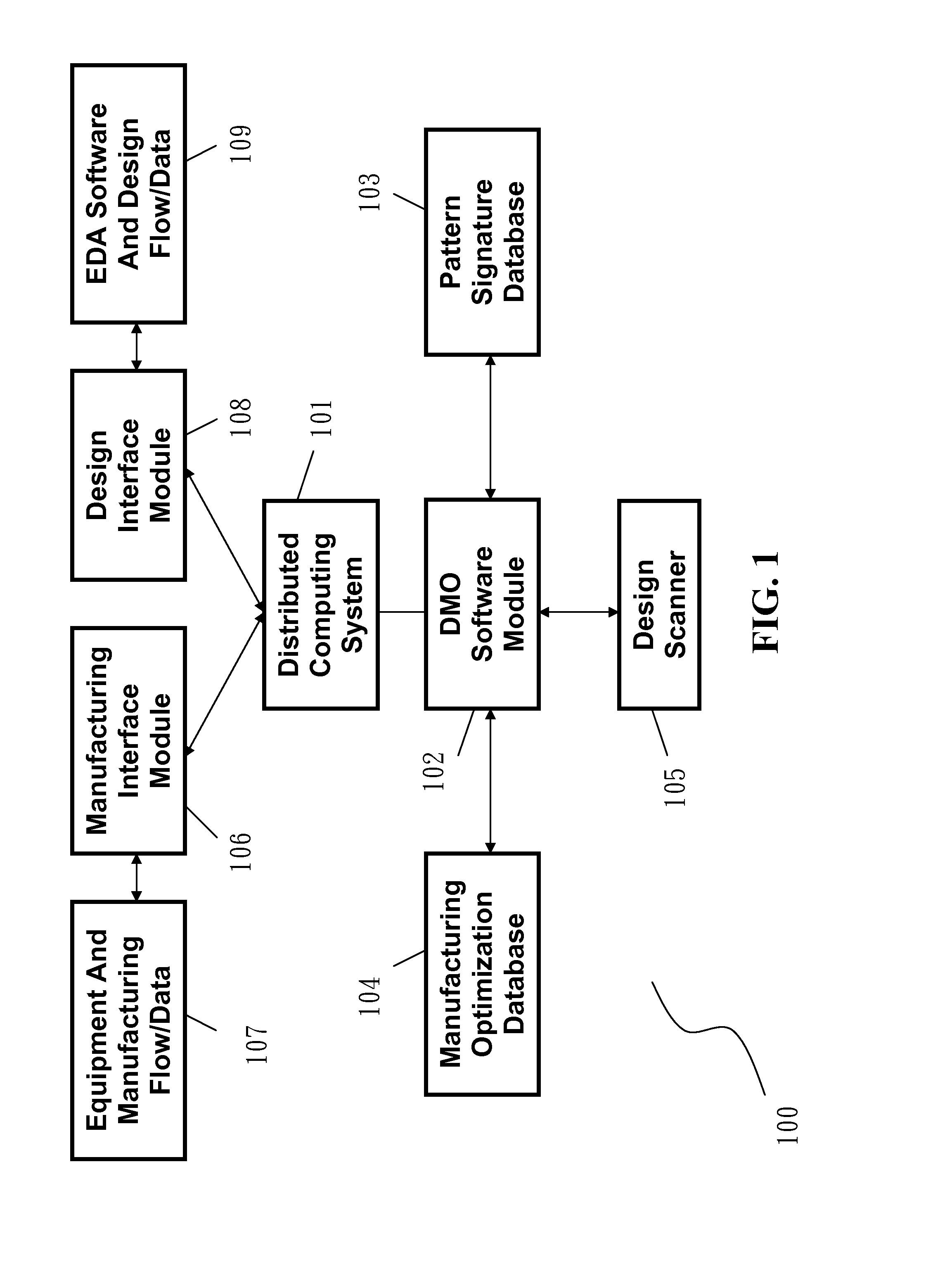

Apparatus For Design-based Manufacturing Optimization In Semiconductor Fab

InactiveCN103970922ASemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor fab

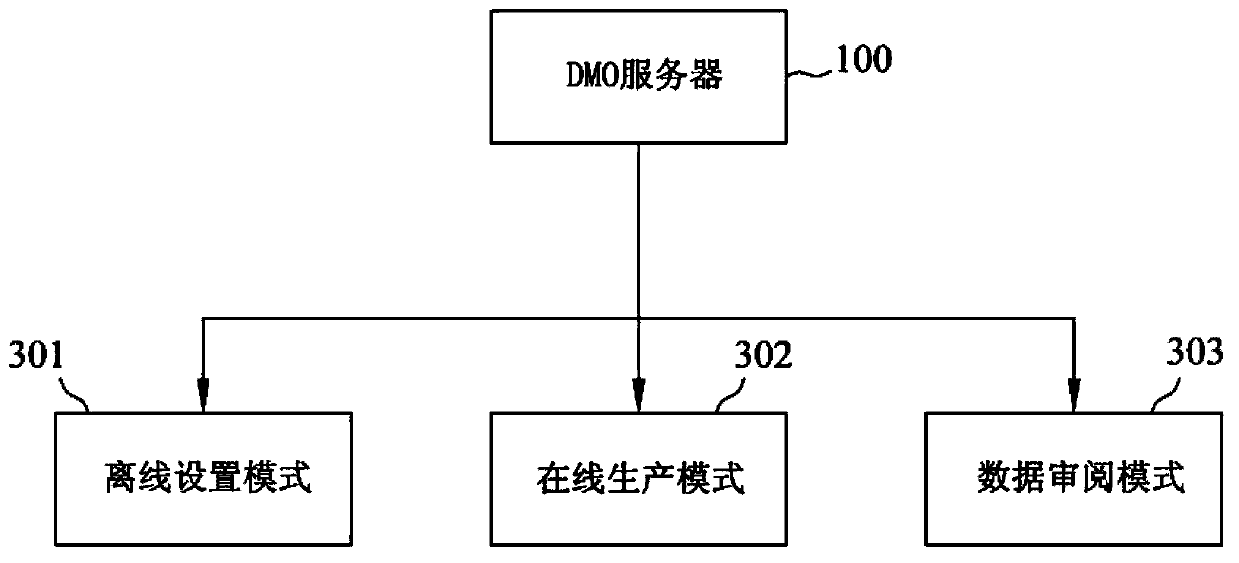

A design-based manufacturing optimization (DMO) server comprises a distributed computing system and a DMO software module incorporating with a design scanner to scan and analyze design data of a semiconductor device for optimizing manufacturing of the semiconductor device. The DMO software module sets up a pattern signature database and a manufacturing optimization database, generates design-based manufacturing recipes, interfaces with manufacturing equipment through a manufacturing interface module, and interfaces with electronic design automation suppliers for the design data through a design interface module. The DMO server executes the design-based manufacturing recipes for manufacturing optimization.

Owner:DMO SYST

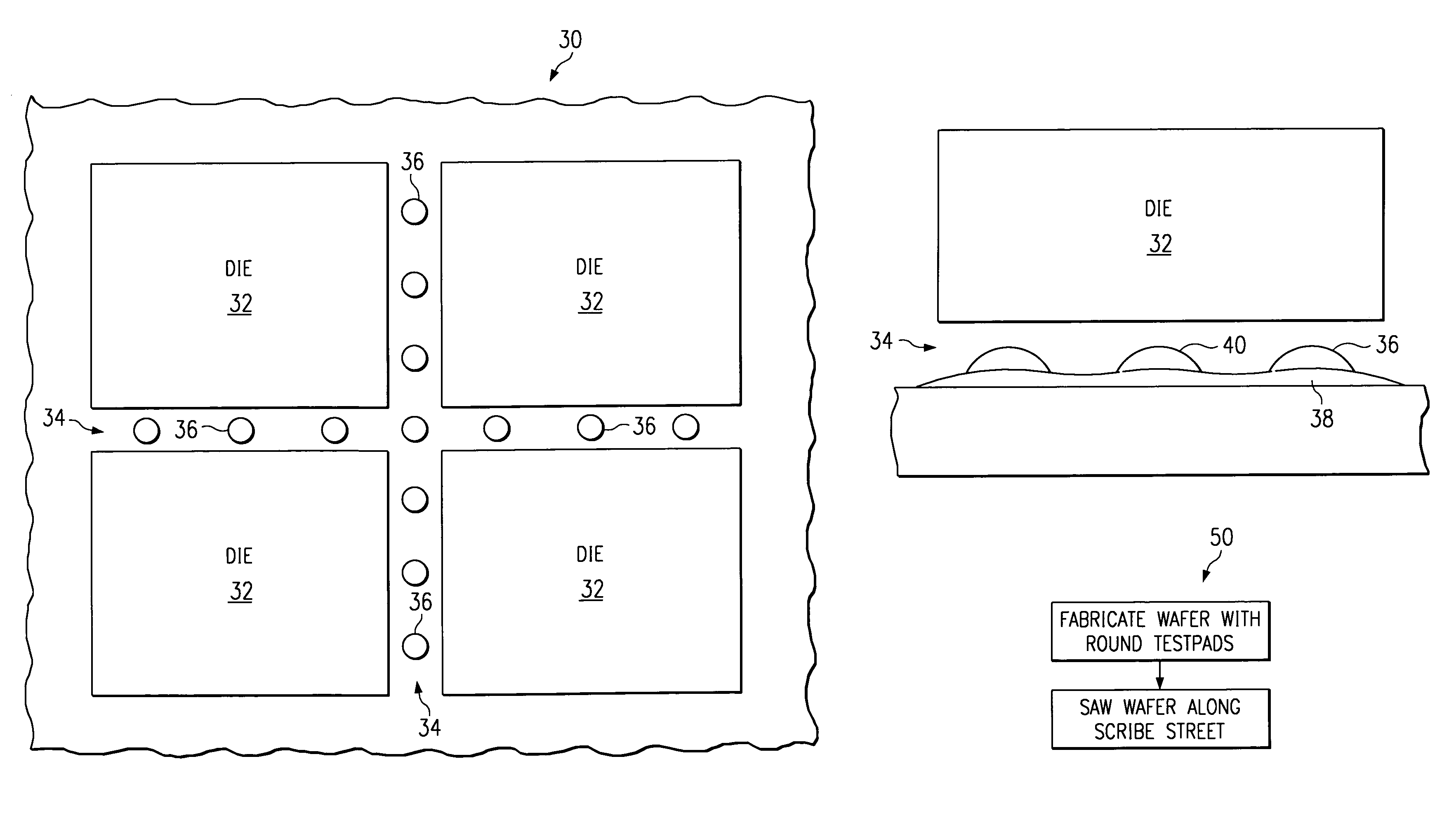

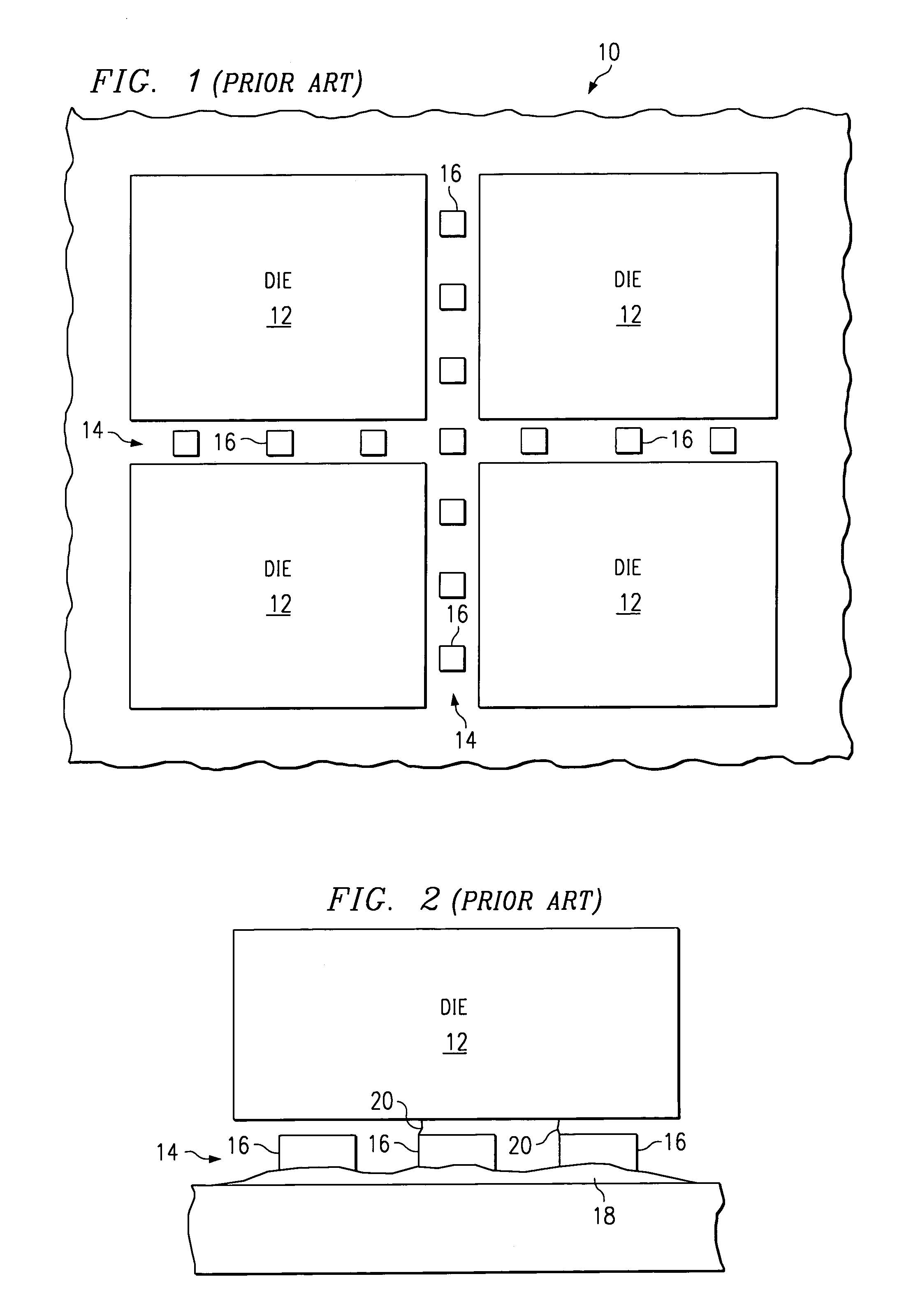

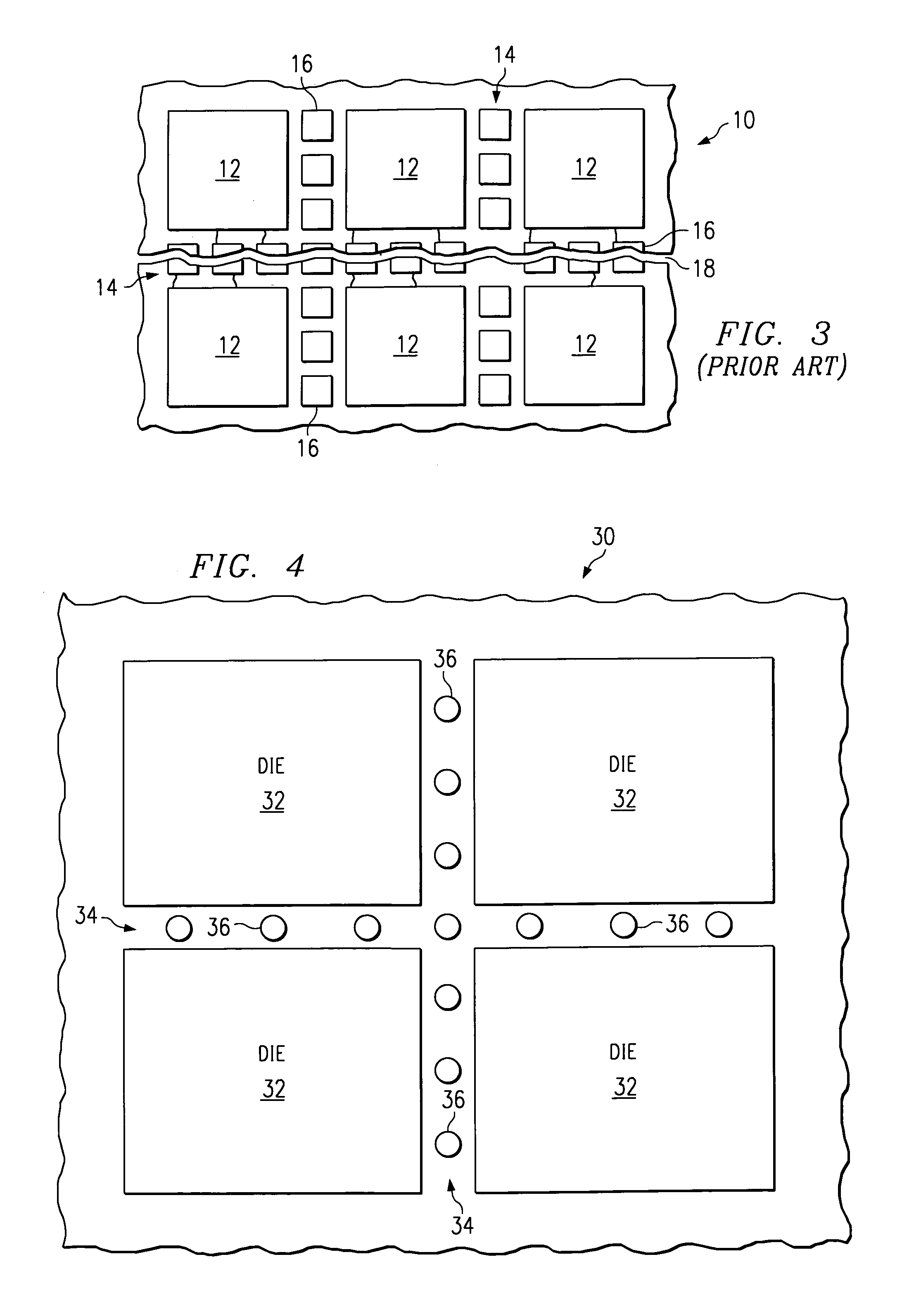

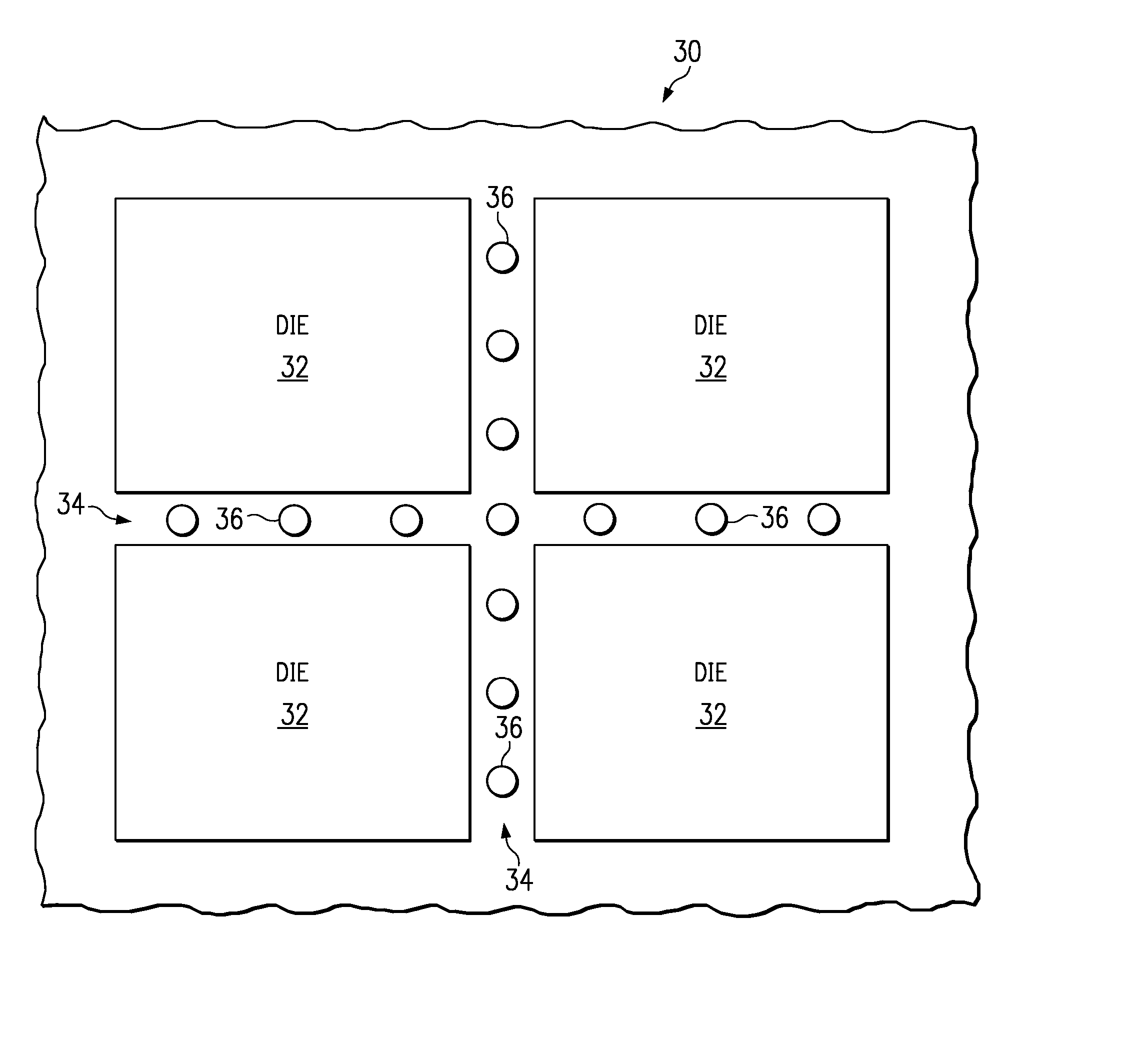

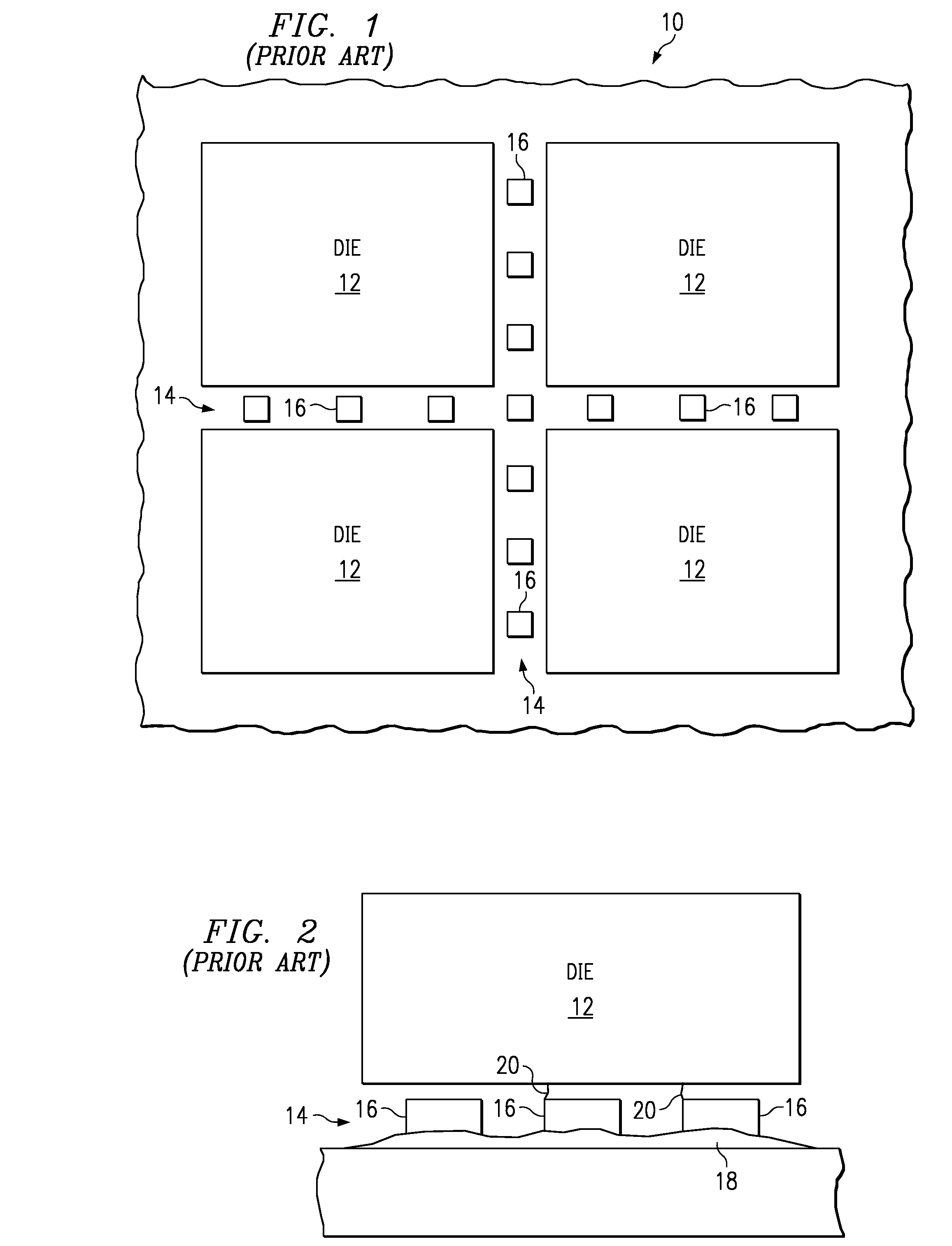

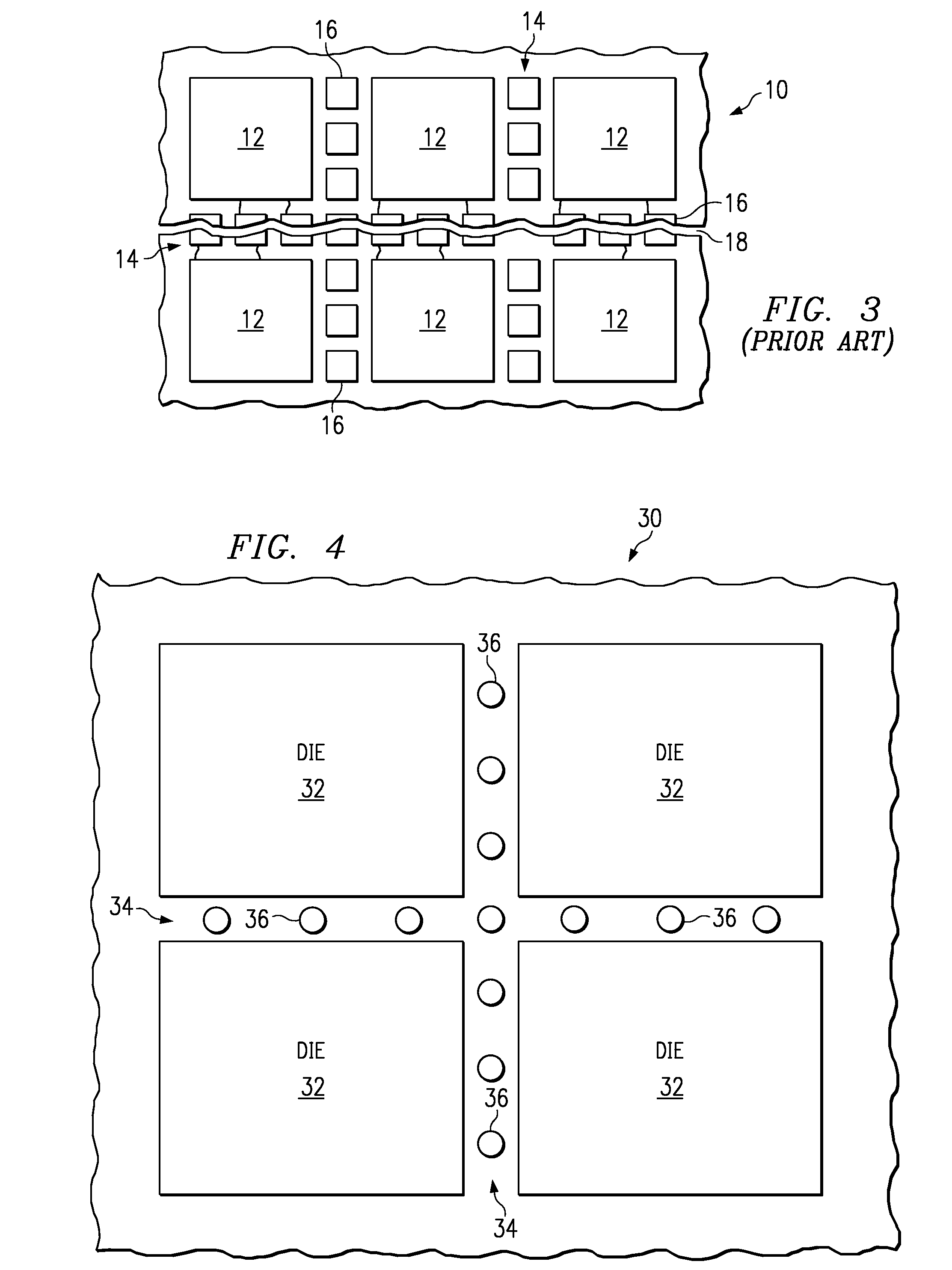

Circular test pads on scribe street area

InactiveUS7259043B2Improve Wafer YieldReduce yield lossSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor fabReticle

A semiconductor wafer design and process having test pads (36) reducing cracks generated during the wafer saw process from extending into and damaging adjacent die. The present invention provides a plurality of circular test pads (36) in a wafer scribe street (34) such that any cracks generated in the test pad during wafer saw self terminate in the periphery of the circular test pad. By providing a curved test pad periphery, cracks will tend to propagate along the edges of the test pads and self terminate therein. The circular test pads avoid any sharp corners as is conventional in rectangular test pads which tend to facilitate the extension of cracks from corners to extend into the adjacent wafer die (32). The present invention utilizes existing semiconductor fab processing and utilizes new reticle sets to define the curved test pads.

Owner:TEXAS INSTR INC

Method for controlling doping density of doped region of semiconductor device accurately

ActiveCN102254801APrecise control of concentrationSimple and fast operationSemiconductor/solid-state device manufacturingSemiconductor fabSilicon dioxide

The invention provides a method for controlling the doping density of a doped region of a semiconductor device accurately. In the method, a silicon wafer is oxidized; a photoresist is added to a boron emulsion source in the coating process; and the boron emulsion source is mixed with the photoresist, and the mixture is placed in a stirring vessel for sufficient stirring so as to obtain an emulsion source coating liquid, wherein the photoresist is carbonized at a high temperature to so as to remove gases carried in the diffusion process, thus obtaining the required impurity density distribution in a boron region. The method is easy and convenient to operate, simple in equipment and is suitable for massive production. The diffusion parameters of the method can be controlled and adjusted freely; the doping density is adjustable; a silica oxidation layer is formed on the silicon wafer by diffusible oxidation; the thickness accuracy in oxidization is controlled so as to reach the density for controlling diffusion impurities accurately; the technological process is simplified; the production cost is reduced; and the yield of the semiconductors is improved by over 20%. The method is particularly suitable for low and medium-grade semiconductor manufacturers to produce the semiconductors massively; and the method has the advantage of remarkable economic benefit.

Owner:JILIN SINO MICROELECTRONICS CO LTD

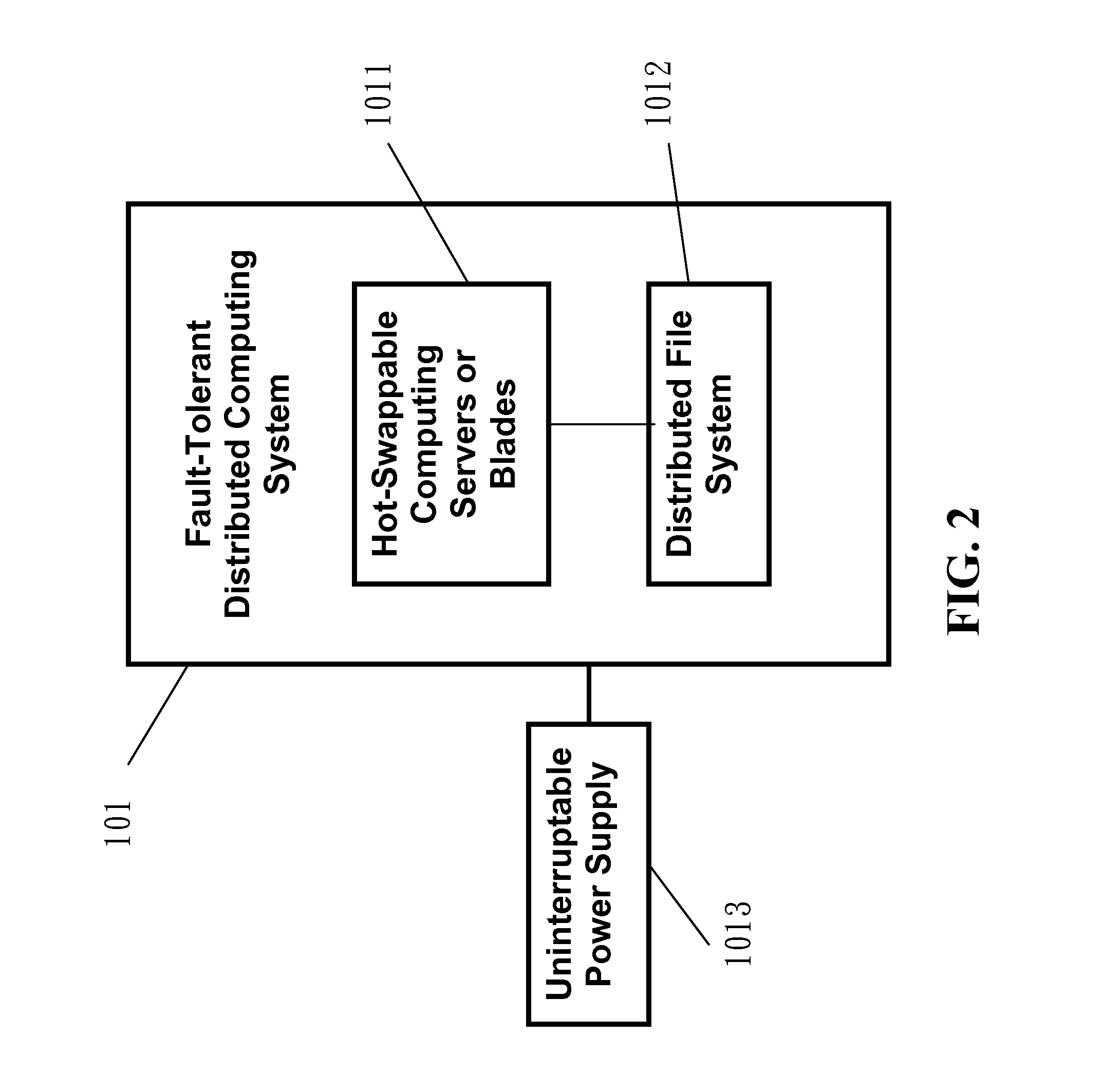

Apparatus For Design-Based Manufacturing Optimization In Semiconductor Fab

InactiveUS20140214192A1Improve scalabilityHighly secureSemiconductor/solid-state device testing/measurementResourcesSemiconductor fabComputing systems

A design-based manufacturing optimization (DMO) server comprises a distributed computing system and a DMO software module incorporating with a design scanner to scan and analyze design data of a semiconductor device for optimizing manufacturing of the semiconductor device. The DMO software module sets up a pattern signature database and a manufacturing optimization database, generates design-based manufacturing recipes, interfaces with manufacturing equipment through a manufacturing interface module, and interfaces with electronic design automation suppliers for the design data through a design interface module. The DMO server executes the design-based manufacturing recipes for manufacturing optimization.

Owner:APPLIED MATERIALS INC

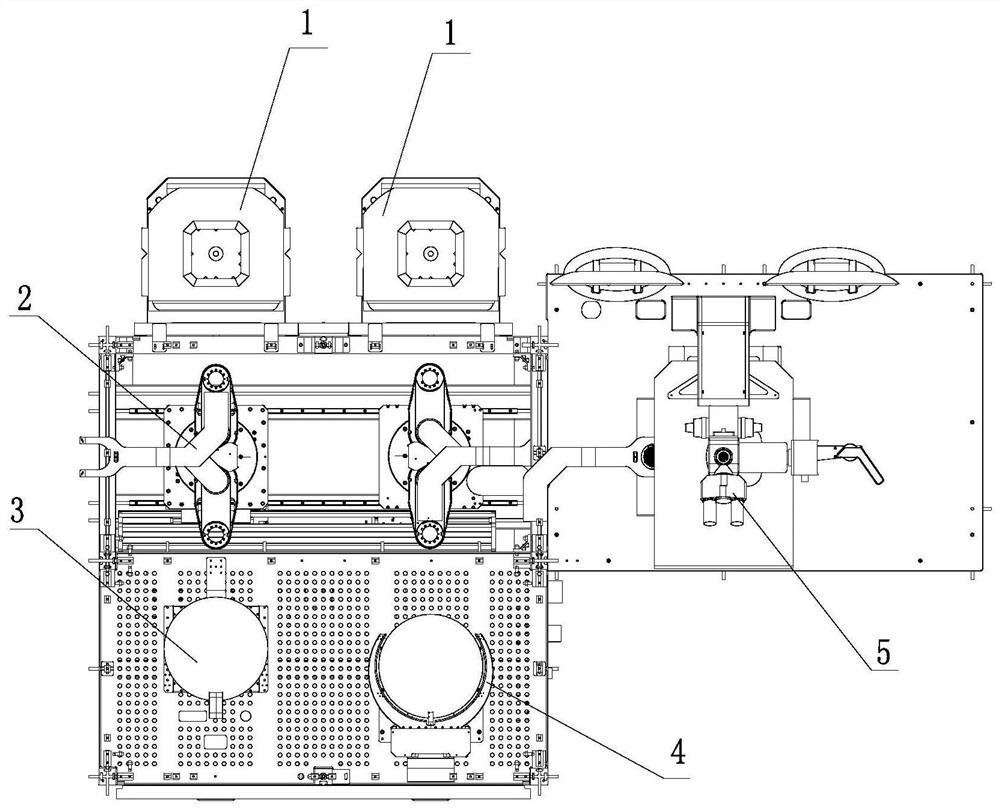

Full-automatic wafer appearance inspection system

PendingCN112820660AQuick judgment of tilt and bendRelieve fatigueSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMicroscopic observationEngineering

The present invention relates to a full-automatic wafer appearance inspection system which comprises a wafer box opening carrier, a wafer taking and placing manipulator, a wafer position calibration mechanism, a wafer turnover mechanism and a microscope detection mechanism, the wafer box opening carrier is used for opening a wafer conveying box, the wafer taking and placing manipulator is used for carrying wafers, and the wafer position calibration mechanism is used for determining the circle center position of the wafer and rotating the wafer to a specified angle; and the wafer turnover mechanism is used for turnovering a wafer so as to inspect the back surface of the wafer, and the microscope detection mechanism inspects the surface of the wafer. The wafer can be automatically transmitted to the microscope for observation, so that damage caused by manual carrying is avoided; the surface and the back surface of the wafer can be visually inspected; and linear motion is adopted in the transmission process, and the wafers are prevented from being thrown out. The system is suitable for being used in semiconductor factories and wafer test factories.

Owner:无锡奇众电子科技有限公司

Circular Test Pads on Scribe Street Area

InactiveUS20070243643A1High yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringSemiconductor fab

A semiconductor wafer design and process having test pads (36) reducing cracks generated during the wafer saw process from extending into and damaging adjacent die. The present invention provides a plurality of circular test pads (36) in a wafer scribe street (34) such that any cracks generated in the test pad during wafer saw self terminate in the periphery of the circular test pad. By providing a curved test pad periphery, cracks will tend to propagate along the edges of the test pads and self terminate therein. The circular test pads avoid any sharp corners as is conventional in rectangular test pads which tend to facilitate the extension of cracks from corners to extend into the adjacent wafer die (32). The present invention utilizes existing semiconductor fab processing and utilizes new reticle sets to define the curved test pads.

Owner:TEXAS INSTR INC

Address-transparent device and method

ActiveUS7787477B2Without significant delay and feeCost-effectiveError preventionFrequency-division multiplex detailsComputer networkData stream

An address-transparent device is disclosed that couples two networks in a semiconductor fab and communicates packets between a host on a first network and a tool on a second network. Optionally, the address-transparent device intercepts packets for local use by a data consumer that resides within or outside of the address-transparent device. The address-transparent device can intercept all or a portion of data streams. As another option, the address-transparent device reroutes packet to another destination by changing the header of the received packet.

Owner:MKS INSTR INC

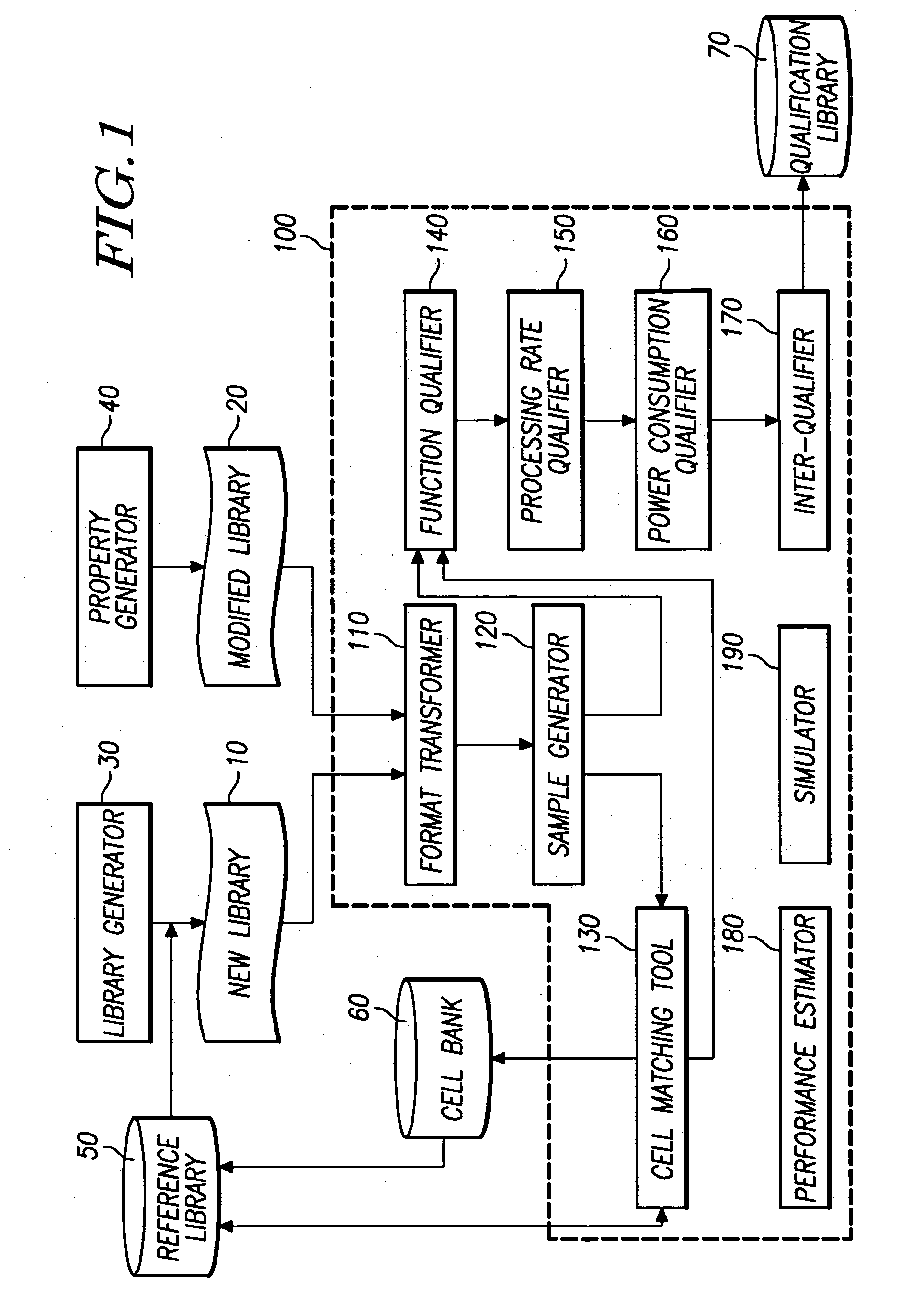

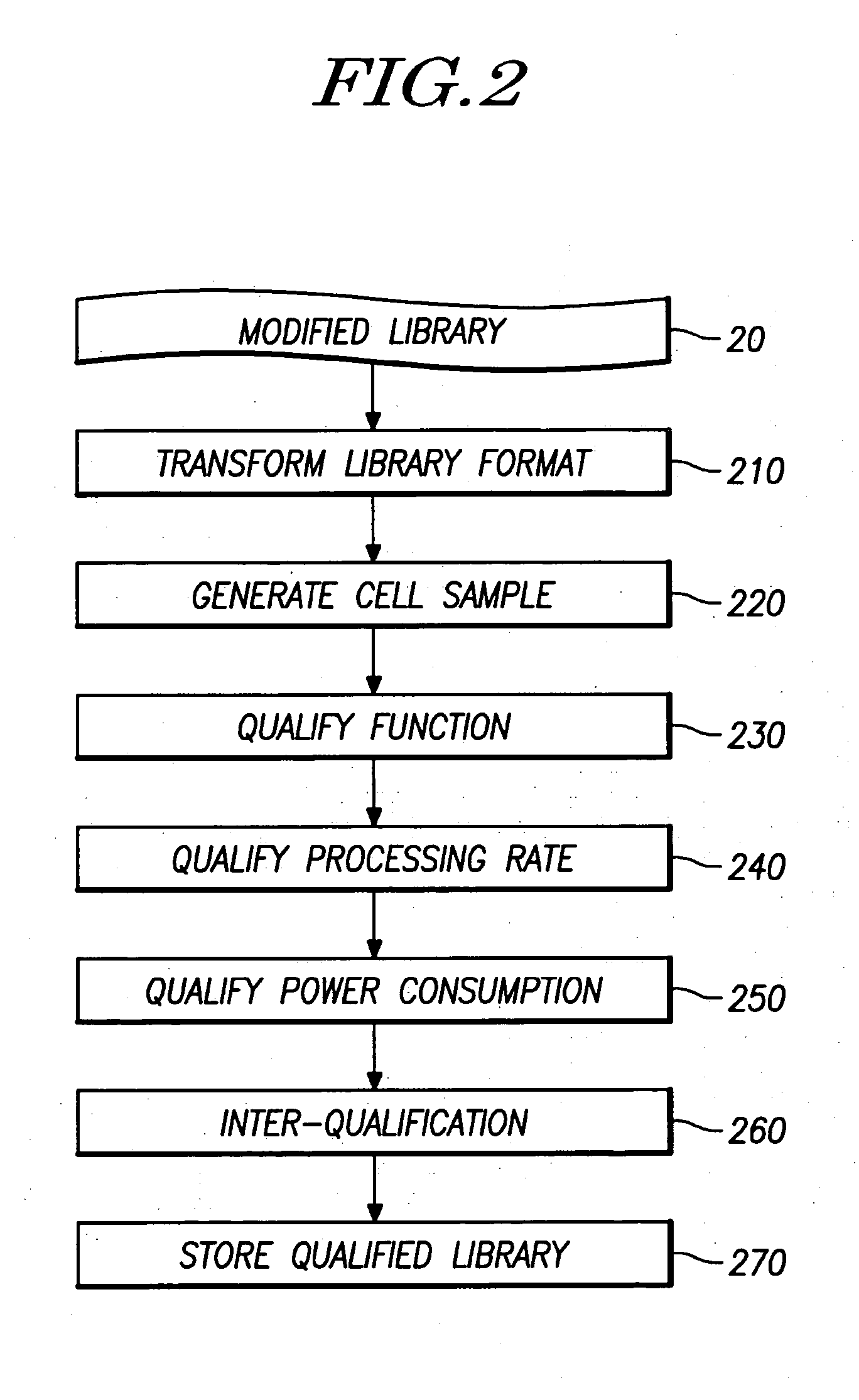

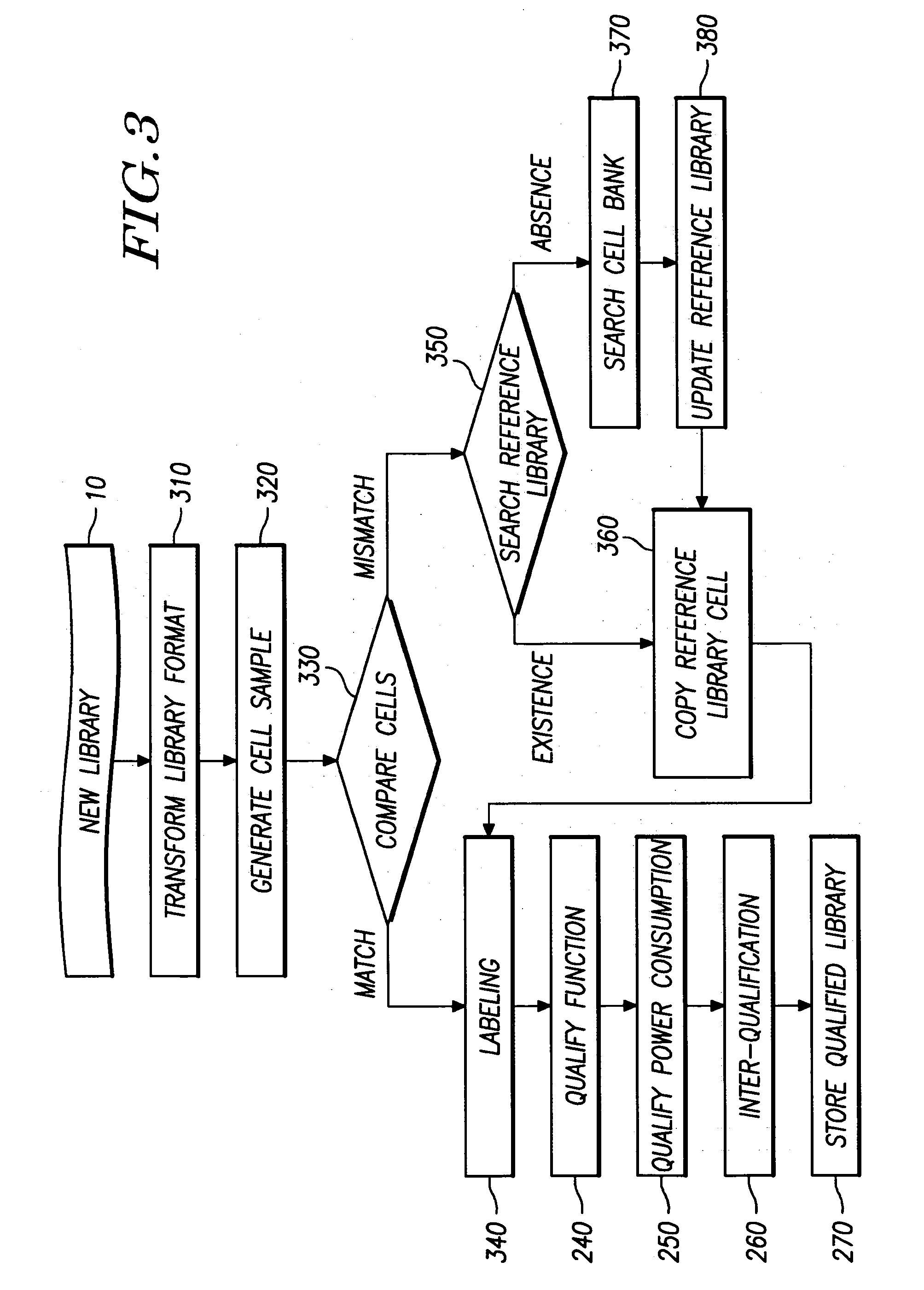

System and method for qualifying a logic cell library

InactiveUS7549133B2Efficient implementationSemiconductor/solid-state device manufacturingCAD circuit designCell processingLogic cell

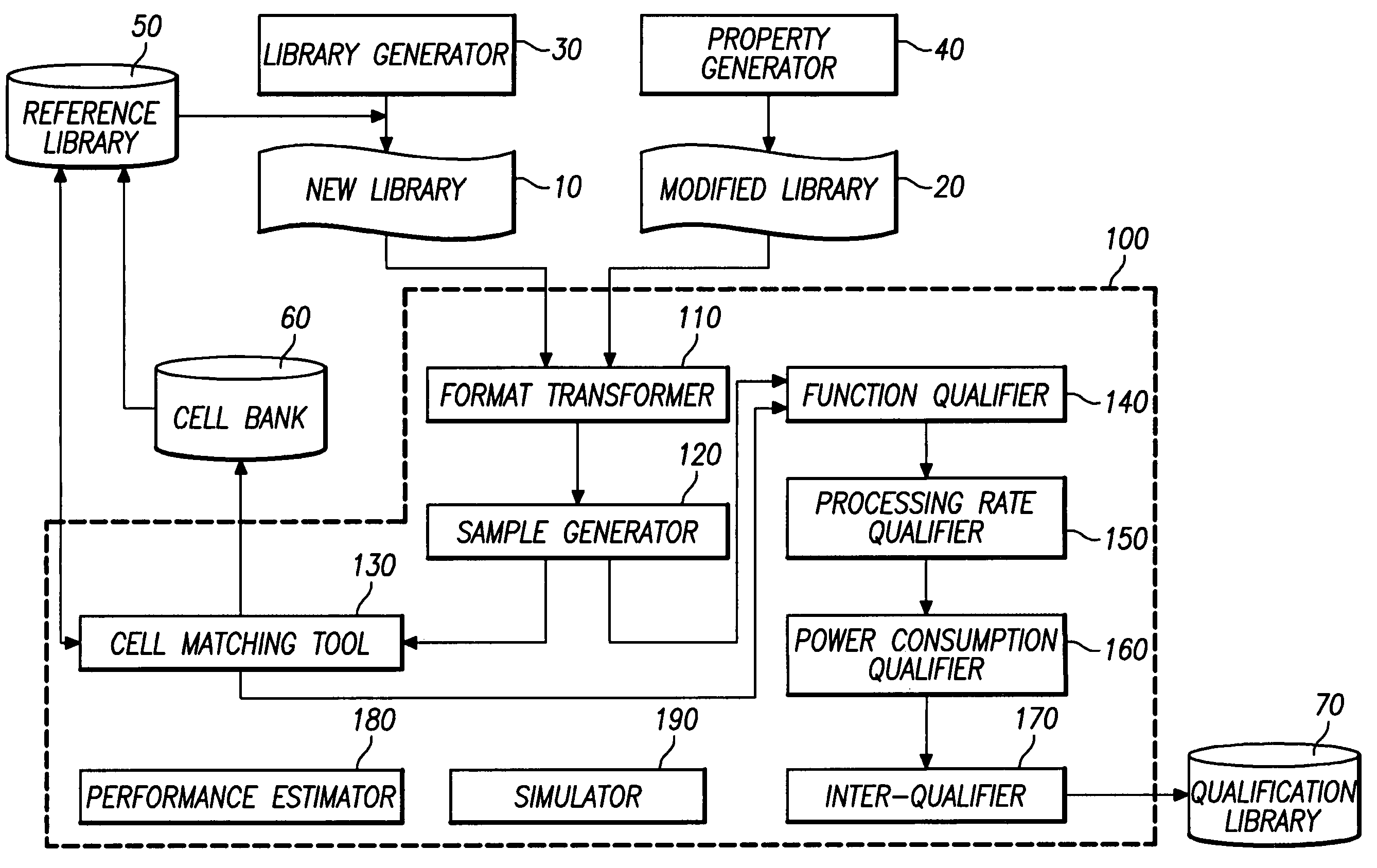

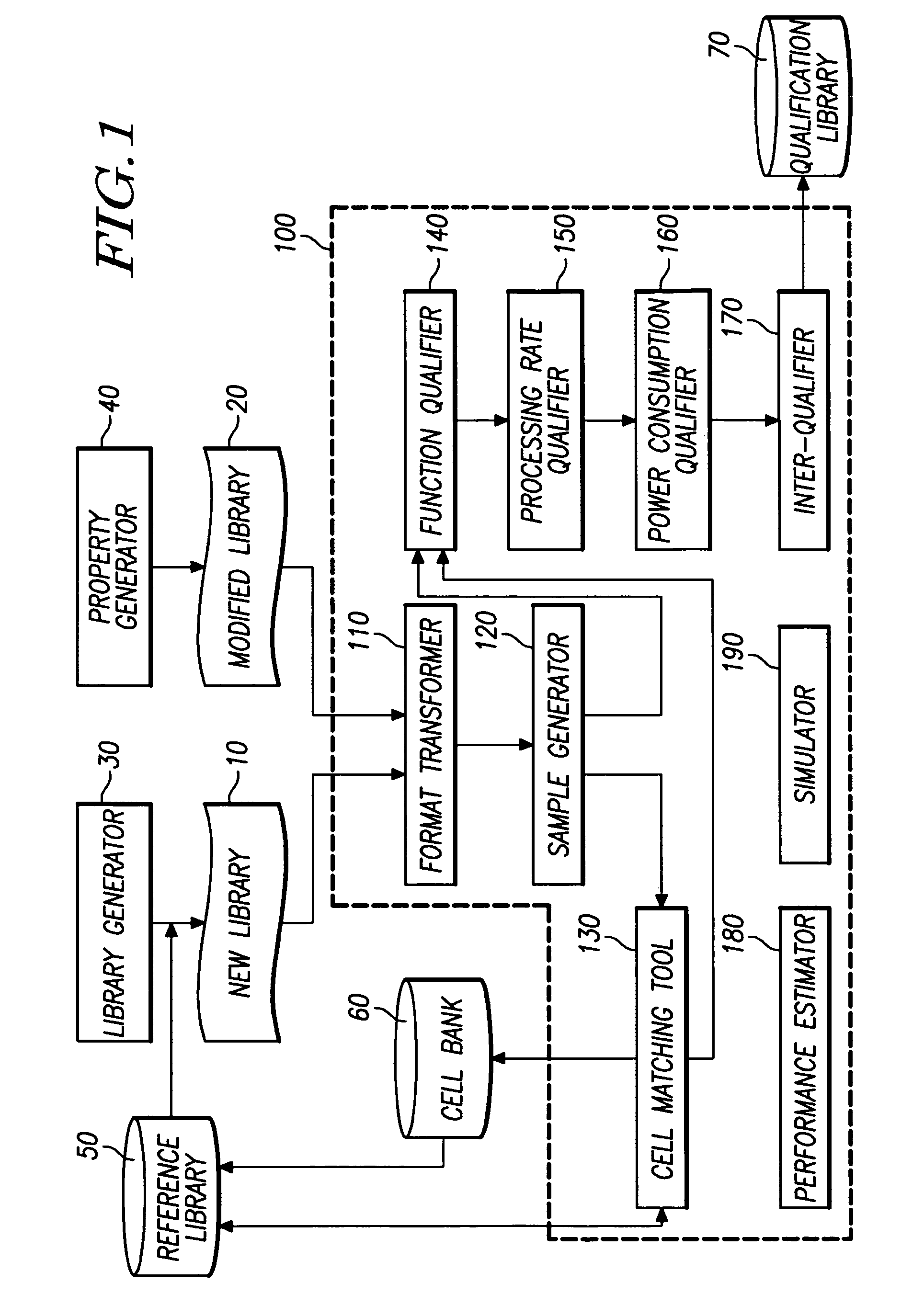

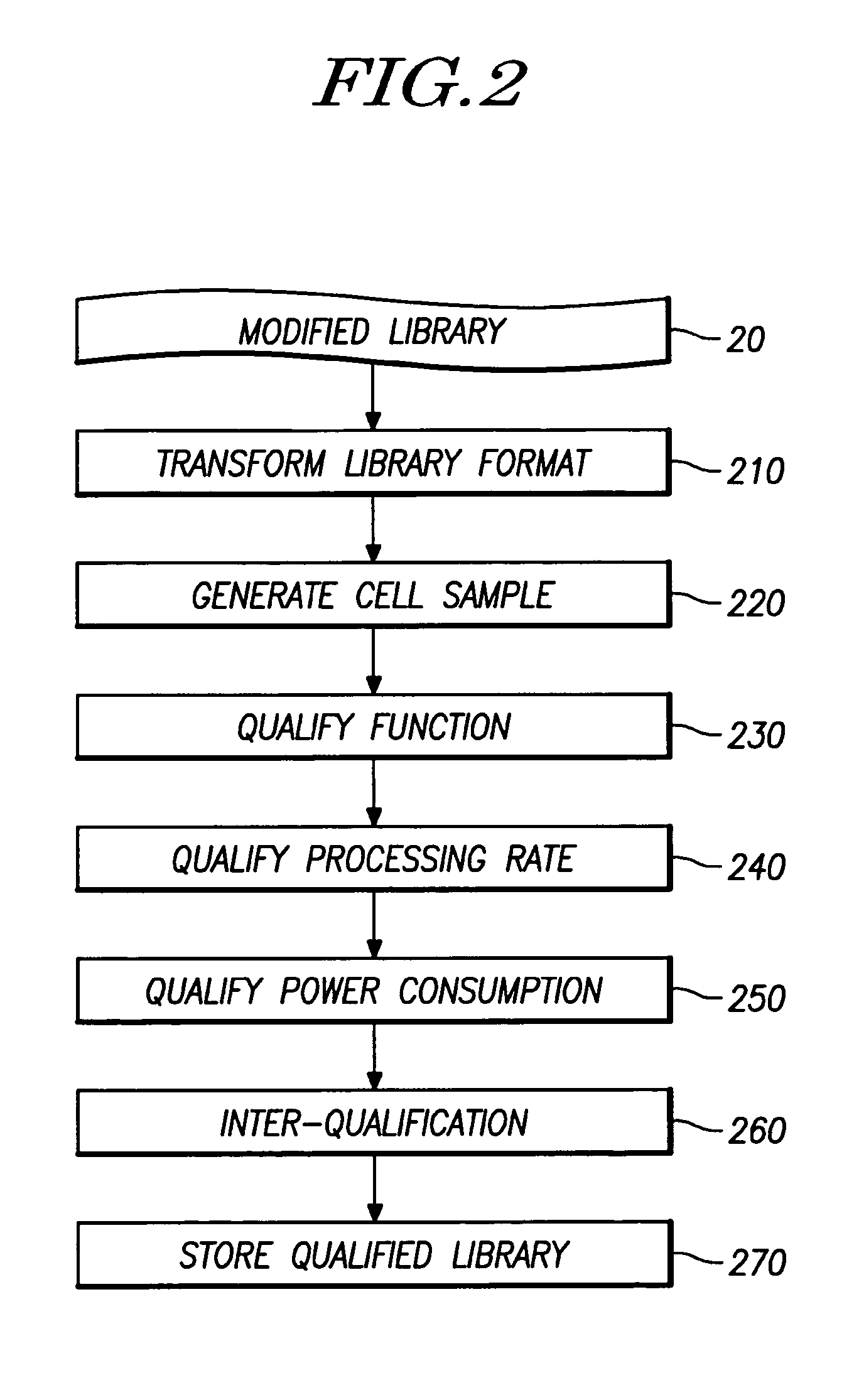

A system and a method for qualifying a logic cell library storing process parameters and properties of a specific semiconductor FAB when the logic cell library is newly developed or modified is provided. The system for qualifying a logic cell library which qualifies a new library and a modified library, includes a format transformer for transforming formats of the new library and the modified library into formats suitable for a predetermined qualifier, a sample generator for creating a qualification cell sample capable of qualifying all cells by using cells of the new or modified library having a transformed format, a cell matching tool for performing a one-to-one cell comparison between cells of the new library and cells of an existing library, a function qualifier for determining whether or not a right value is output with respect to an input value in order to qualify a cell function of the new or modified library, a processing rate qualifier for measuring a time required from signal input to signal output in order to qualify a cell processing rate of the new or modified library, a power consumption qualifier for measuring power consumed during a process of a cell of the new or modified library, and an inter-qualifier for determining whether or not logical design information and physical design information of the new or modified library suitably corresponds to each other.

Owner:DONGBU ELECTRONICS CO LTD

Co-planarity examination method and optical module for electronic components

InactiveUS7012682B2Minimize and substantially eliminate problemAccurate measurementInvestigating moving sheetsUsing optical meansOptical ModuleSemiconductor fab

Manufacturing lines include inspection systems for monitoring the quality of parts produced. Manufacturing lines for making semiconductor devices generally inspect each fabricated part. The information obtained is used to fix manufacturing problems in the semiconductor fab plant. A machine-vision system for imaging an object having a first side and a second side includes an imager, and an optics apparatus that images two or more views of the first side of the object and images two or more views of the second side of the object. The two or more views of the first side and the second side of the object are each from different angles. The object includes at least one major surface. A divider background surface is placed near the at least one major surface of the object to obtain separate images of features of the object on the first side of the object and features of the object on the second side of the object. In one embodiment, the divider diffuses light to back light the features on the object on the first side and back light the features on the second side of the object.

Owner:LEMAIRE CHARLES A

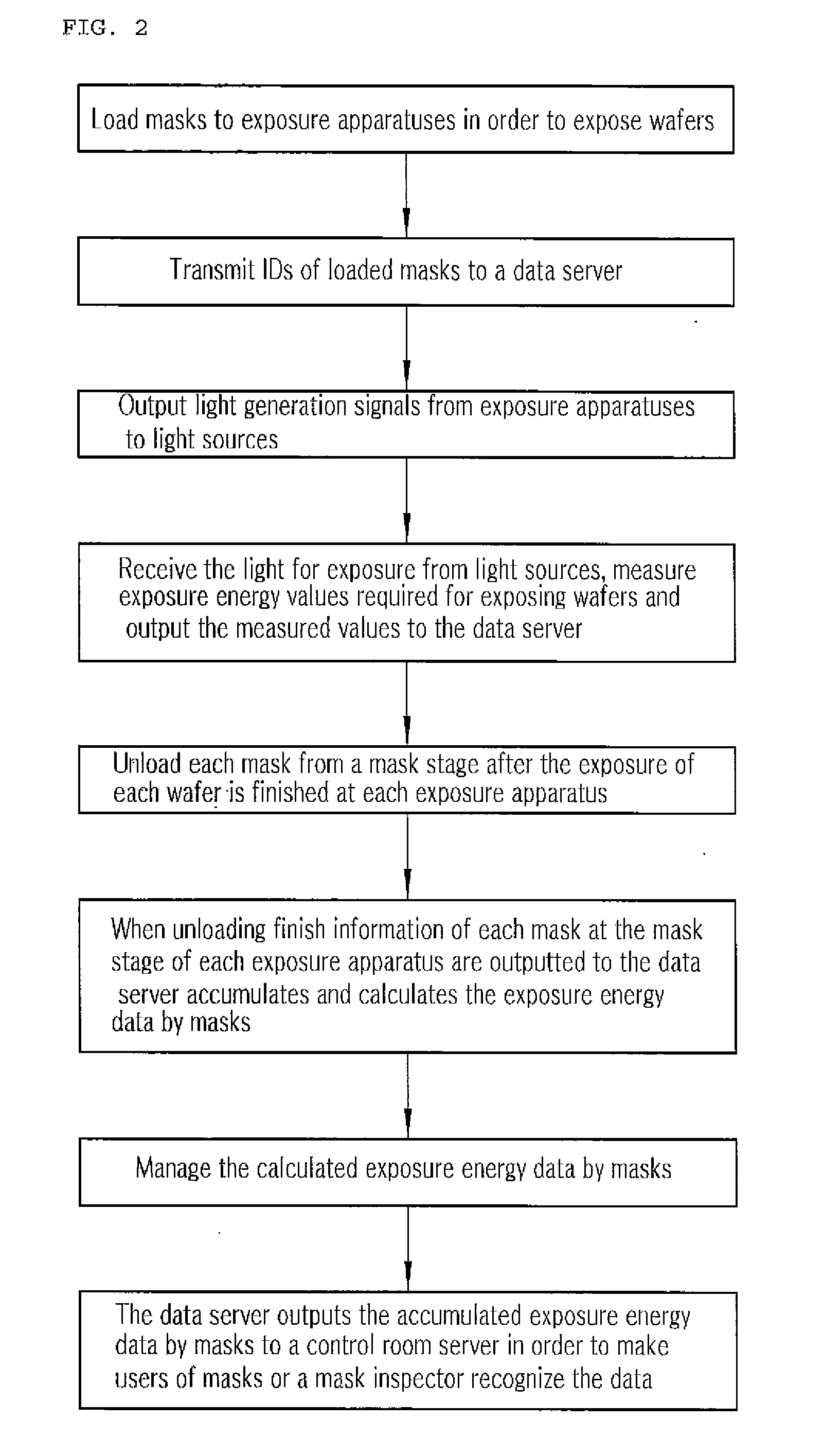

System for accumulating exposure energy information of wafer and management method of mask for exposure utilizing exposure energy information of wafer accumulated with the system

ActiveUS20080175467A1Increase productionMaterial analysis by optical meansSemiconductor/solid-state device manufacturingLight energyApproaches of management

Disclosed is a management method of a mask for exposure utilizing exposure energy information of a wafer. According to the present invention, in case of exposing wafers in exposure apparatuses, information on masks loaded on exposure apparatuses are calculated from the exposure apparatuses, the light energy values applied during the exposure of wafers by the corresponding masks are calculated, the calculated light energy values are stored in the data server, the same data are collected from all wafer exposure processes performed at plural exposure apparatuses within the semiconductor FAB and the exposure information about the exposure energy relating to plural masks used by plural exposure apparatuses are accumulated and managed. Accordingly, the exposure degree of a mask about the exposure energy, as a direct cause of the contamination of masks such as the crystal growth and haze, is directly calculated and then defects of masks are predicted together with measures according that, so that deterioration of the yield of the semiconductor is prevented and the yield of the semiconductor is increased.

Owner:CYMER KOREA

Method for improved semiconductor processing equipment tool pedestal/pad vibration isolation and reduction

A method to improve vibration isolation in semiconductor process level inhibits vibration frequencies transmitted though building structure from production tools, pumps, compressors, chillers, AHUs (Air Handling Units), and footfalls traffic on raised floor system on to tool pedestals and pads from affecting semiconductor fabrication processes. The tool pedestal / pad for modern semiconductor FABs are required have very small tolerance to ambient vibration. Therefore, reduction and isolation of vibration of tool pedestal / pad is the key requirement for safe, reliable and uninterrupted operation of modern semiconductor FABs. Sound proofing material and foam is injected into hollow steel and / or aluminum support members and sound proofing adhesives and / or caulking are applied at points of connections in conjunction with mechanical fastening. In various applications, placement of shaped wielded rod utilized for dissipating vibration energy in center of hollow member which is surrounded with sound proofing material and / or foam.

Owner:SK COMML CONSTR INC

Composite slurry for doping in semiconductor industry and curing film-forming processing method

PendingCN111825853AModerate hardnessModerate intensitySemiconductor/solid-state device manufacturingWater/sewage treatment by heatingPapermakingSemiconductor fab

The invention discloses composite slurry for doping in the semiconductor industry and a curing film-forming processing method. The invention belongs to the field of high polymer materials, and particularly relates to composite slurry for doping in the semiconductor industry and a subsequent curing molding manufacturing method. According to the curing film-forming processing method of composite slurry for doping in the semiconductor industry, the composite slurry for doping is used for processing the composite slurry for doping by adopting wet papermaking equipment, and the composite slurry ischaracterized in that the composite slurry for doping is washed by deionized water or ultrapure water before being put into the wet papermaking equipment. The composite slurry and the forming film thereof are moderate in hardness, moderate in strength and uniform and consistent in doping, and the strict index requirement that the product yield is larger than 99.999% is met when parallel contrast tests are conducted on famous semiconductor manufacturers and imported products in China. The composite slurry has positive significance for realizing import substitution of the product and getting ridof dependence on foreign imported products.

Owner:崔恩密 +1

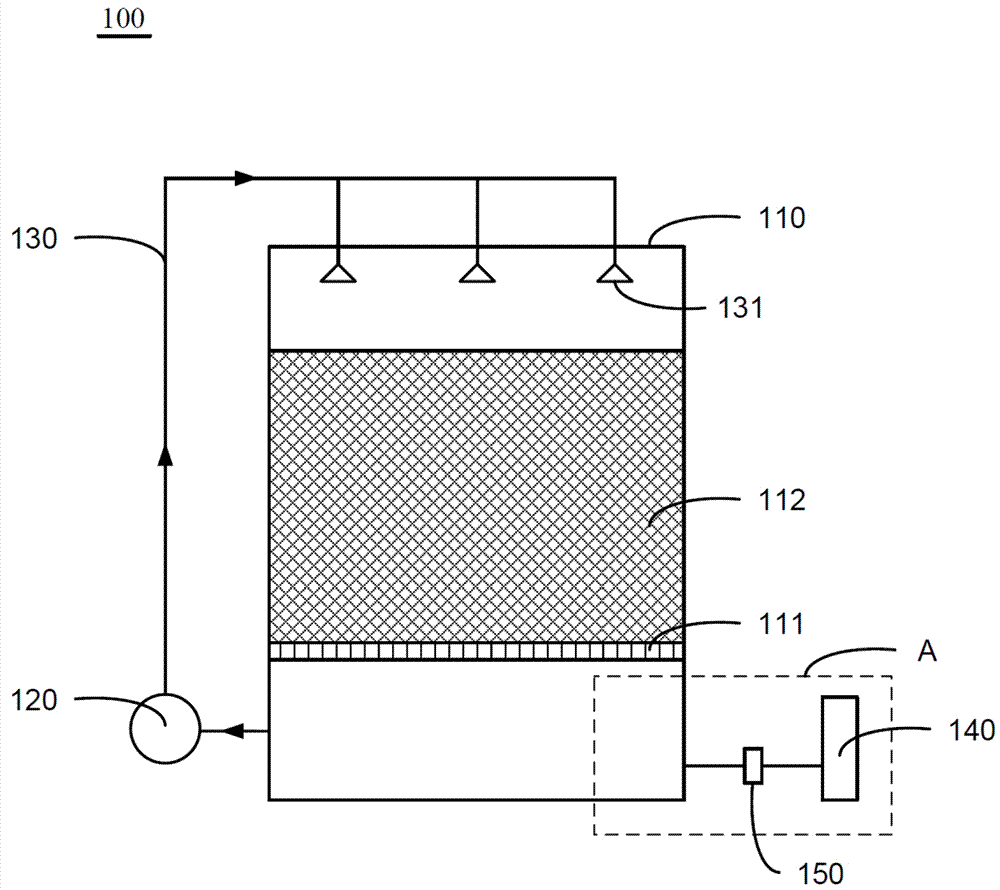

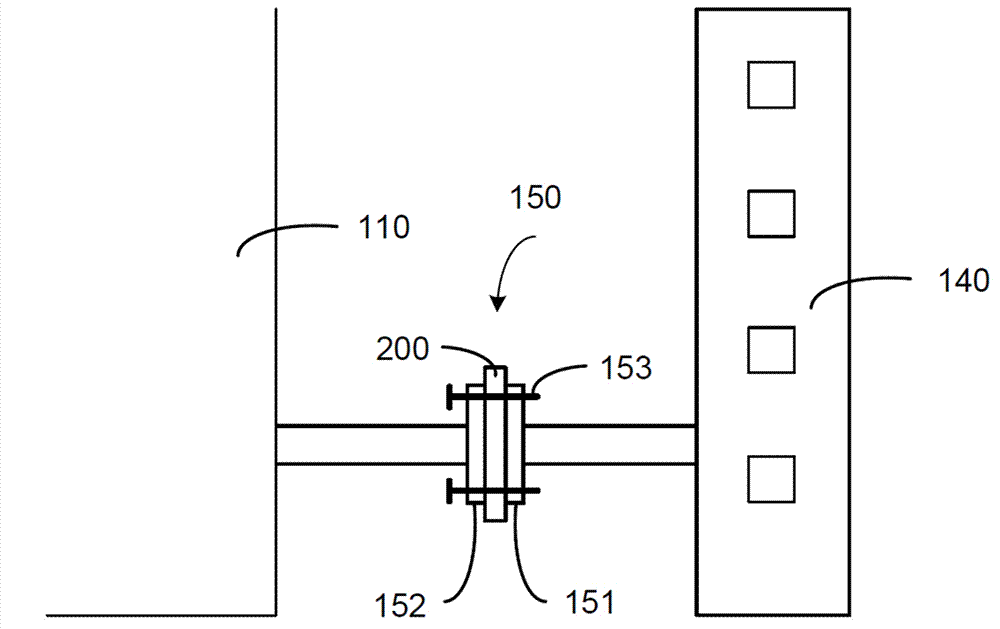

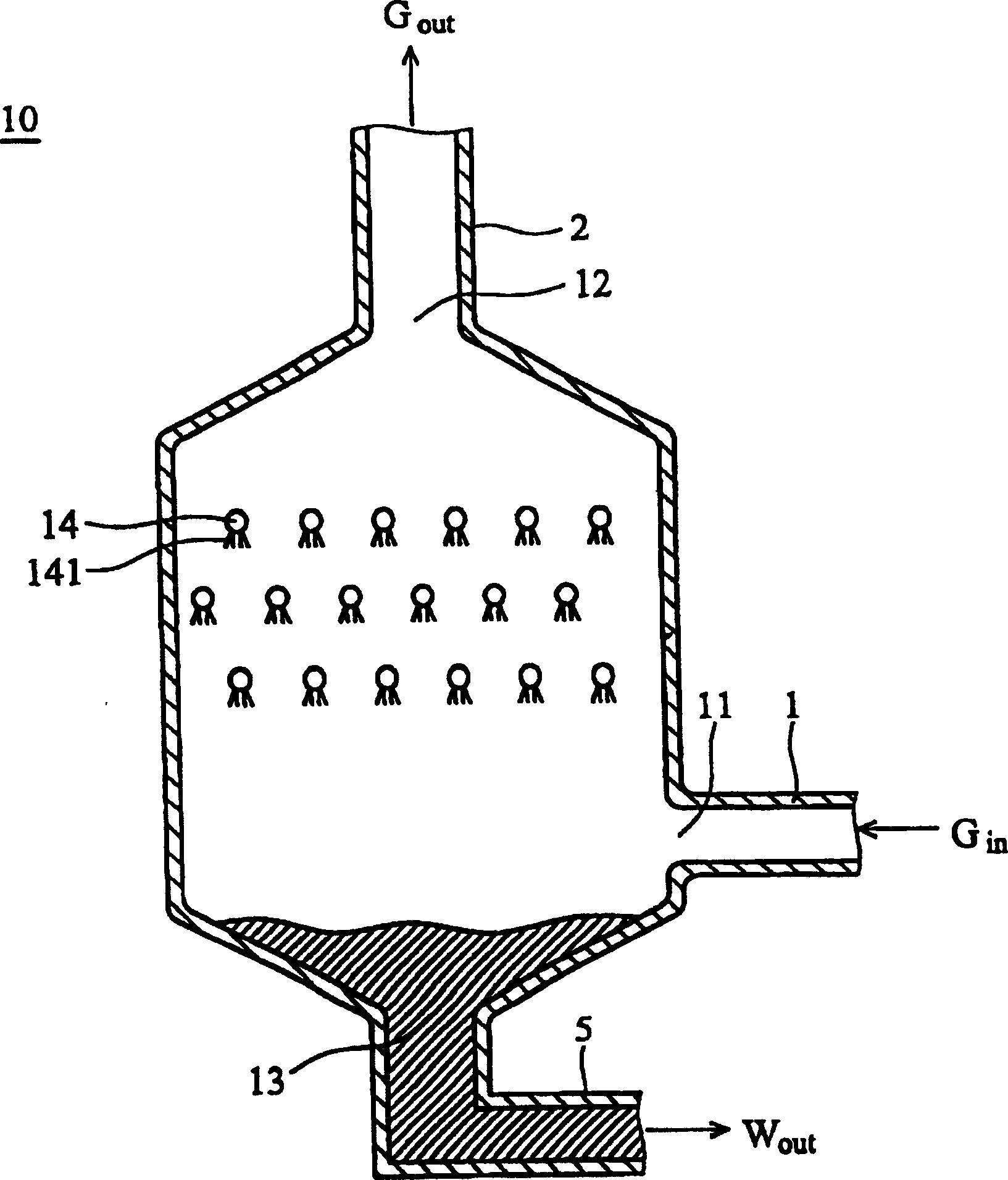

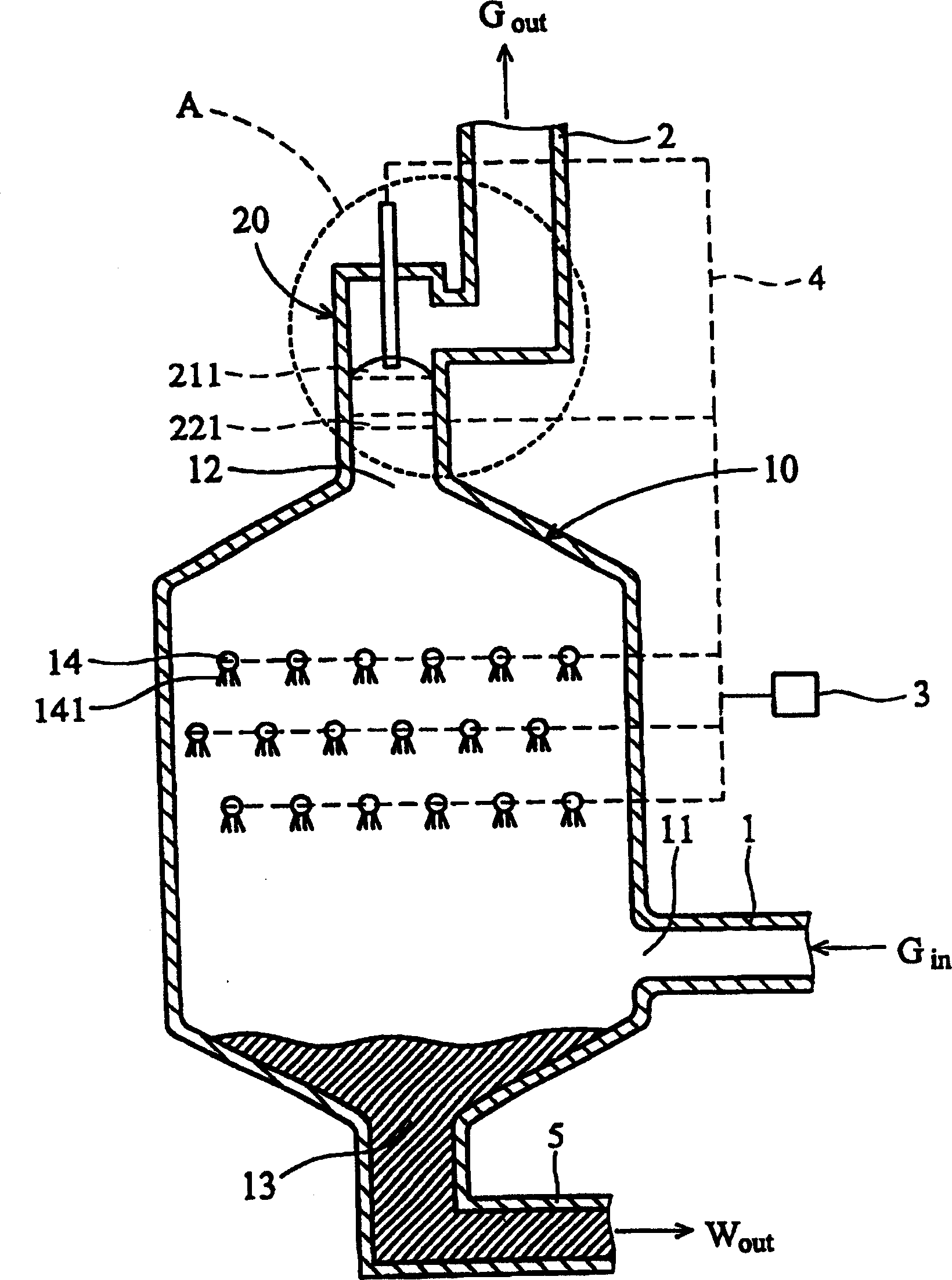

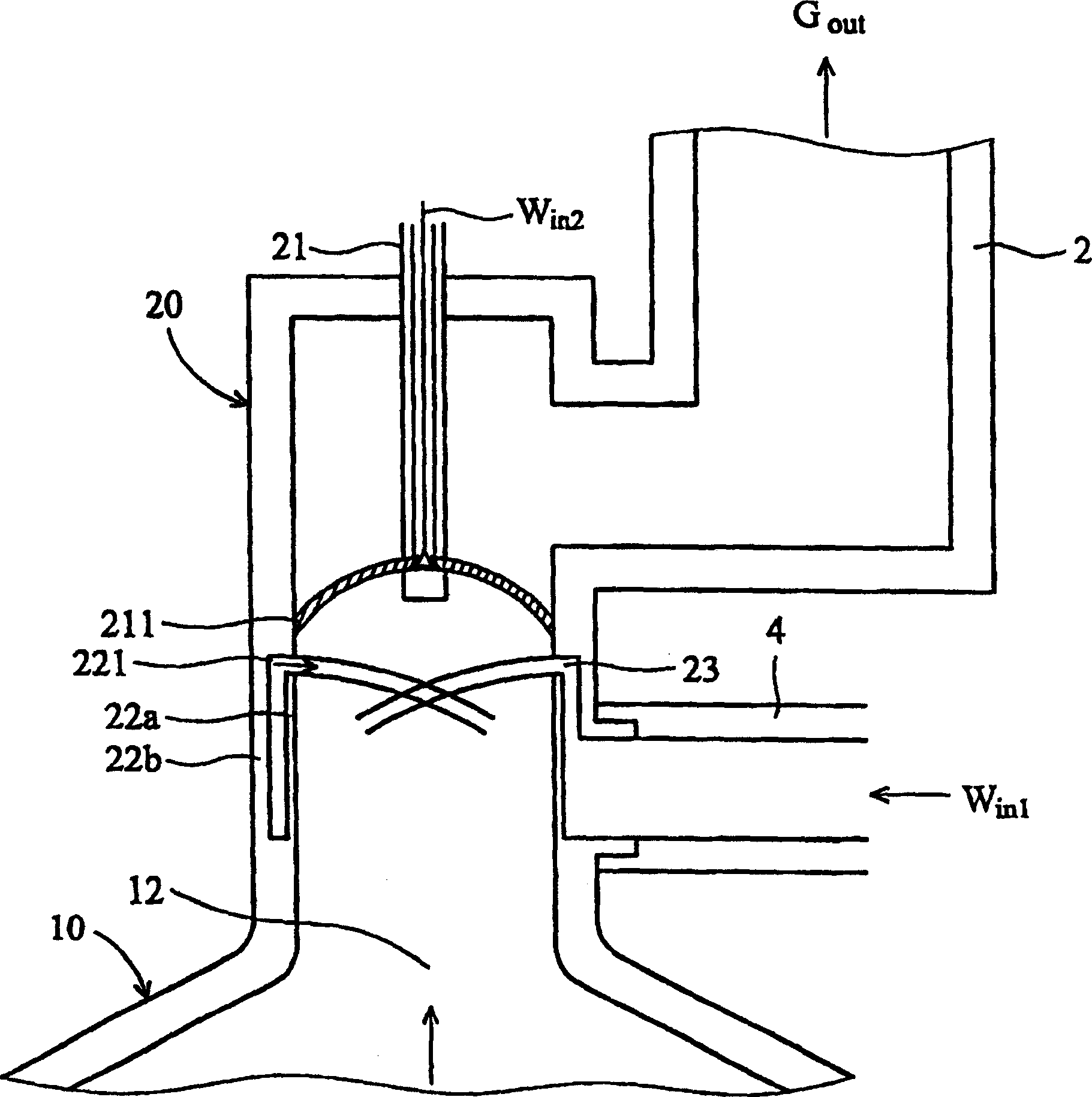

Scrubbing tower used for acidic and alkaline exhaust gas of semiconductor plants

InactiveCN103084051AExcellent acid and alkali exhaust treatment effectAffect the washing effectDispersed particle separationFilling materialsSemiconductor fab

The invention discloses a scrubbing tower used for acidic and alkaline exhaust gas of semiconductor plants. The scrubbing tower comprises a circulation detergent box. A porous separation plate is arranged at the middle of the circulation detergent box. The part of the circulation detergent box below the separation plate is used for collecting a detergent. A filling material used for increasing the contact area between the acidic and alkaline exhaust gas and the detergent is arranged on the separation plate. The scrubbing tower also comprises a circulation pump and a circulation pipeline. The circulation pump is connected with the circulation detergent box through the circulation pipeline, and is used for driving the circulation flow of the detergent. The scrubbing tower also comprises a liquidometer which is arranged on the lower part of the circulation detergent box and is connected with the circulation detergent box through a connection device. A filtering device is arranged on the connection device. With the scrubbing tower provided by the invention, impurities and scraps of filling materials can be effectively prevented from entering the liquidometer and damaging the liquidometer; and scrubbing tower scrubbing effect is prevented from being affected by excessively low liquid level in the scrubbing tower. The scrubbing tower has a simple structure, and provides an excellent processing effect upon semiconductor plant acidic and alkaline exhaust gases.

Owner:CSMC TECH FAB2 CO LTD

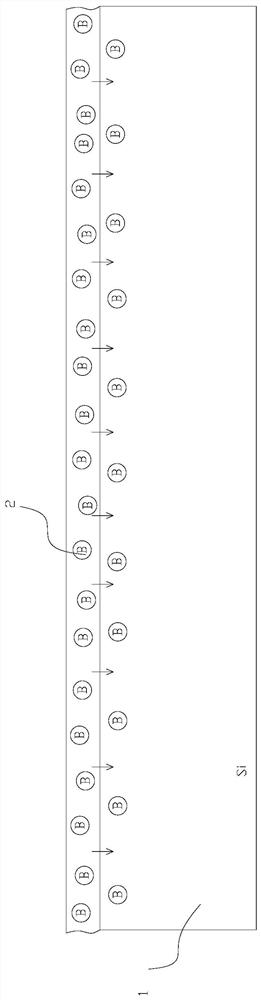

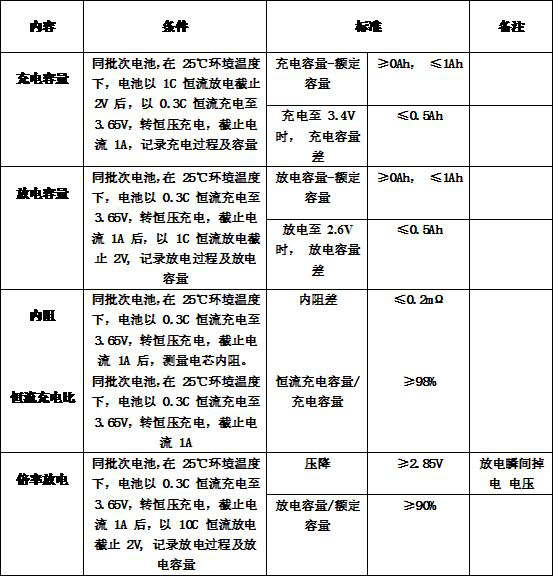

Battery cell consistency sorting method applied to energy storage lithium batteries of semi-conductor factories

The invention relates to a battery cell consistency sorting method applied to energy storage lithium batteries of semiconductor factories. The method comprises the following steps that charging capacity, discharging capacity, internal resistance, constant-current charging ratio and multiplying power screening is carried out, the batteries in the same batch are discharged and then charged, and the batteries of which the difference value between the charging capacity and rated capacity meets the requirement are screened out; the screened batteries are discharged and then charged, and the batteries of which the difference value between the discharge capacity and the rated capacity and the discharge capacity meet the requirements are screened out; and the screened batteries are charged, the batteries with the internal resistance difference less than or equal to 0.2 milliohm are screened out, and the ratio of the constant-current charging capacity to the charging capacity is greater than or equal to 98%. The screened batteries are charged and then discharged, and the batteries with the voltage drop larger than or equal to 2.85 V and the ratio of the discharging capacity to the rated capacity larger than or equal to 90% are screened out. The method has the advantages that the screened lithium ion batteries can keep good battery consistency in the aspects of charging capacity, rate discharge and the like, and in addition, the lithium ion batteries screened by the screening standards related to charging capacity, rate discharge and the like are more suitable for the semiconductor factories.

Owner:芜湖楚睿智能科技有限公司

System and method for qualifying a logic cell library

InactiveUS20070148705A1Efficient implementationLibrary screeningSemiconductor/solid-state device manufacturingCell processingLogic cell

A system and a method for qualifying a logic cell library storing process parameters and properties of a specific semiconductor FAB when the logic cell library is newly developed or modified is provided. The system for qualifying a logic cell library which qualifies a new library and a modified library, includes a format transformer for transforming formats of the new library and the modified library into formats suitable for a predetermined qualifier, a sample generator for creating a qualification cell sample capable of qualifying all cells by using cells of the new or modified library having a transformed format, a cell matching tool for performing a one-to-one cell comparison between cells of the new library and cells of an existing library, a function qualifier for determining whether or not a right value is output with respect to an input value in order to qualify a cell function of the new or modified library, a processing rate qualifier for measuring a time required from signal input to signal output in order to qualify a cell processing rate of the new or modified library, a power consumption qualifier for measuring power consumed during a process of a cell of the new or modified library, and an inter-qualifier for determining whether or not logical design information and physical design information of the new or modified library suitably corresponds to each other.

Owner:DONGBU ELECTRONICS CO LTD

Method for controlling doping density of doped region of semiconductor device accurately

ActiveCN102254801BPrecise control of concentrationSimple and fast operationSemiconductor/solid-state device manufacturingSemiconductor fabSilicon dioxide

The invention provides a method for controlling the doping density of a doped region of a semiconductor device accurately. In the method, a silicon wafer is oxidized; a photoresist is added to a boron emulsion source in the coating process; and the boron emulsion source is mixed with the photoresist, and the mixture is placed in a stirring vessel for sufficient stirring so as to obtain an emulsion source coating liquid, wherein the photoresist is carbonized at a high temperature to so as to remove gases carried in the diffusion process, thus obtaining the required impurity density distribution in a boron region. The method is easy and convenient to operate, simple in equipment and is suitable for massive production. The diffusion parameters of the method can be controlled and adjusted freely; the doping density is adjustable; a silica oxidation layer is formed on the silicon wafer by diffusible oxidation; the thickness accuracy in oxidization is controlled so as to reach the density for controlling diffusion impurities accurately; the technological process is simplified; the production cost is reduced; and the yield of the semiconductors is improved by over 20%. The method is particularly suitable for low and medium-grade semiconductor manufacturers to produce the semiconductors massively; and the method has the advantage of remarkable economic benefit.

Owner:JILIN SINO MICROELECTRONICS CO LTD

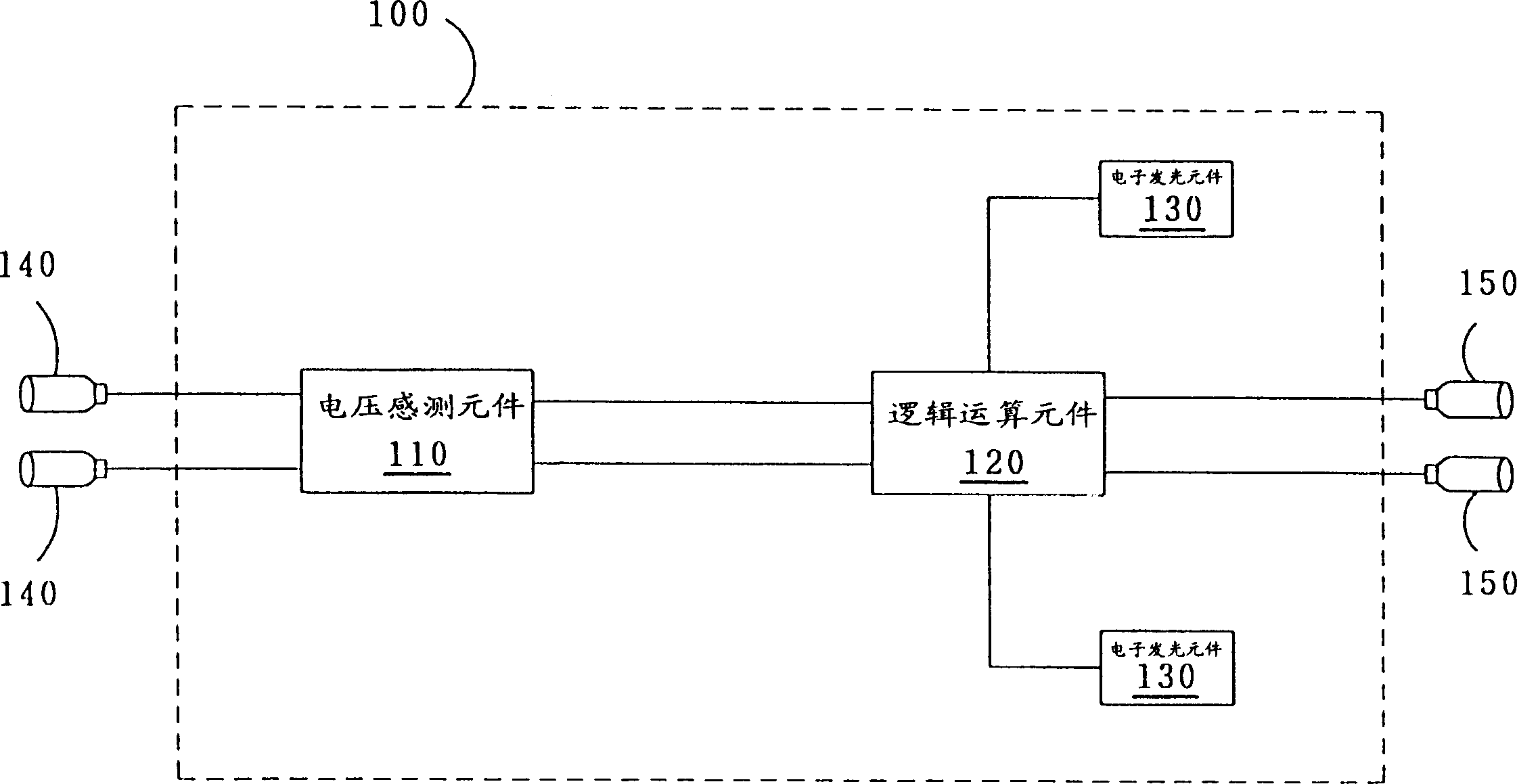

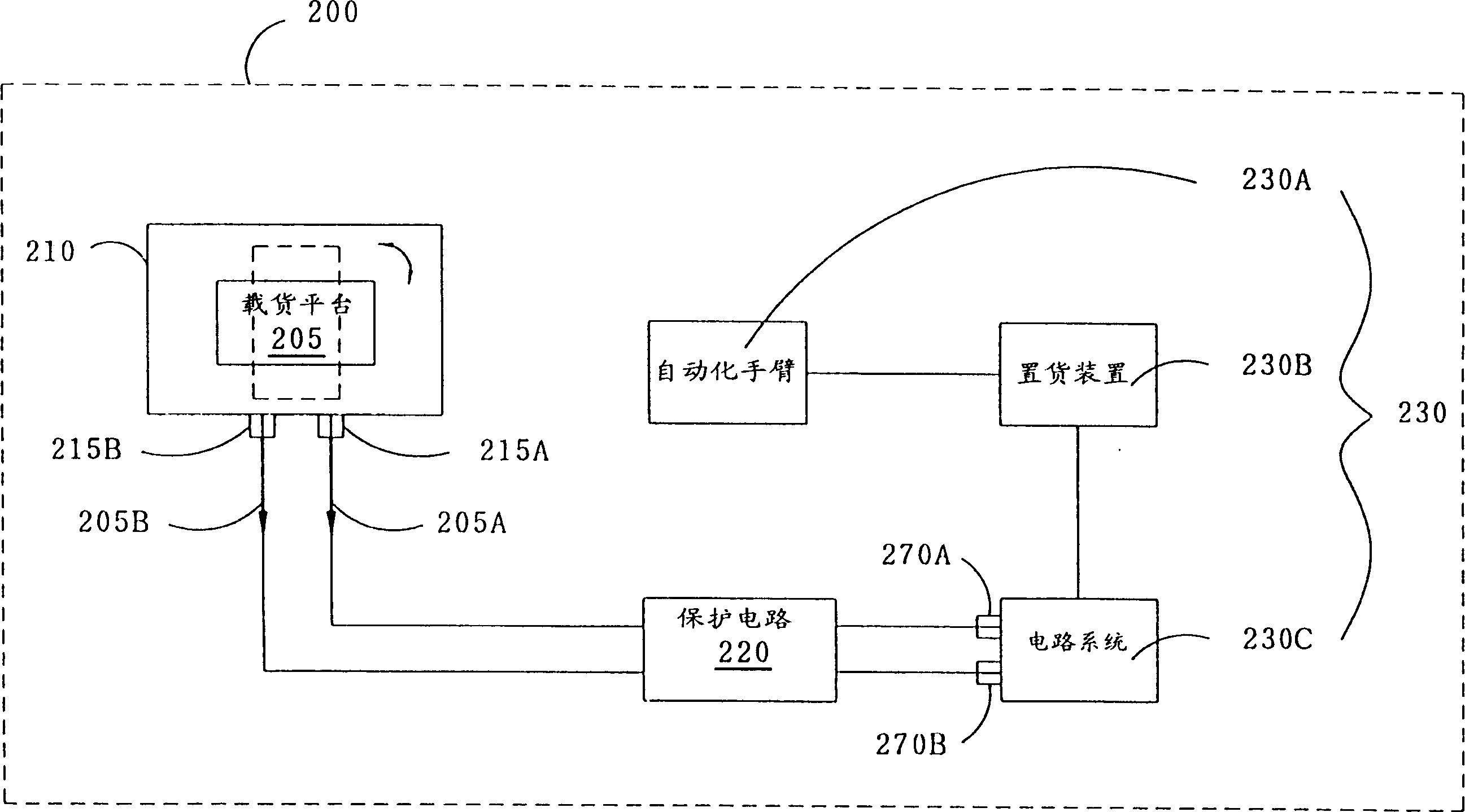

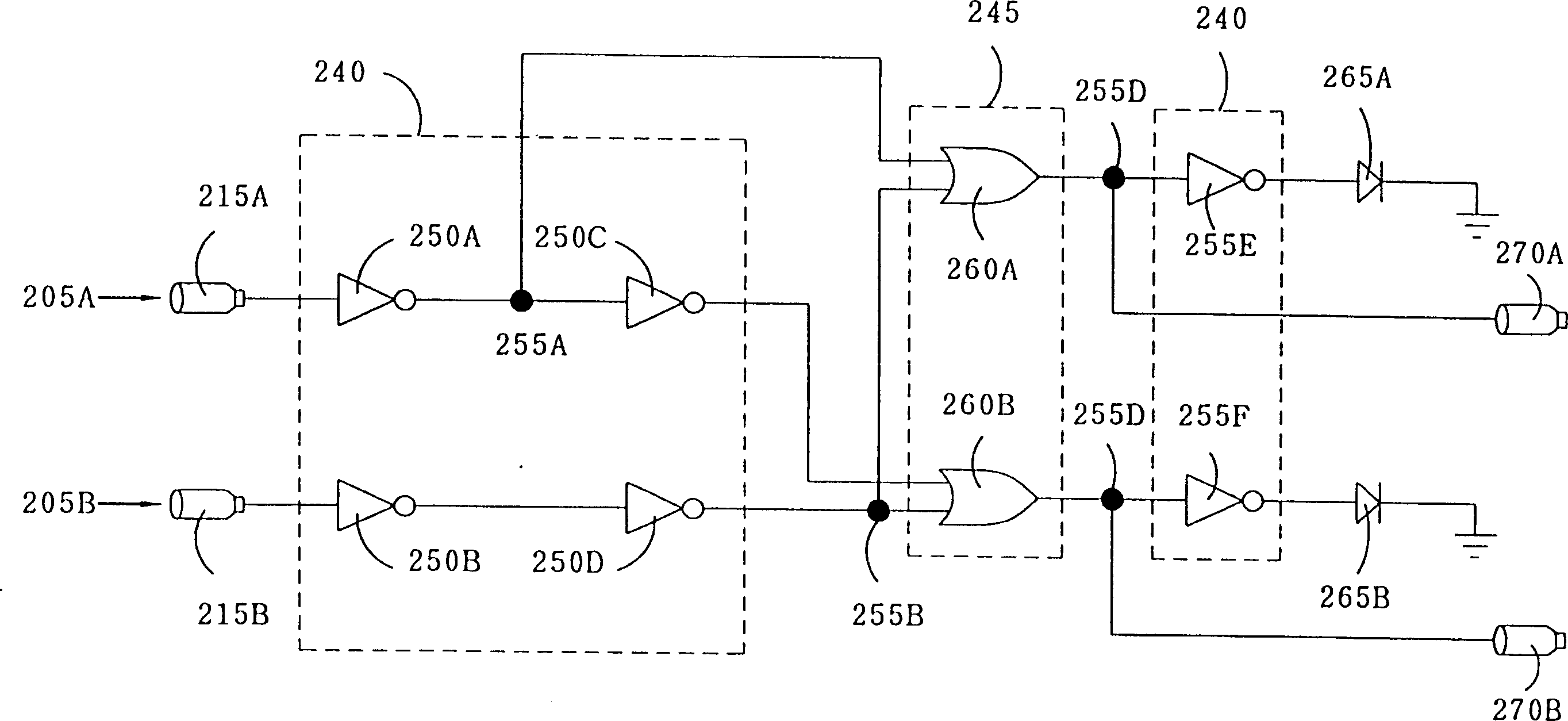

Protective circuit of automation for semiconductor factory

InactiveCN1423303AImprove stabilityReduce maintenance costsSemi-permeable membranesSemiconductor/solid-state device manufacturingSemiconductor factorySemiconductor fab

The invention discloses the protection circuit between the standard mechanical interface and the fabricating desk. First, the fabricating desk utilized in the semicondutor industry, the protection circuit and the automatic transport machining with the standard mechanical interface are provided. The protection circuit and the automatic transport machine with the standard mechanical interface are provided. The protection circuit includes at least the voltage sensing element, the logic assembly and the two luminous elements. The protection circuit through the voltage-sensing element receives the signal output by the fabricating desk and through the logic assembly makes the logic judgement to the signal output from the fabricating desk. The protecting circuit through the two luminous element displays the state of the fabricating desk and outputs the logic signals to the standard mechanical interface so as to control the operation of the automatic arm.

Owner:MACRONIX INT CO LTD

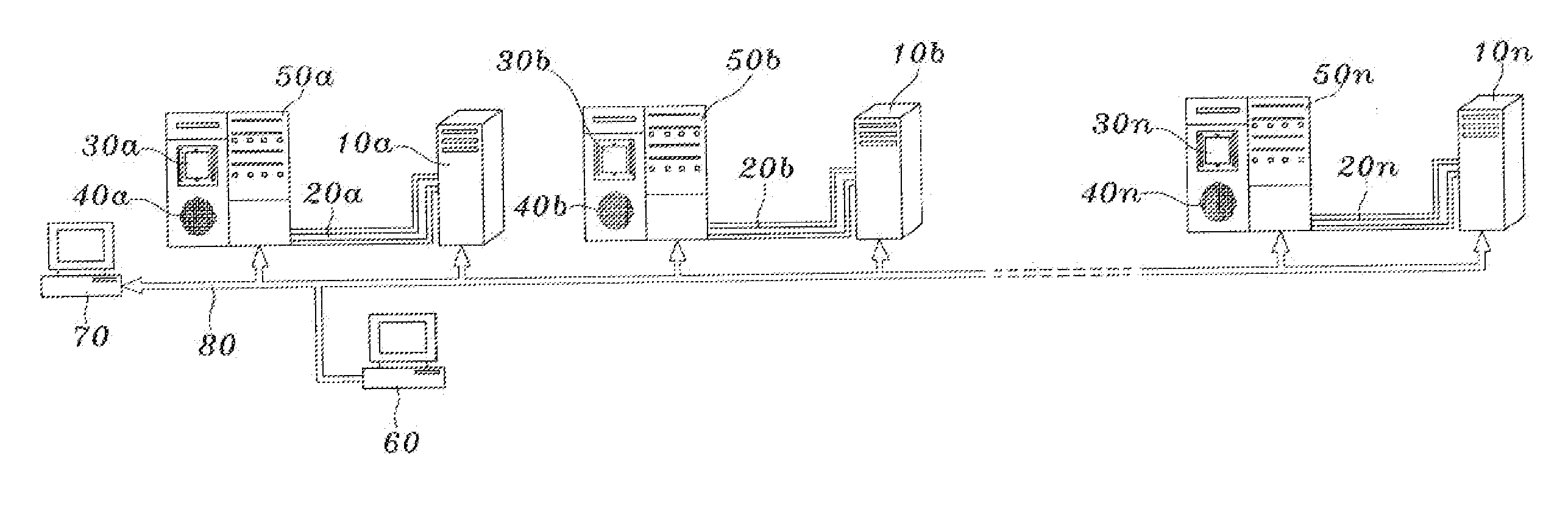

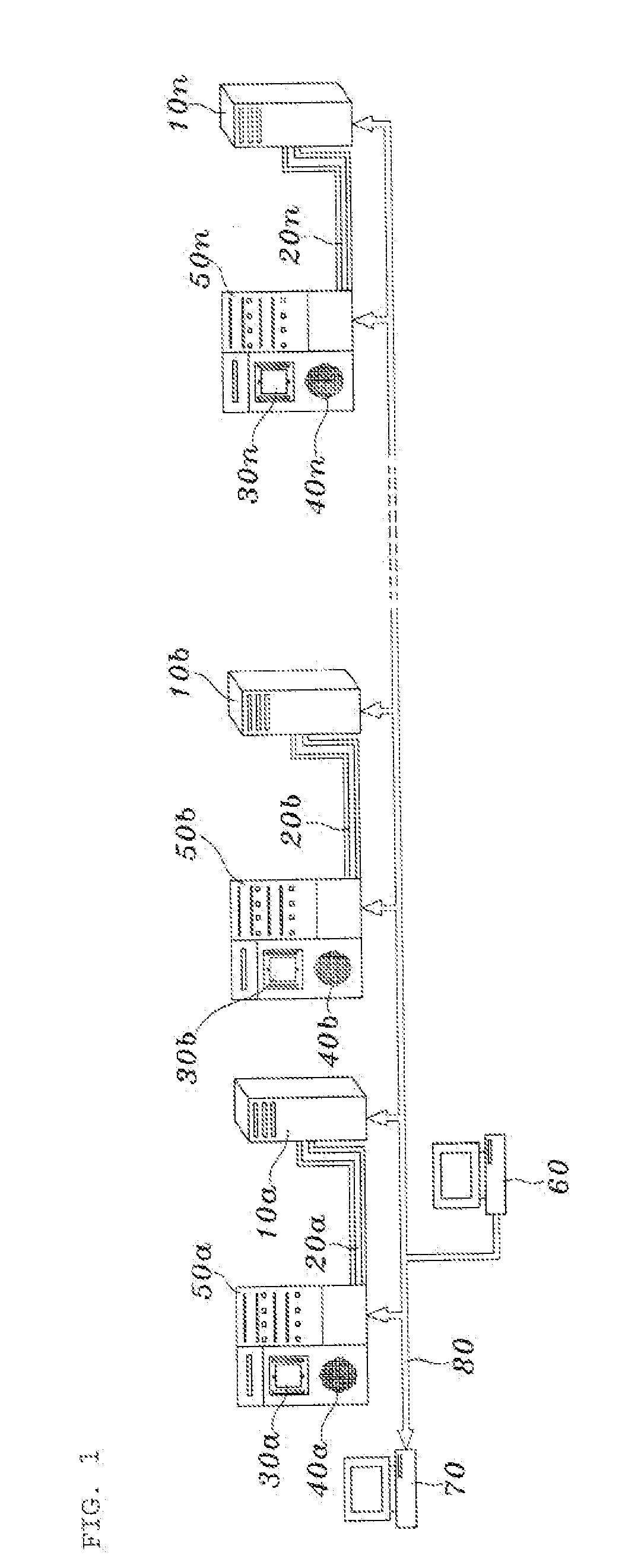

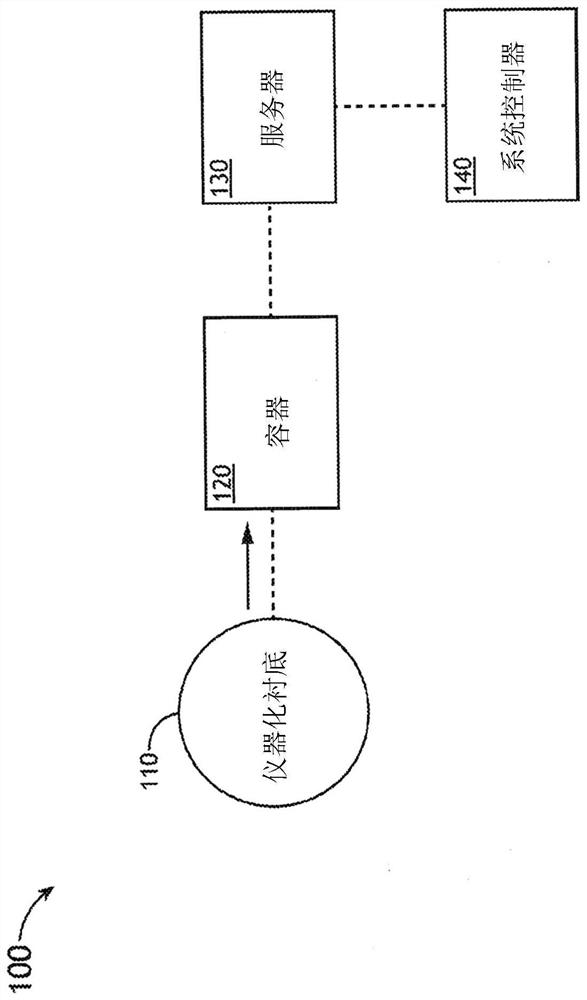

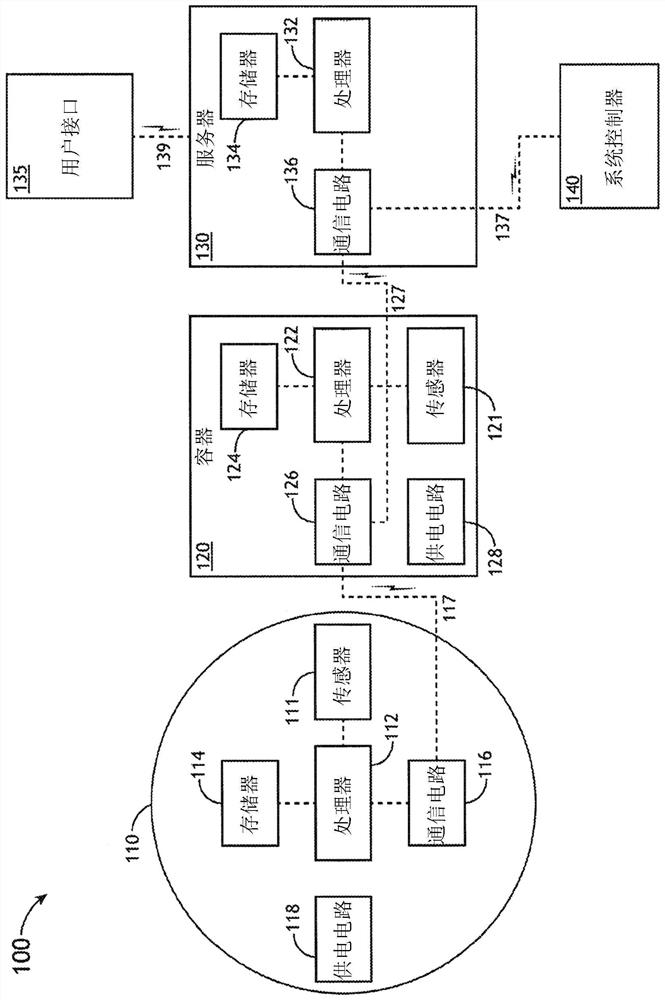

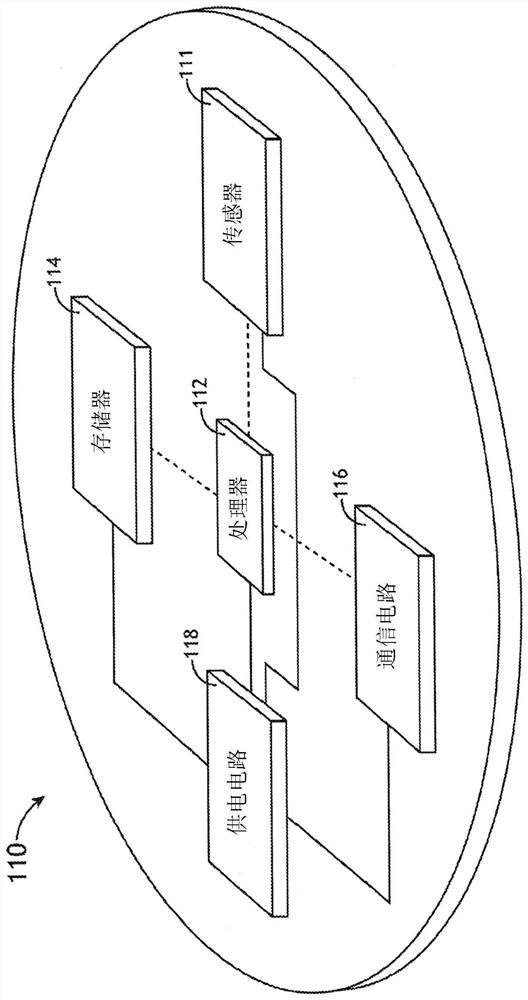

Systems and methods for monitoring parameters of semiconductor factory automation systems

ActiveCN107690604BSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingProcess engineeringSemiconductor factory

Owner:KLA CORP

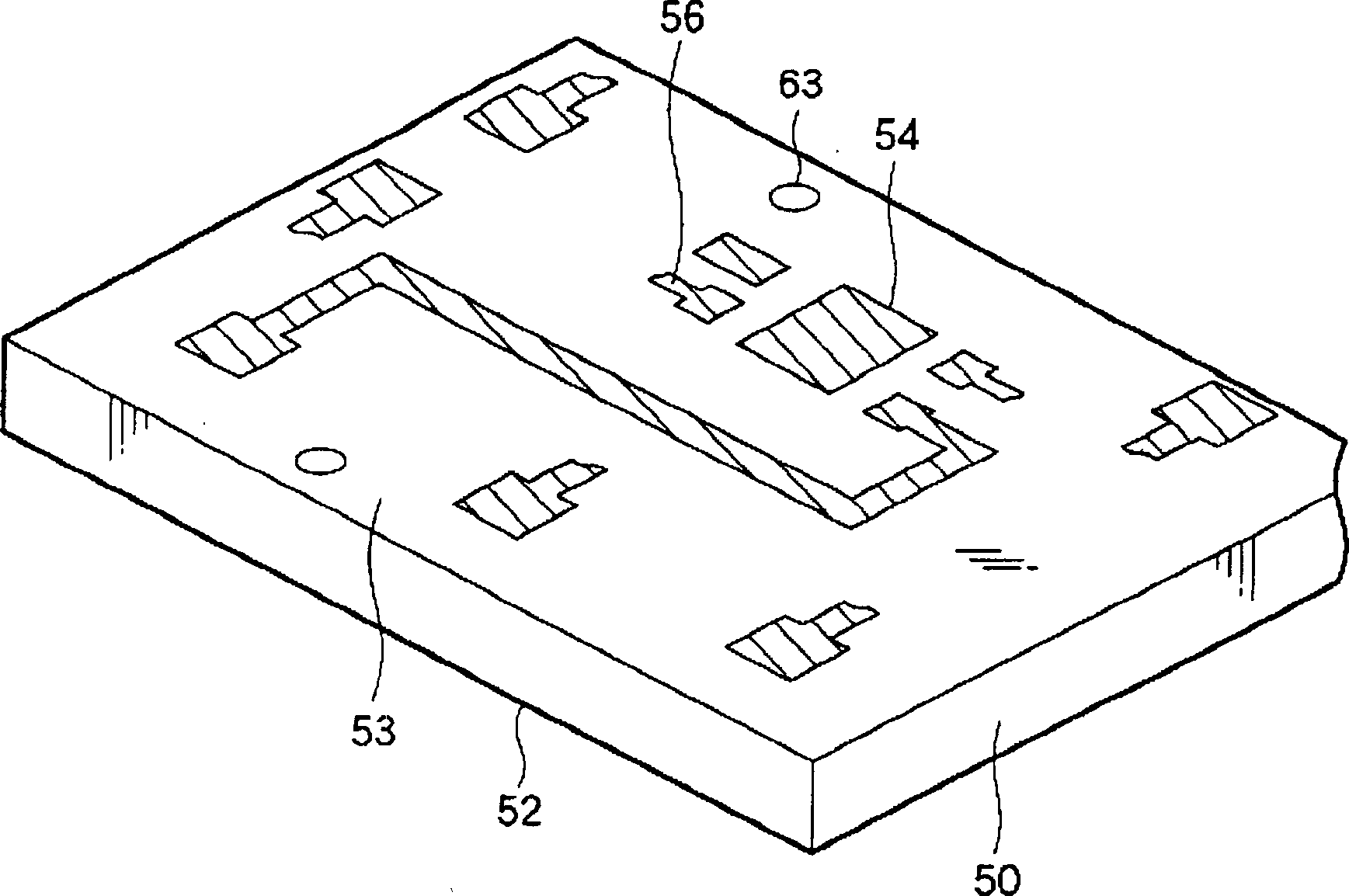

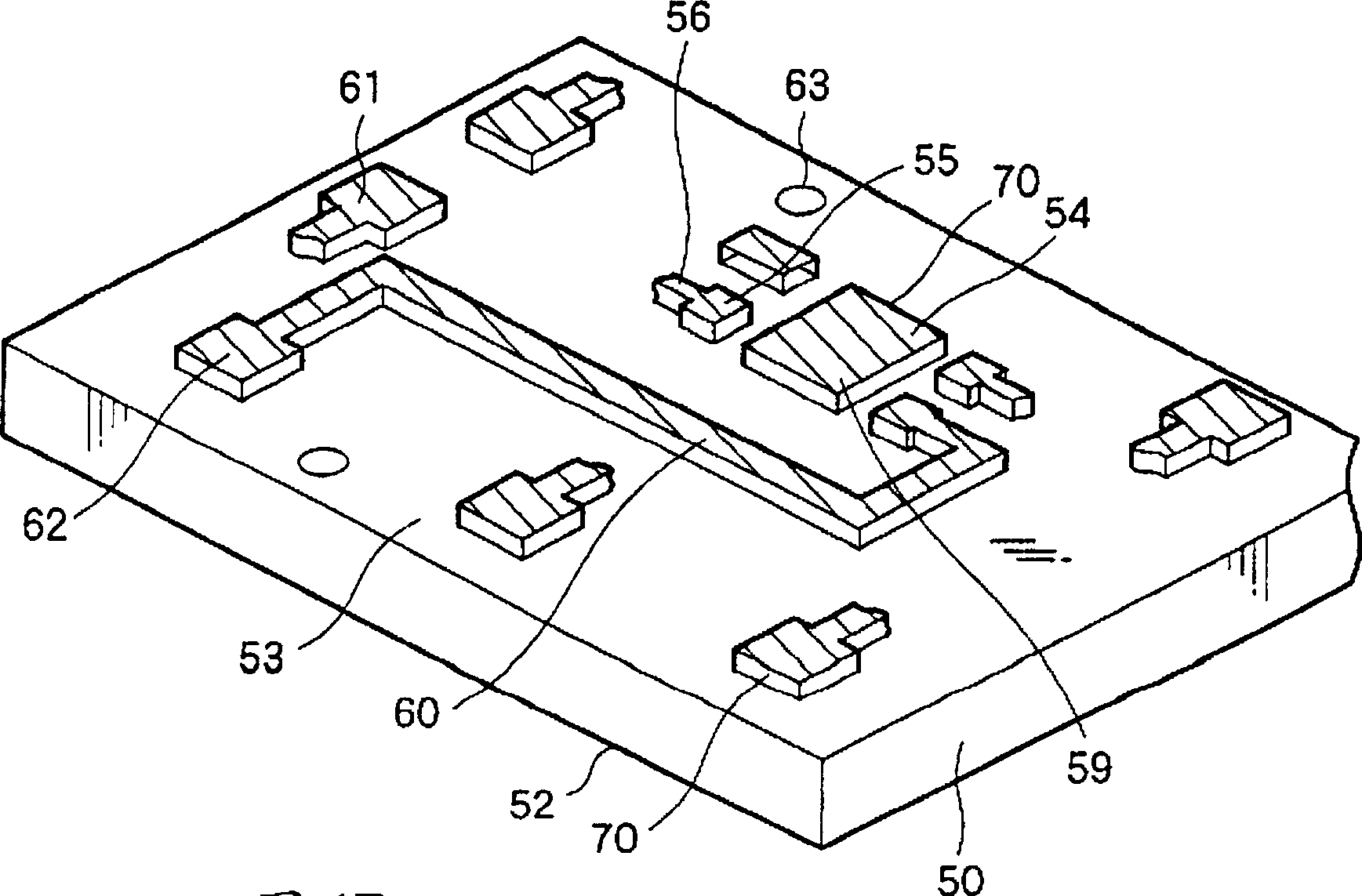

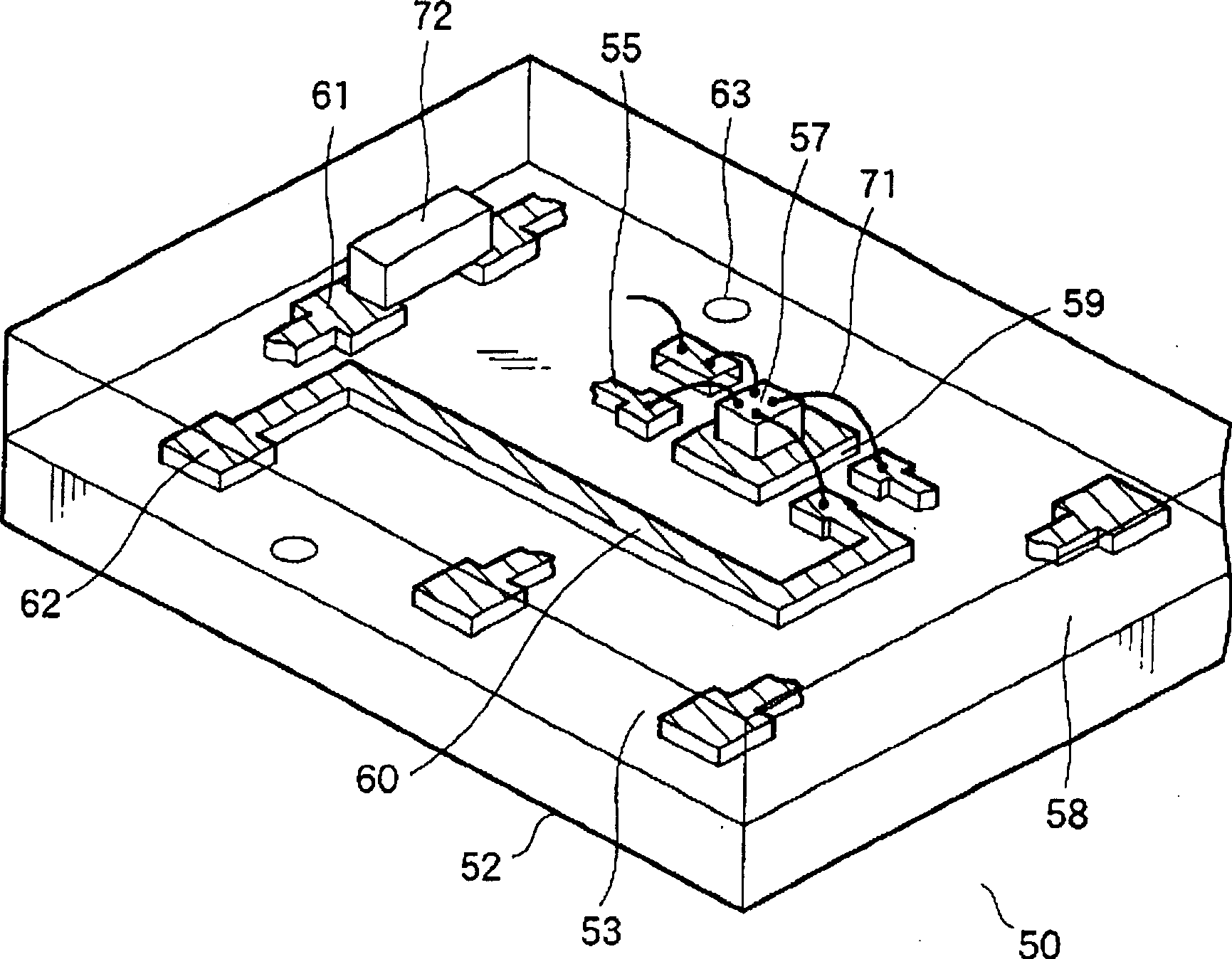

Method for producing plate shape body and semiconductor device

InactiveCN1237610CLower resistanceImprove surface flatnessPrinted circuit assemblingSemiconductor/solid-state device detailsConductive coatingEngineering

In the present invention there is formed a sheet-like board member 50 having conductive coating films, such as first pads 55 and die pads 59, formed thereon or a sheet-like board member 50 which has been half-etched by using conductive coating films such as first pads 55 and die pads 59. A hybrid IC can be manufactured by means of utilization of post-processing processes of a semiconductor manufacturer. Further, a hybrid IC can be manufactured without adoption of a support board, and hence there can be manufactured a hybrid IC which is of lower profile and has superior heat dissipation characteristics.

Owner:SANYO ELECTRIC CO LTD

Air filter

InactiveCN1233443CAvoid accumulationAvoid harmGas treatmentUsing liquid separation agentSolubilityAir filtration

An air filter device is connected with an external water supply device and an air pipeline to filter suspended particles in the passing gas, which includes: a cavity and a water curtain generator. The cavity has a plurality of nozzles connected to the external water supply device, which continuously sprays water mist into the cavity. The water curtain generator is socketed at the gas outlet of the cavity and connected to the external water supply device. The water curtain generator has a The annular opening is formed to form a first water curtain covering the gas outlet. The invention is suitable for filtering the corrosion exhaust gas produced by semiconductor factories, and can reduce submicron silicon particles and soluble corrosion gases in the exhaust gas, so as to avoid the accumulation of silicon particles in the exhaust pipes of semiconductor factories and increase pipeline maintenance. Cost, and reduce the suspended particles discharged from the exhaust port of the semiconductor factory, so as to avoid the air pollution caused by the submicron suspended particles discharged by it, which will cause harm to the human body.

Owner:MACRONIX INT CO LTD