Patents

Literature

110results about How to "Significant delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

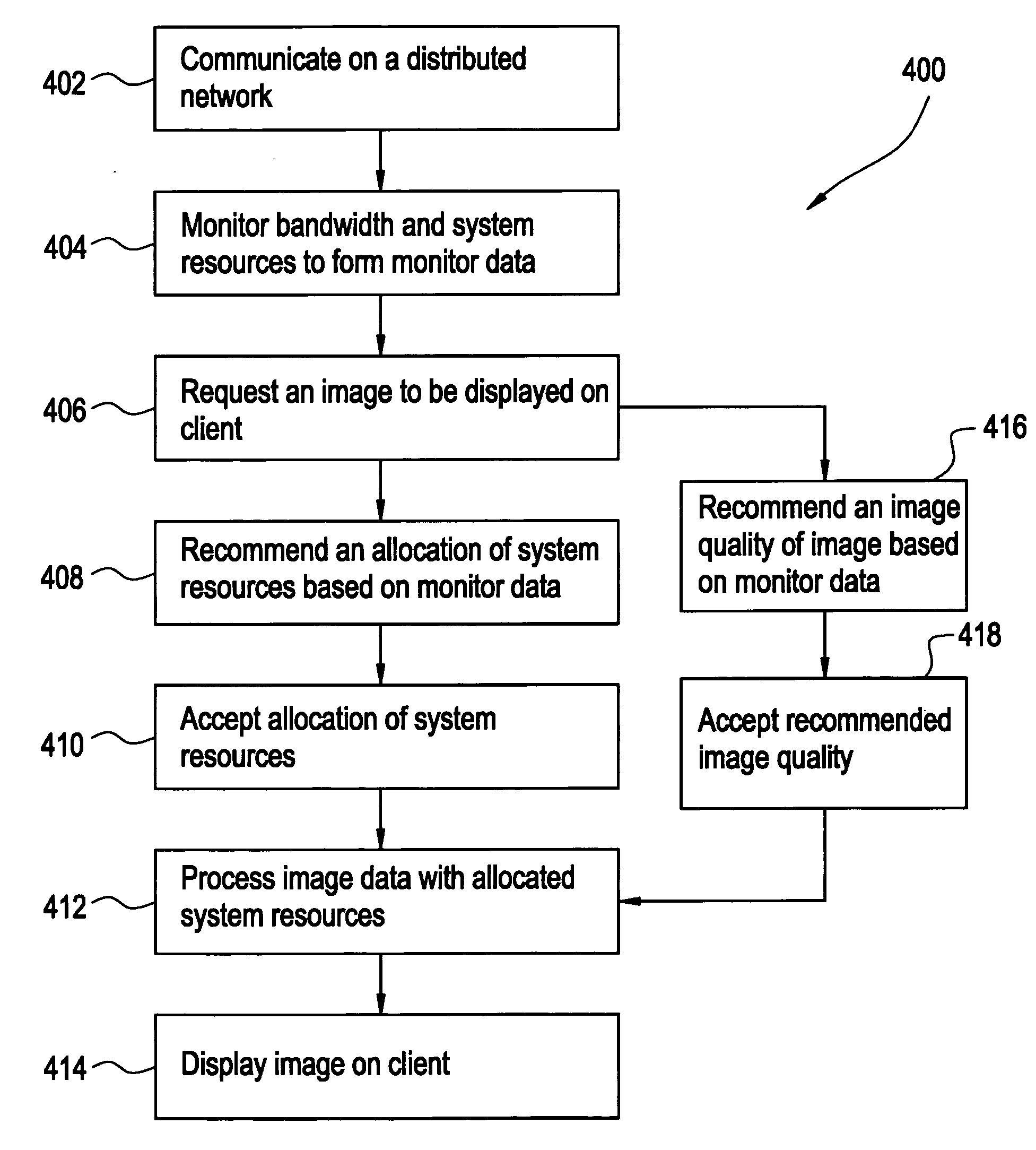

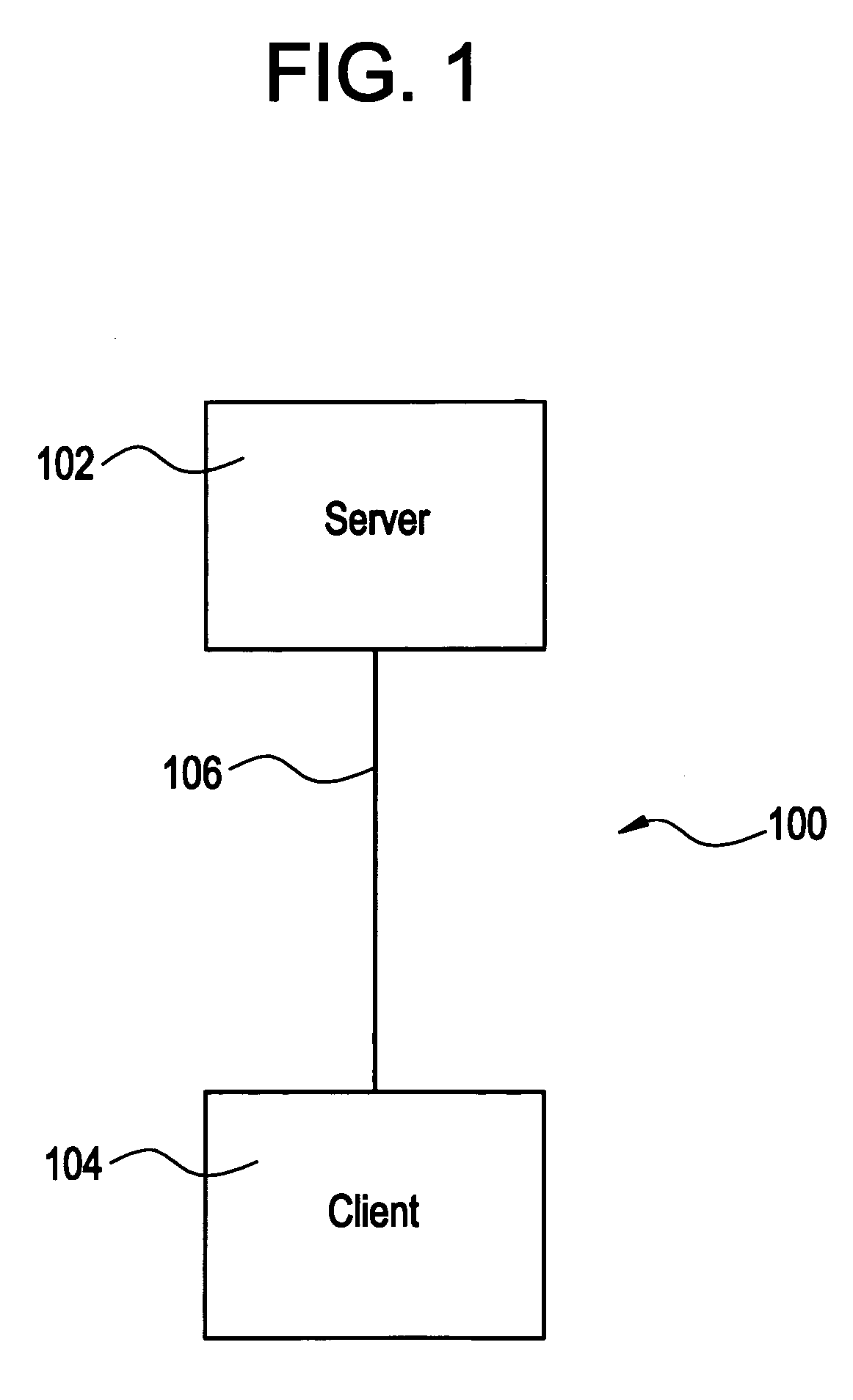

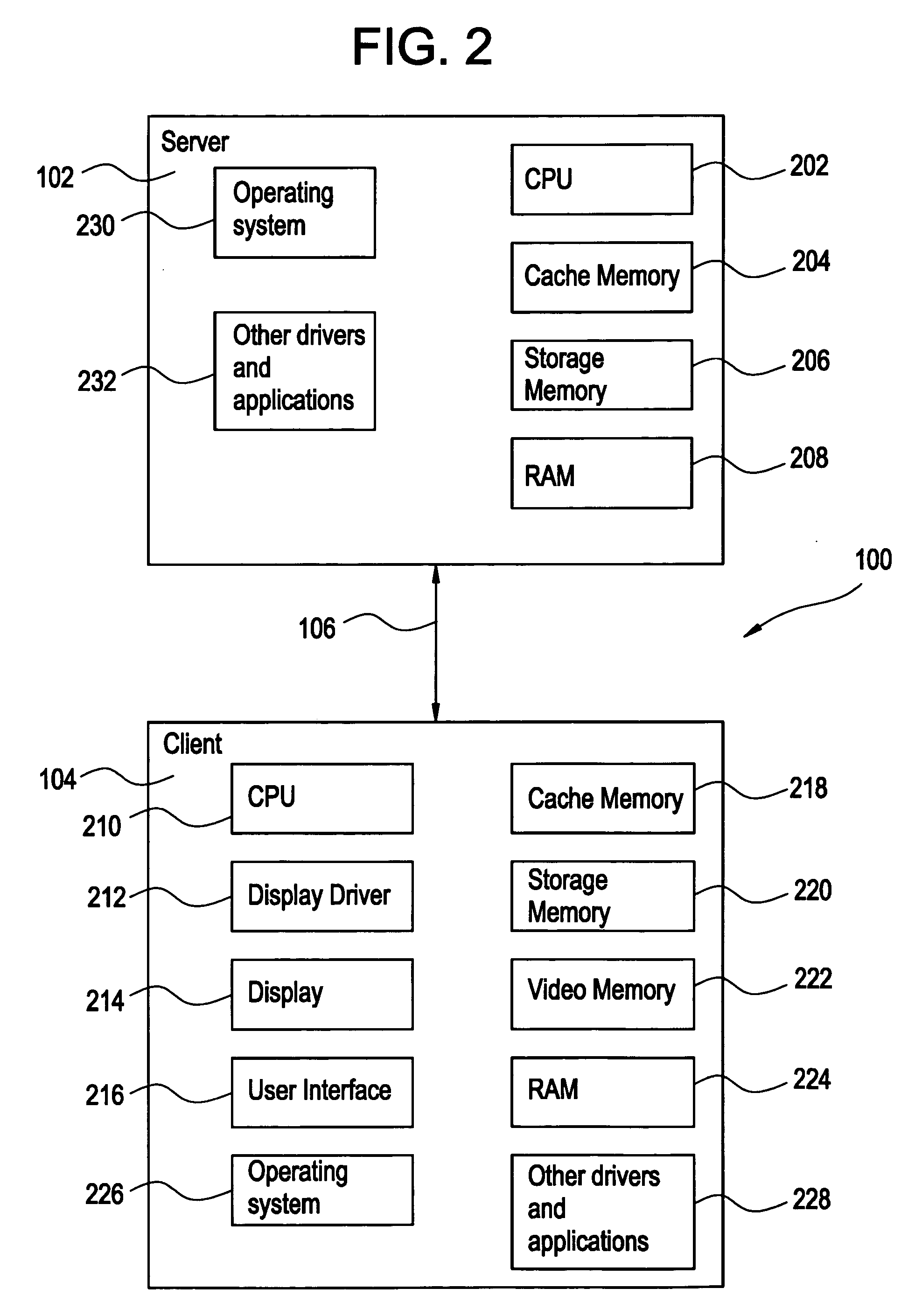

Distributed image processing for medical images

ActiveUS20070046966A1Significant delayProcessor architectures/configurationTransmissionClient-sideMonitoring data

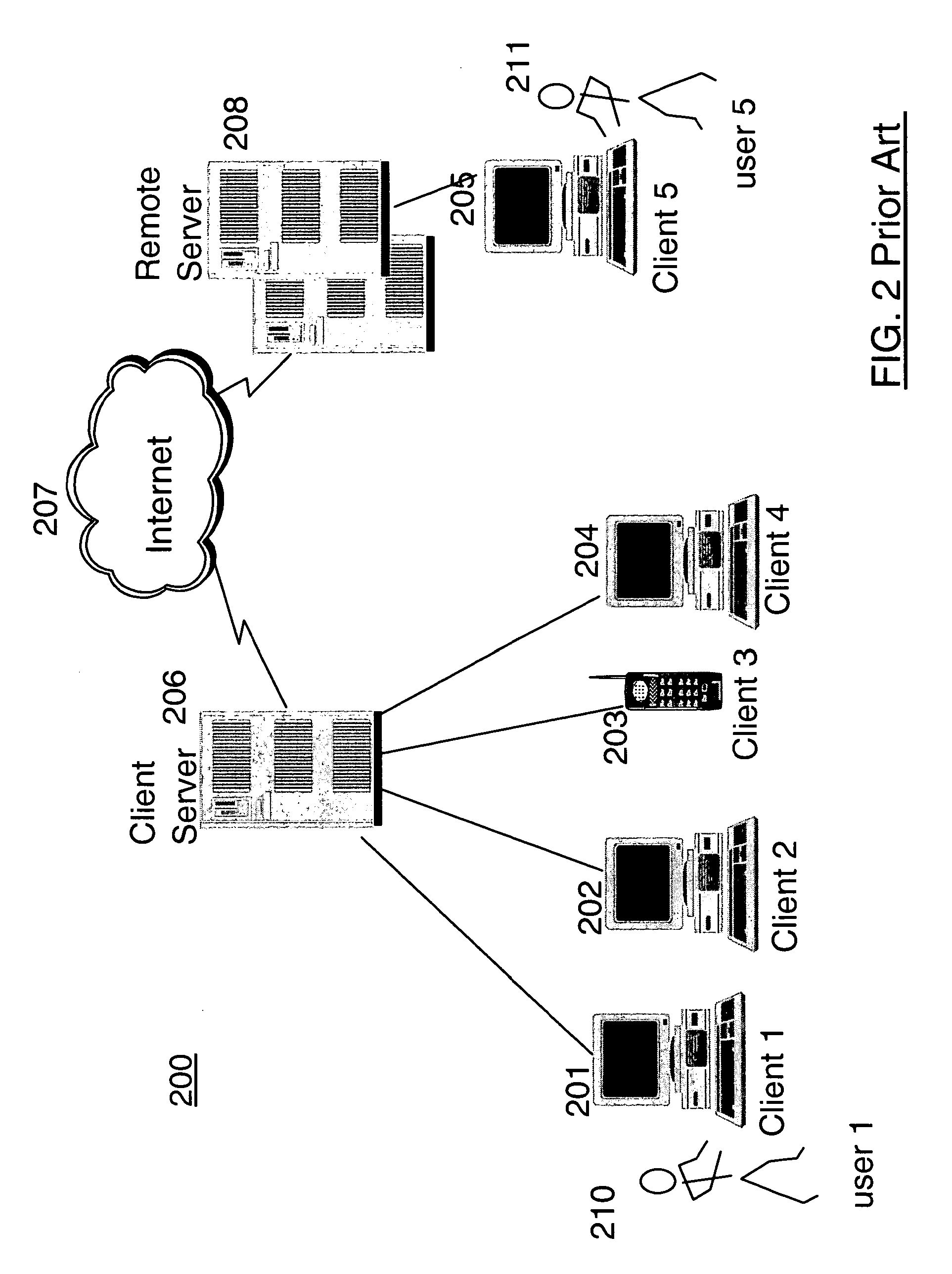

Certain embodiments of the present invention provide a method of medical image processing on a distributed network including: communicating on a distributed network comprising a server, a client, and a communications pathway having a bandwidth, wherein the distributed network comprises system resources related to the server, the client, and the communications pathway; monitoring the system resources and the bandwidth with at least one process monitor to generate monitor data; and recommending an allocation of at least a portion of the system resources for processing three dimensional image data to form two dimensional image data displayable on the client, wherein the allocation is based at least in part on the monitor data.

Owner:GENERAL ELECTRIC CO

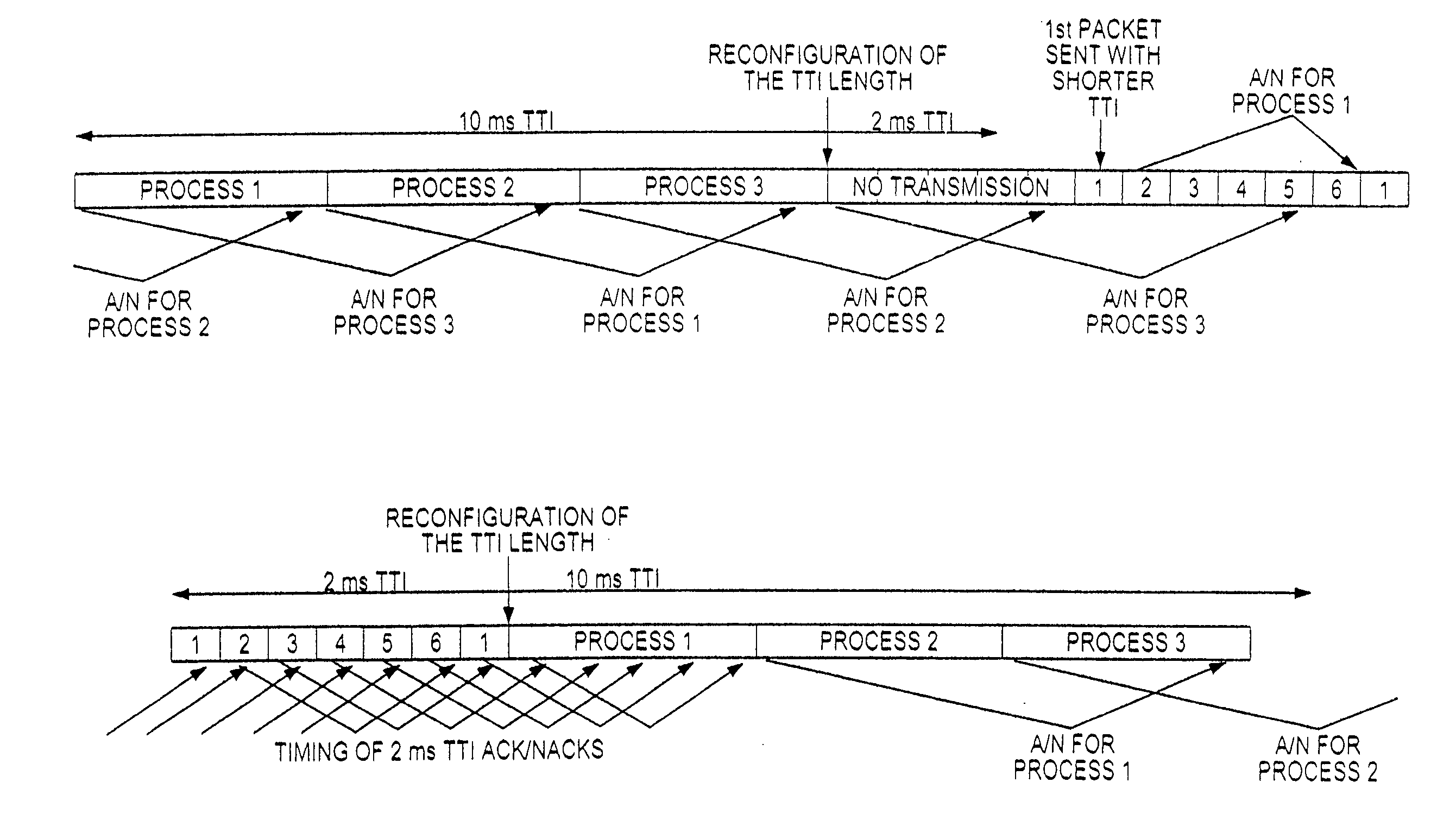

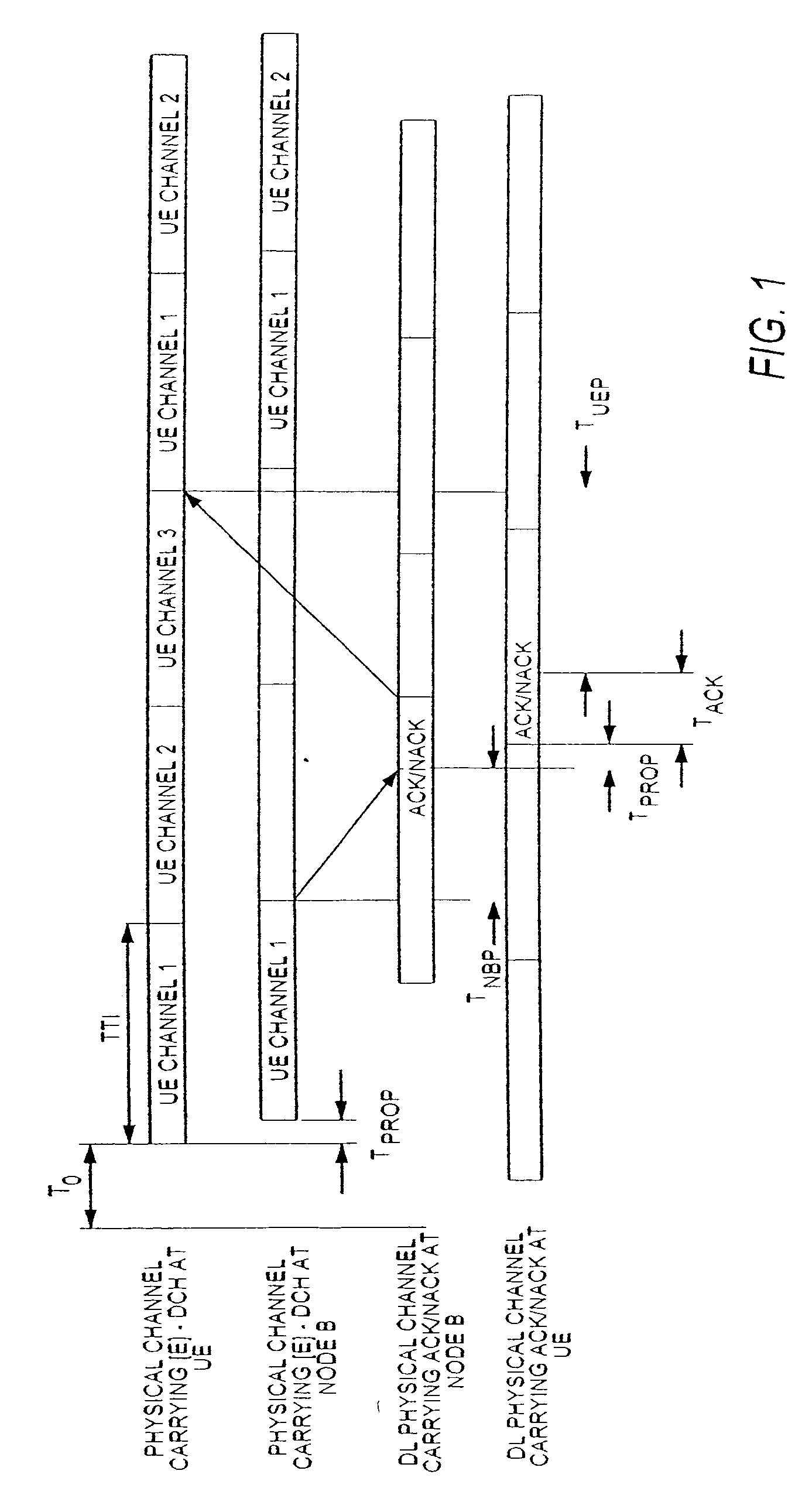

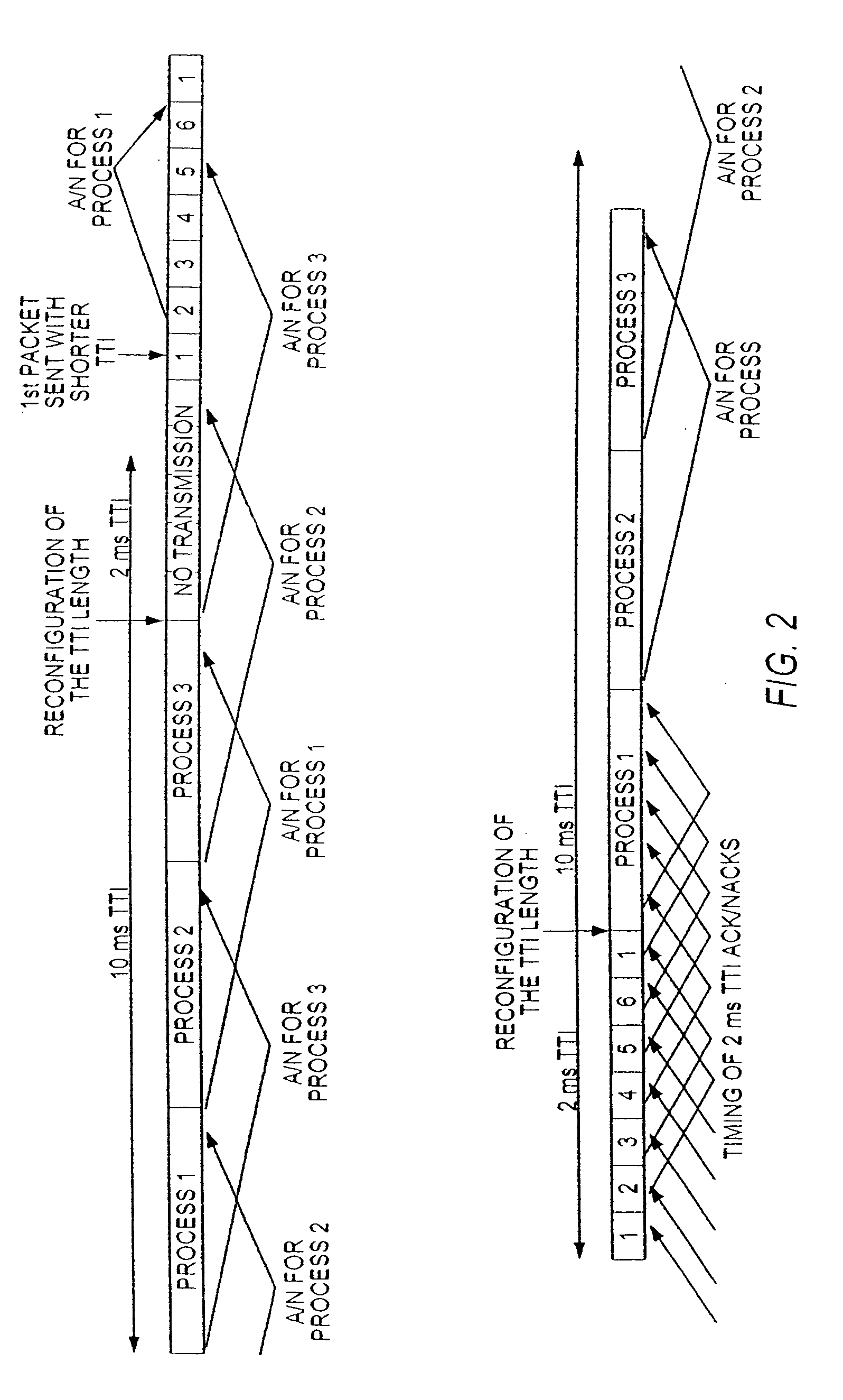

WCDMA uplink HARQ operation during the reconfiguration of the TTI length

ActiveUS20060034285A1Minimize dataLarge delayError prevention/detection by using return channelData switching by path configurationAir interfaceReal-time computing

A method for minimizing the loss of data and ensuring that large delays do not occur during reconfigurations of an uplink transmission time interval (TTI) length of a WCDMA High Speed Packet Uplink Access (HSUPA) air interface, wherein the reconfiguration of an uplink TTI length is delayed until all pending retransmissions are successfully transmitted or until the maximum number of transmissions is reached. The transmission of new packets during this time period is prevented. However, pending retransmissions are allowed to occur. After the UE has received an ACK / NACK for each HARQ process, or until the specific maximum number of re-transmissions is reached, the UE starts transmitting with a new uplink TTI length.

Owner:NOKIA TECHNOLOGLES OY

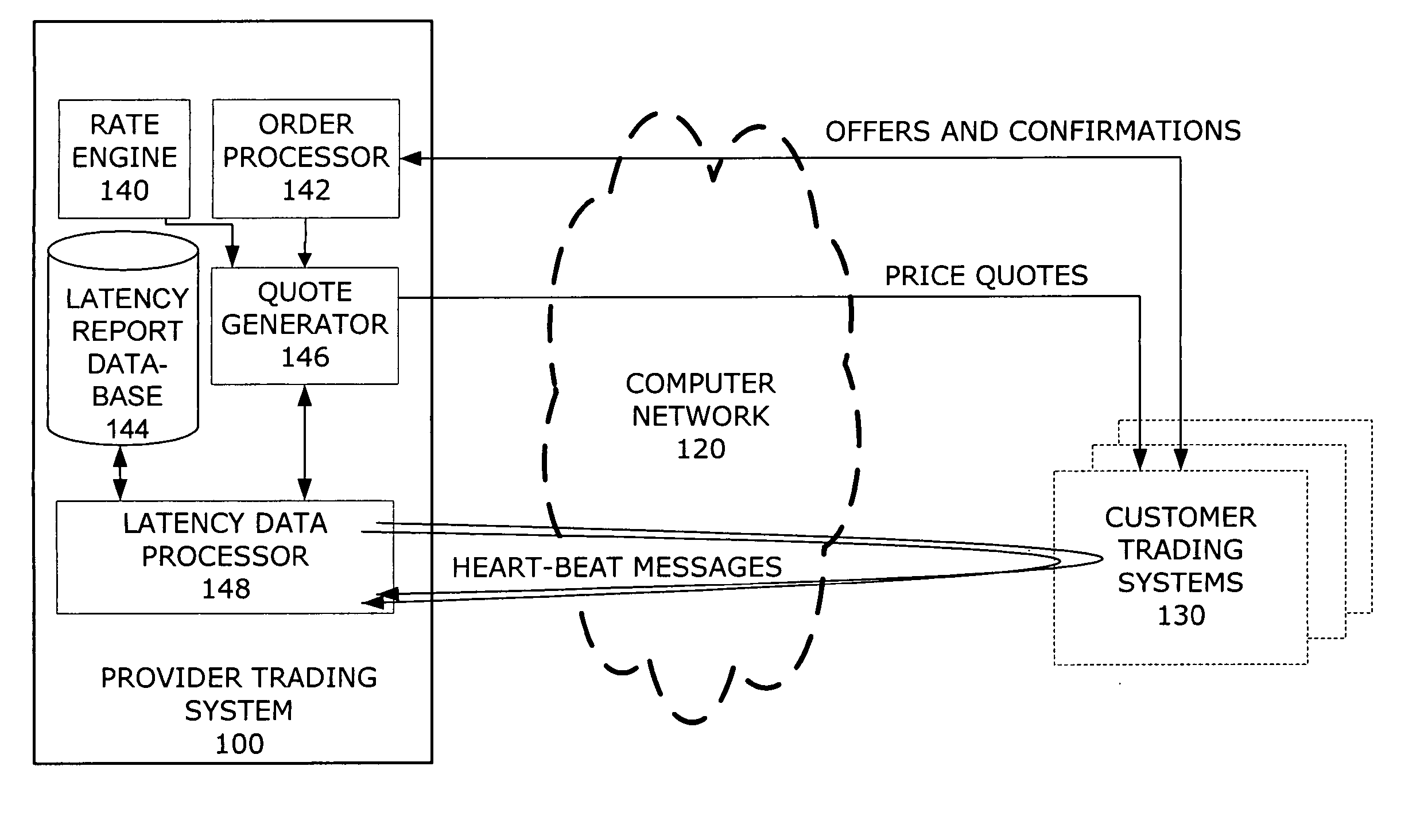

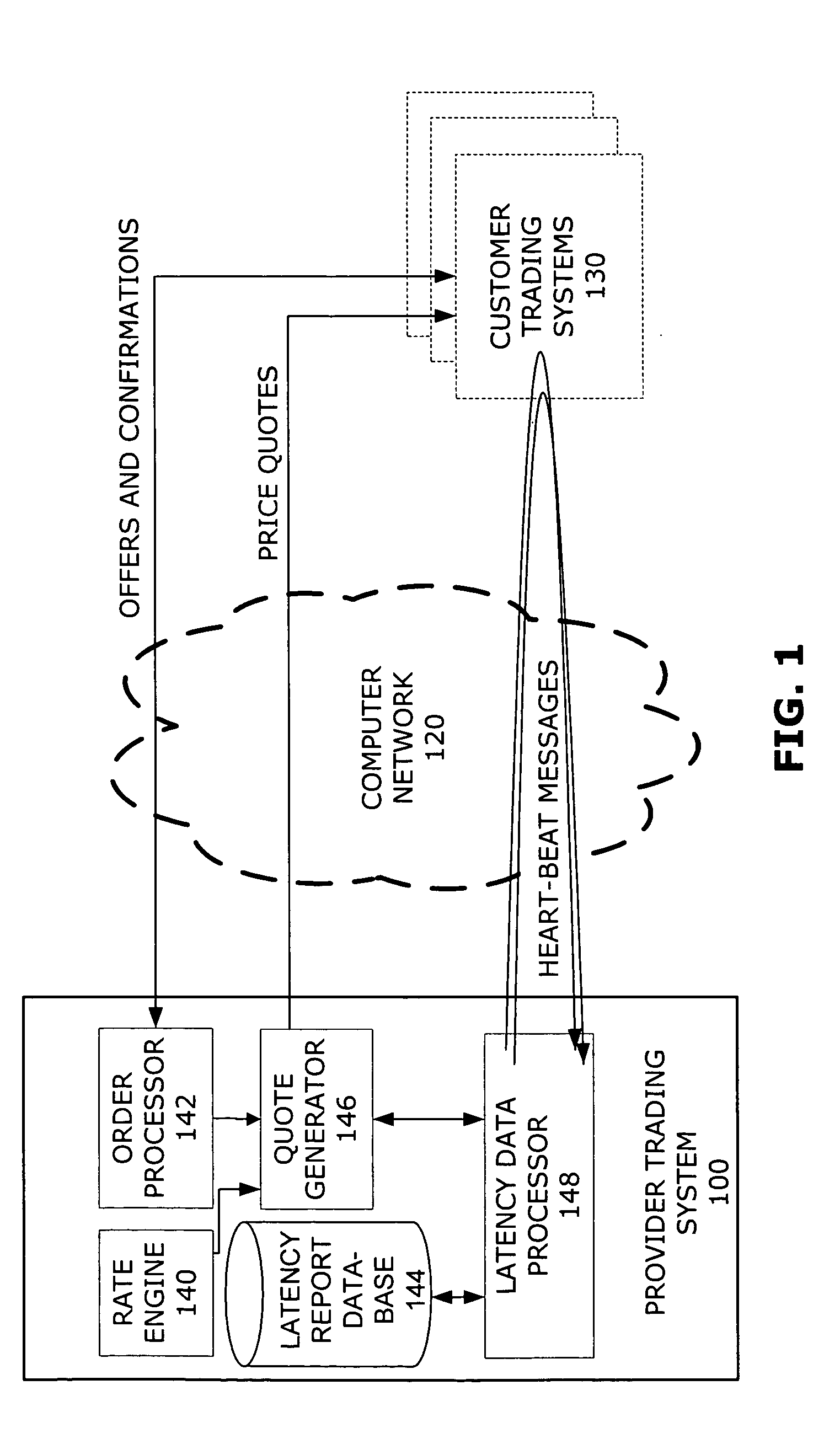

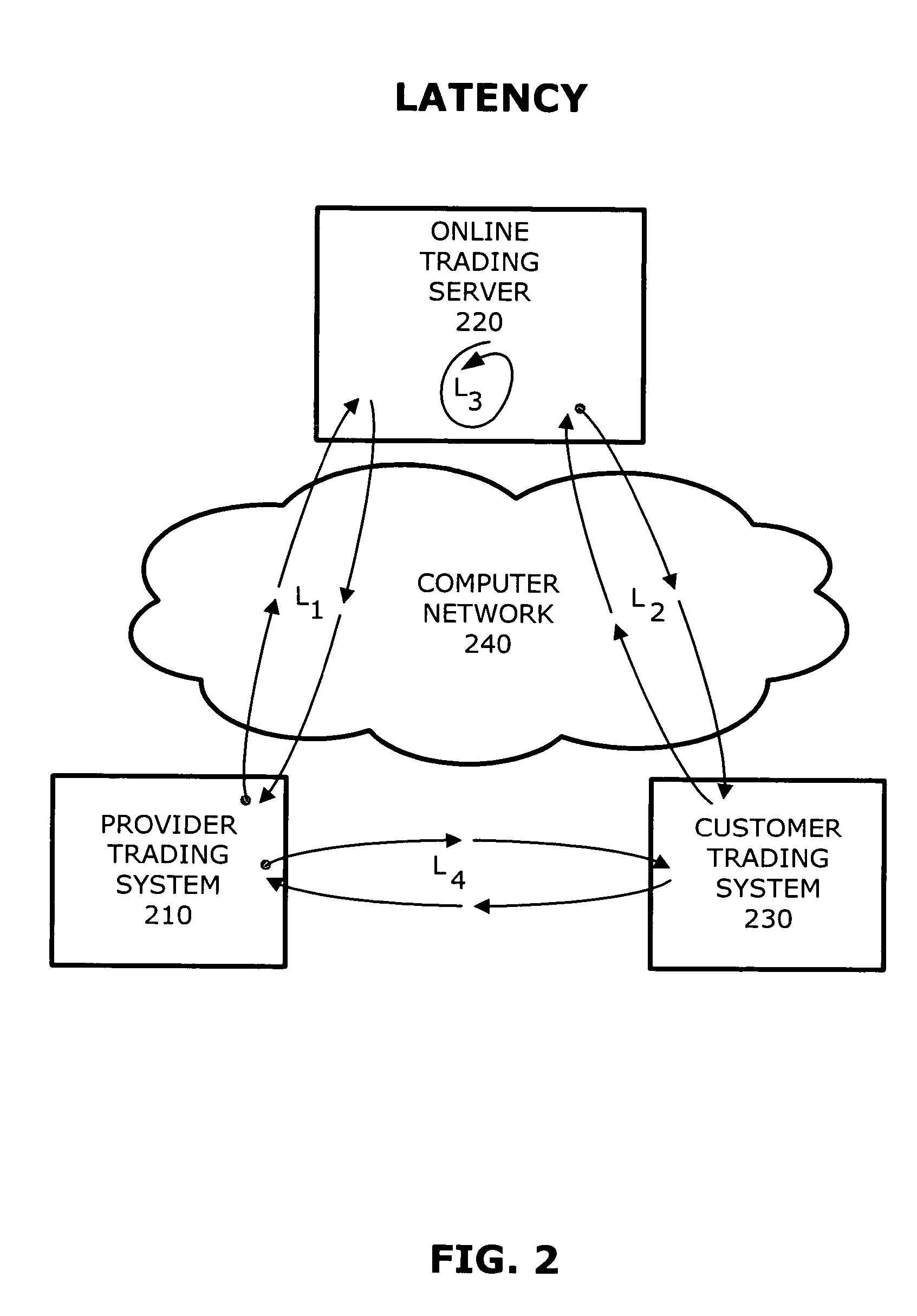

Latency-aware asset trading system

InactiveUS20050137961A1Significant delayHigh frequencyFinanceSpecial data processing applicationsPrice quoteOnline trading

An online trading system for providers, customers and online trading servers, as well as methods of conducting online trading transactions, that incorporate processing components and steps that measure, monitor, report and utilize up-to-date network latency data to process offers to deal so that an unnecessarily large number of deals will not be refused. The systems and methods may also be used to make adjustments to the frequency and content of price quotes, based on current latency data, to improve customers' opportunity to submit offers that will arrive timely. The invention provides banks (and other liquidity providers), as well as online trading server operators, with sufficient information concerning network latencies so that price quotes issued by the banks can be “tuned” and customized so that they will not expire before the bank's customers have a reasonable opportunity to review the price quotes and submit offers to deal.

Owner:FX ALLIANCE

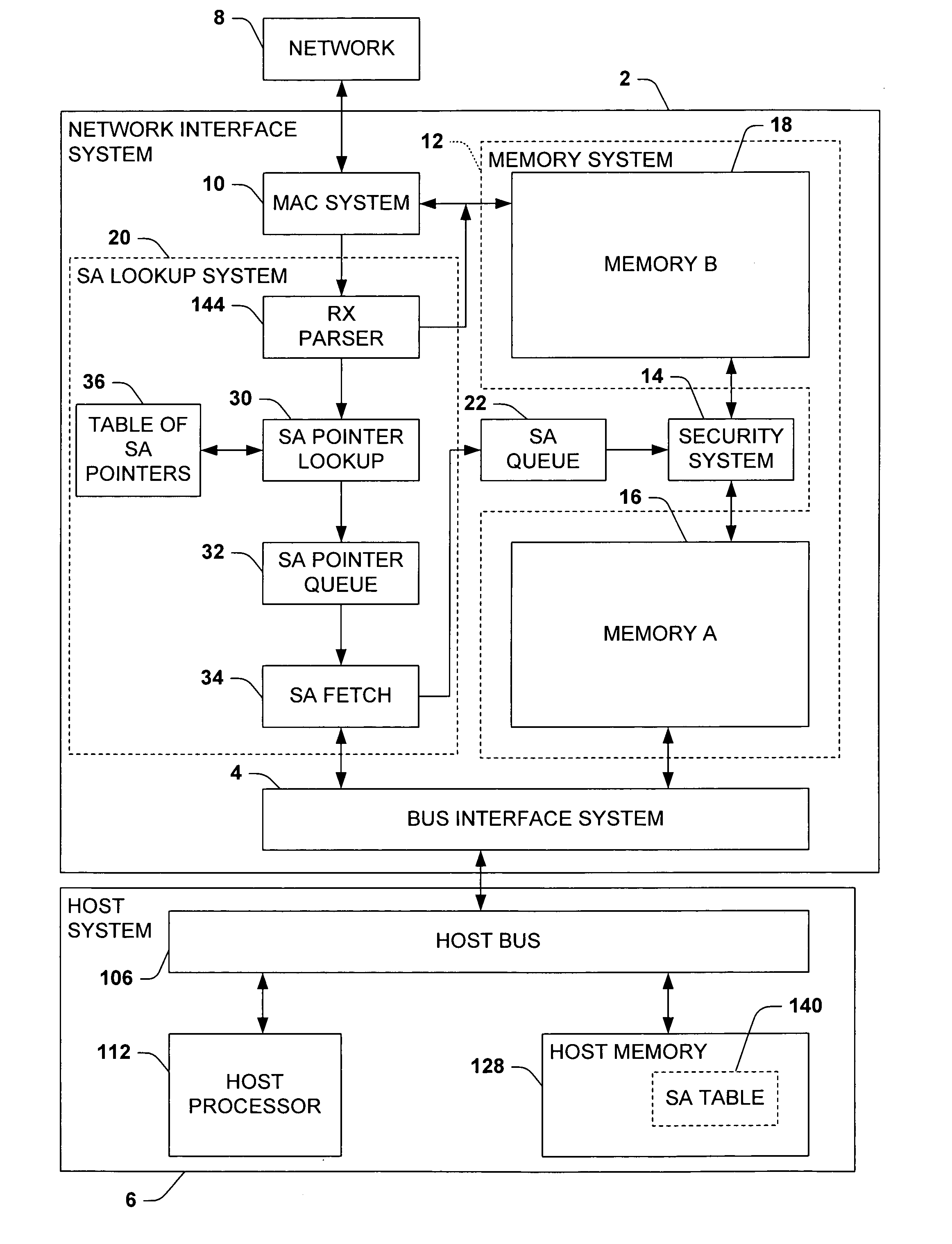

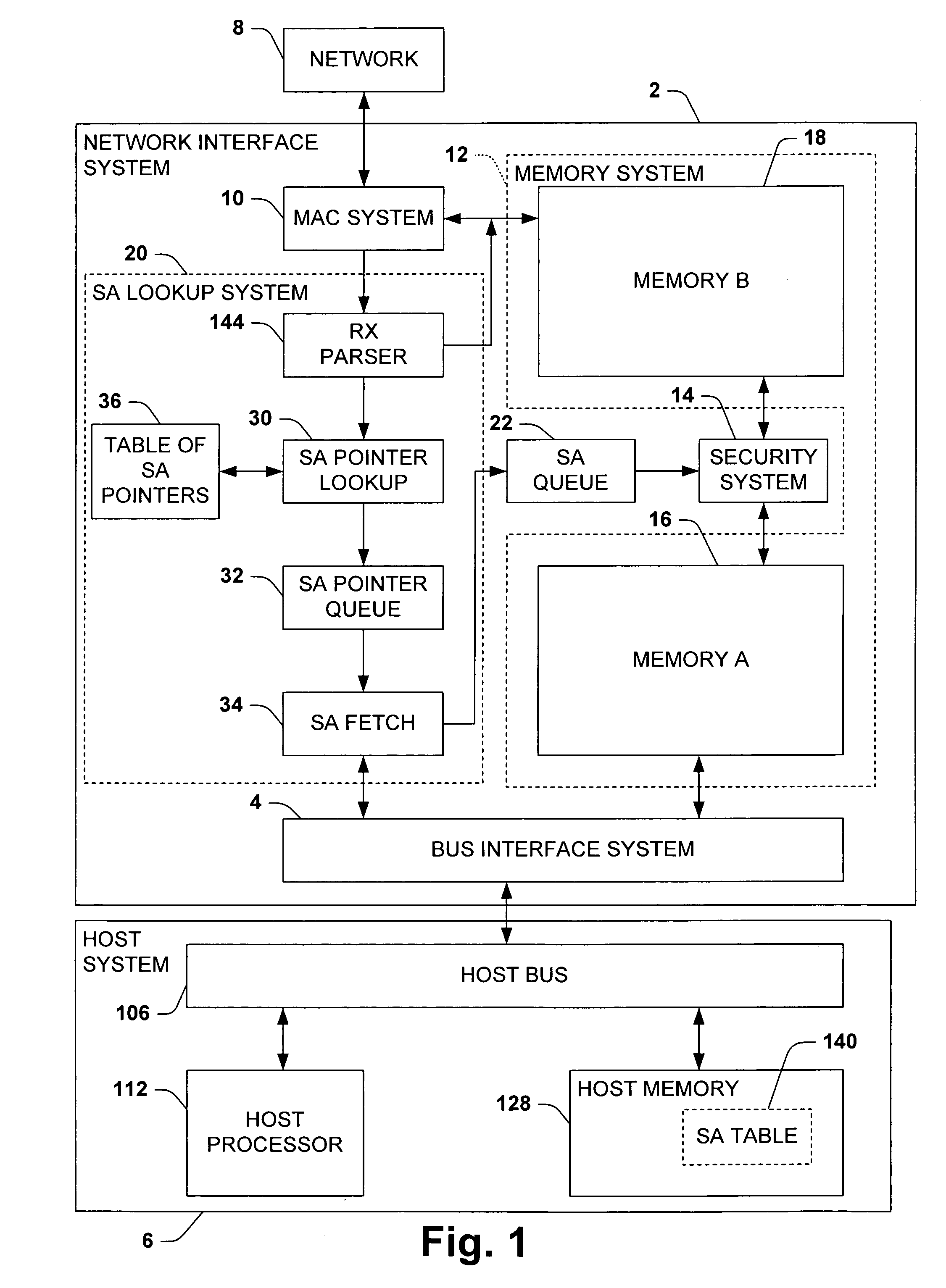

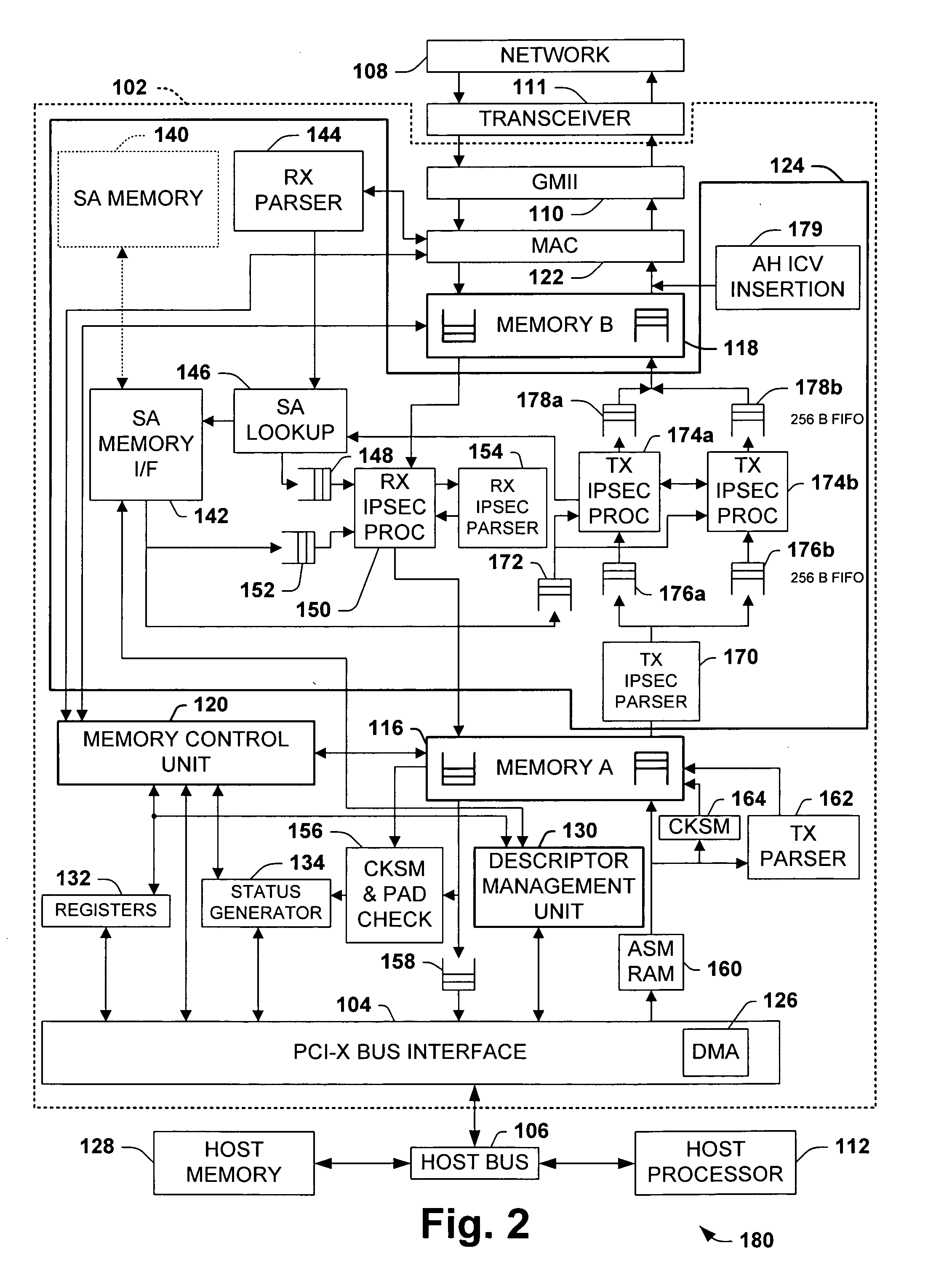

Network interface with security association data prefetch for high speed offloaded security processing

ActiveUS20050256975A1Facilitates high speed security processingTo overcome the large delayMultiple digital computer combinationsData switching networksExternal storageSecurity association

One aspect of the invention relates to a network interface system for interfacing a host system with a network. The network interface system includes a bus interface system, a media access control system, and a security system. The security system selectively perform security processing on data incoming from the network based on security associations stored in a memory external to the network interface system, typically a host system memory. The security association for any given frame, when available, is fetched from the external memory after the frame begins to arrive in the network interface system based in part on information contained in the frame. Preferably, the fetch begins before the frame is fully received and the security association is queued whereby security processing can begin without having to wait for the security association to be fetched.

Owner:MEDIATEK INC

Methods of controlling transmission power levels in air interface channels

InactiveUS20050163070A1Reduce noise levelQuality improvementPower managementTransmission control/equalisingQuality of serviceFrequency spectrum

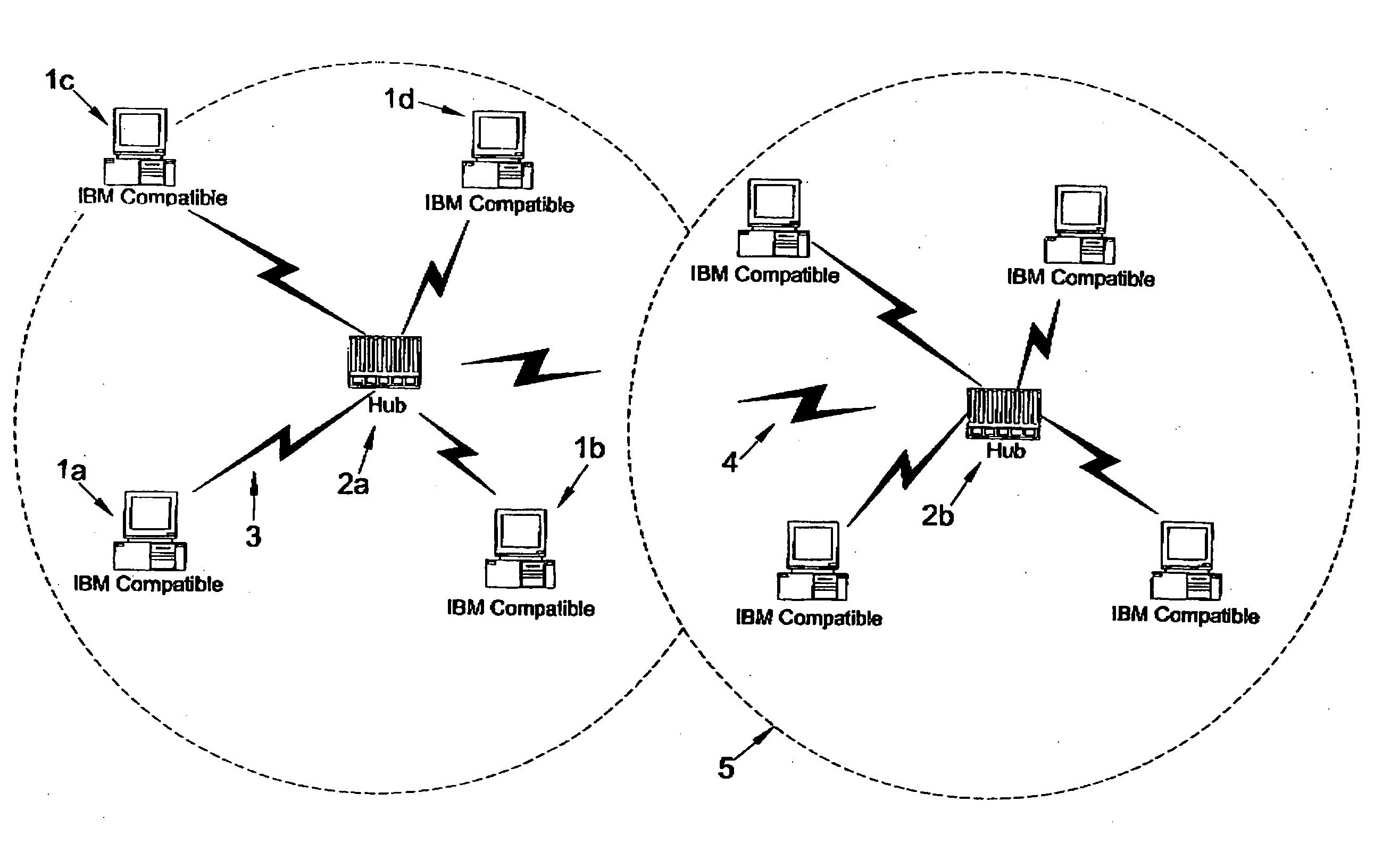

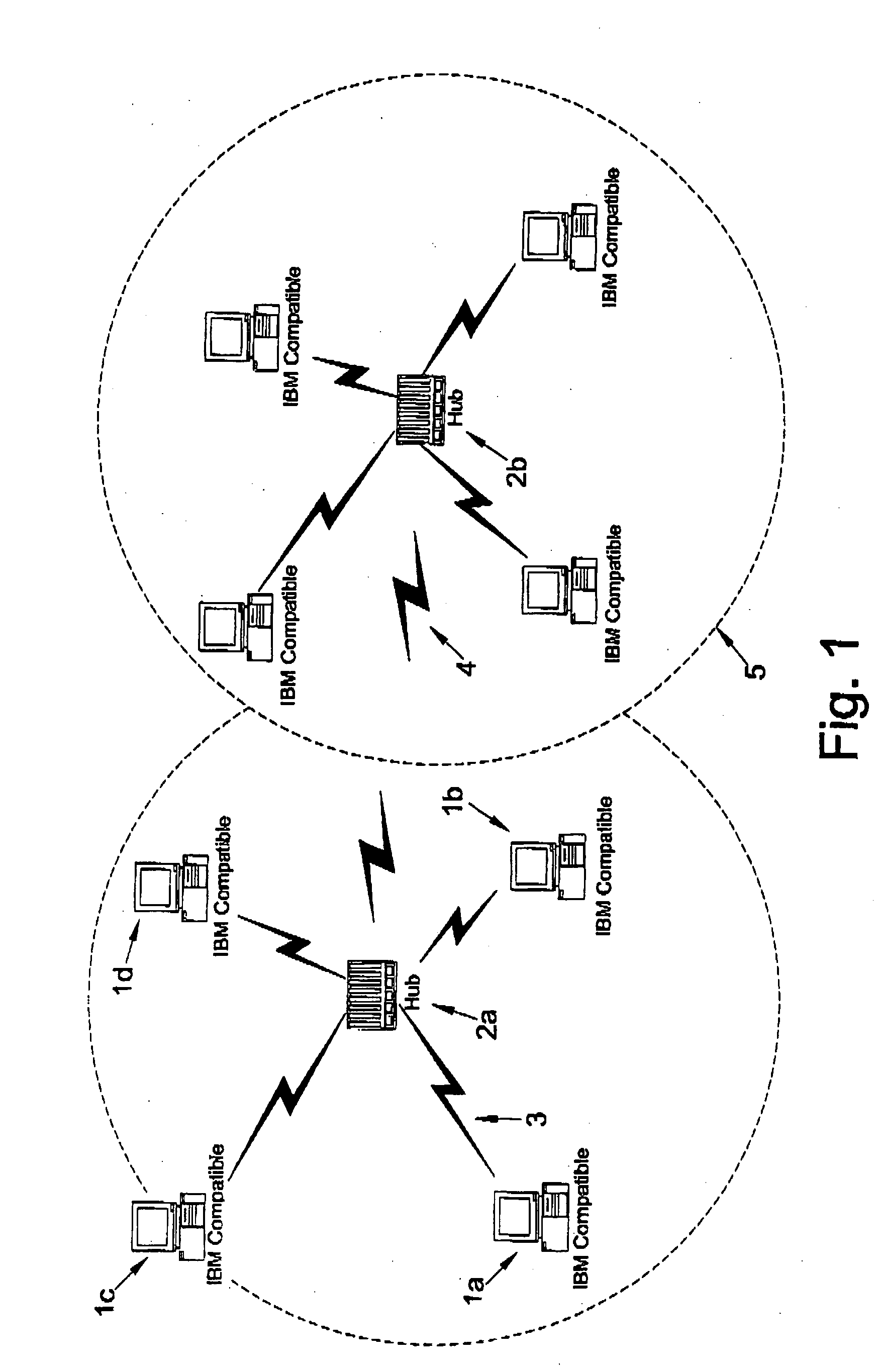

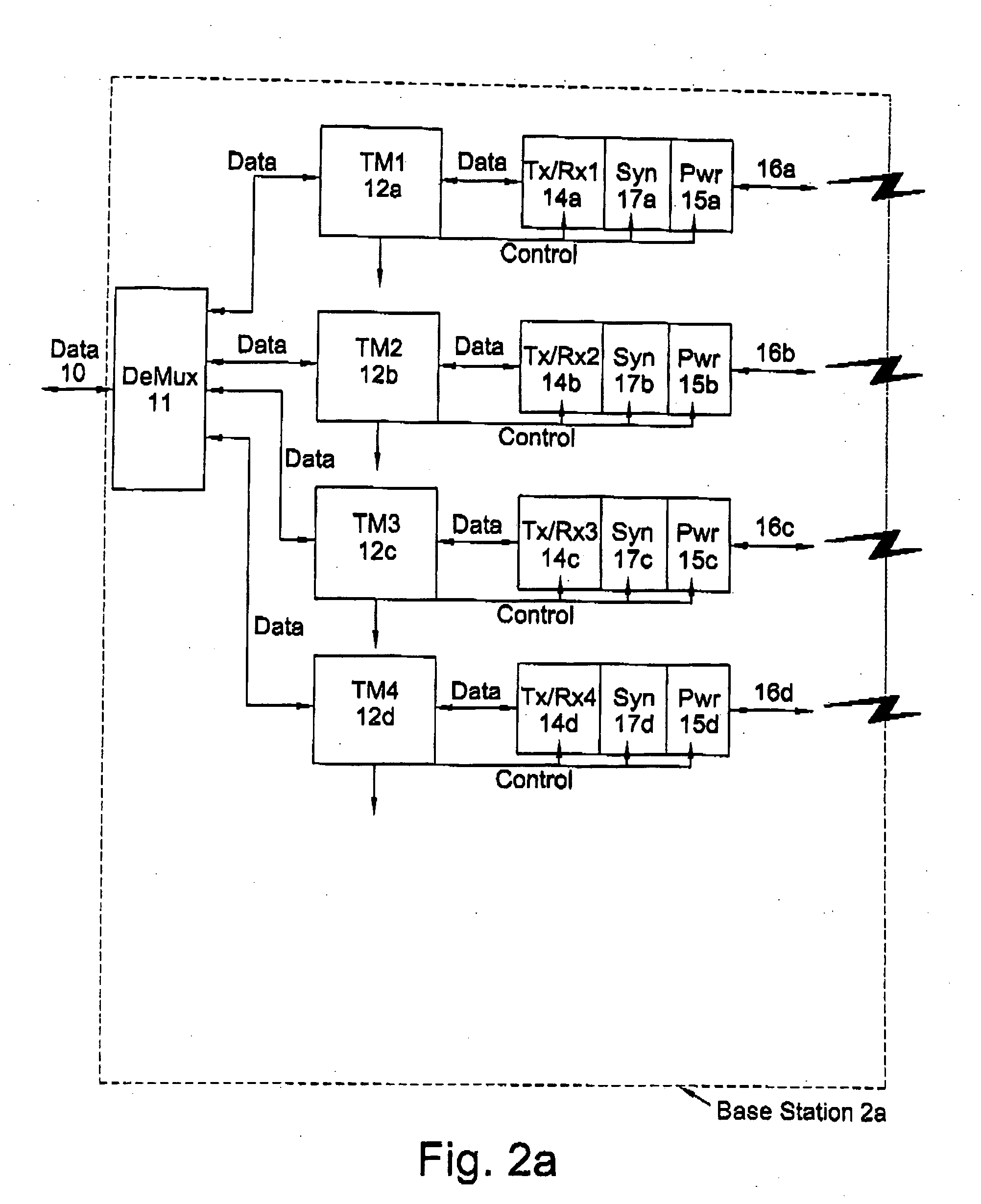

The present invention relates to wireless communications, and in particular although not exclusively, to networks of indoor collocated or overlapping wireless coverage areas especially those intended for operation in unlicensed spectrum such as the Industrial Scientific and Medical (ISM) bands. The present invention provides a method of controlling the transmission power associated with an air interface channel, the method comprising determining a quality of service measure for a signal to be transmitted on a second air interference channel; determining an interference measure corresponding to the interference on said second air interface channel which will be caused by transmissions on said first air interface channel; requesting the changing of the transmission power associated with the first air interface channel when the signal is to be transmitted on the second air interface channel, when the quality of service measure is above a predetermined value and when the interference measure is above a predetermined value for said quality of service value.

Owner:KK TOSHIBA

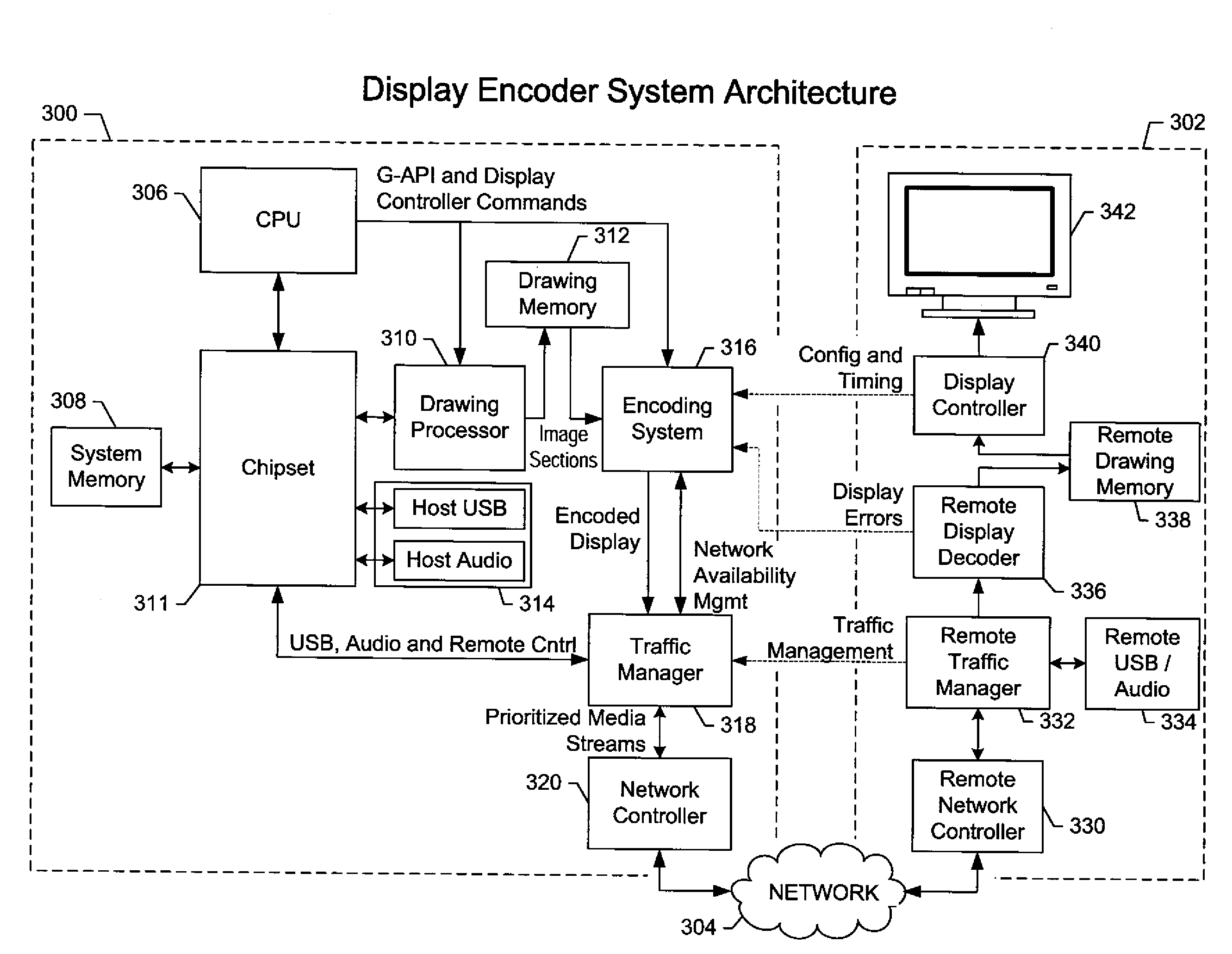

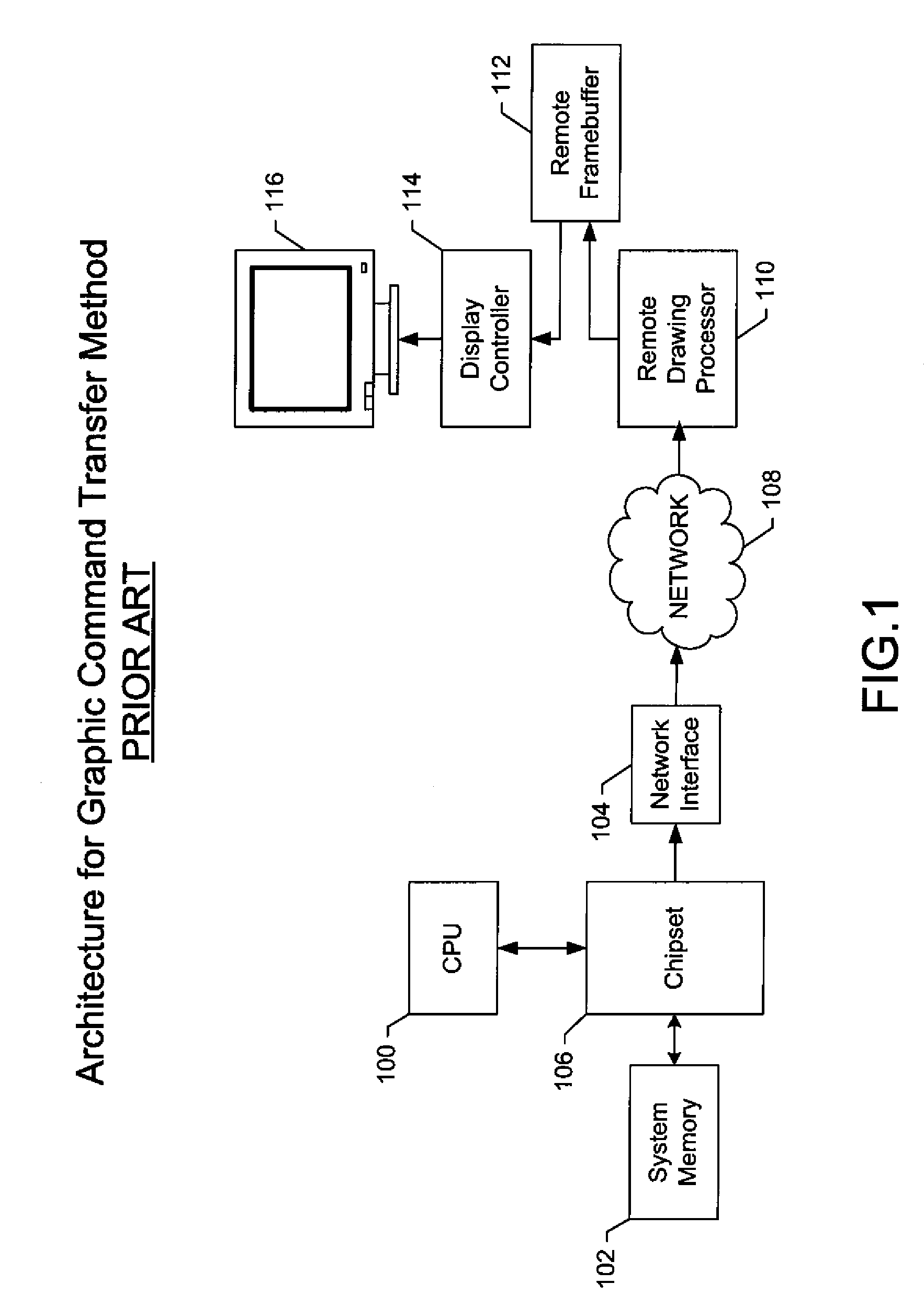

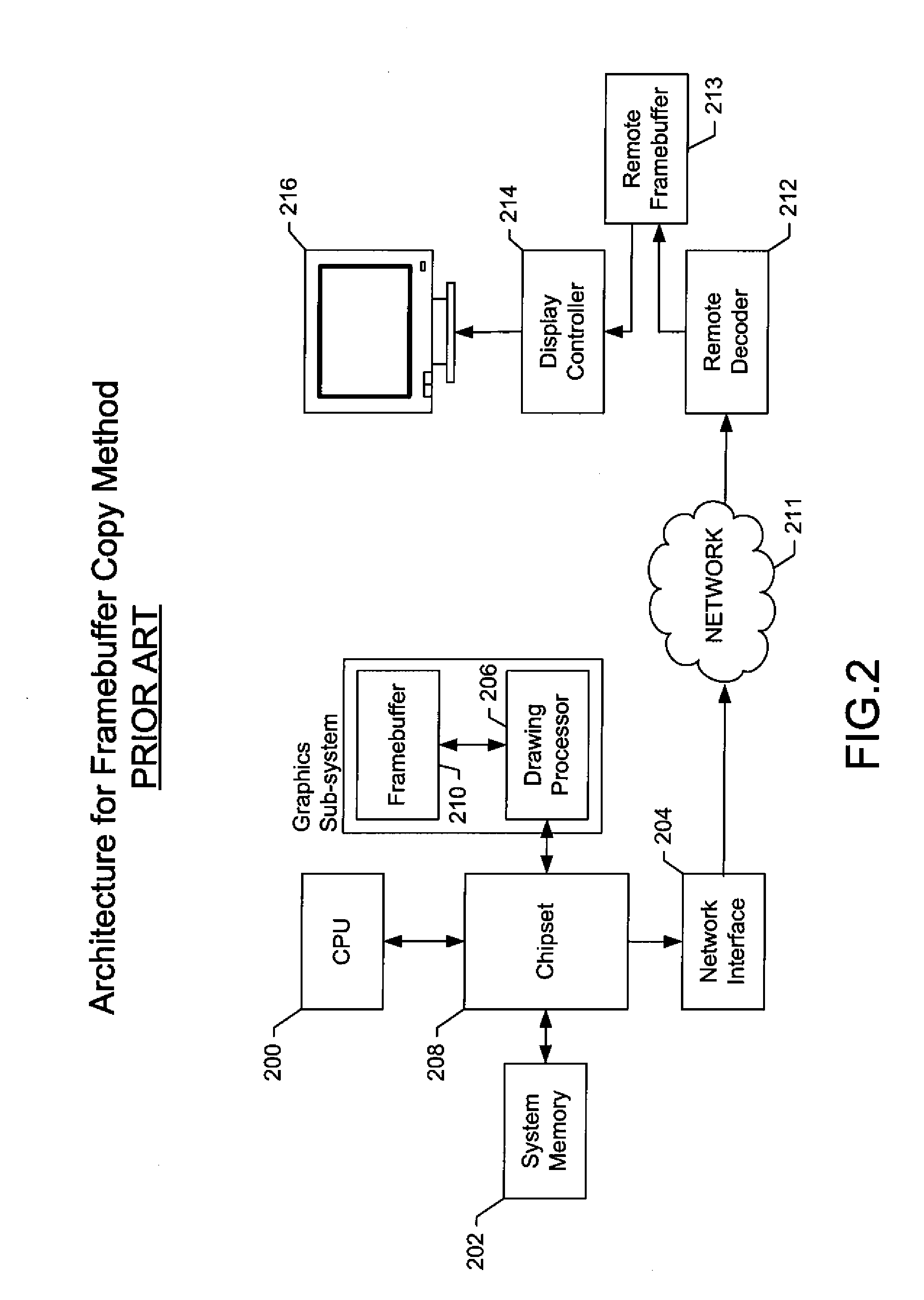

Methods and apparatus for interfacing a drawing memory with a remote display controller

ActiveUS7430681B1Adapt quicklyLatency from when the image is drawnError detection/correctionData resettingClient-sideComputer science

A method of transmitting encoded computer display images between computers over a nondeterministic network is disclosed. During a display session in which images are transmitted from a host to a client, the client requests sections of encoded image updates at a predetermined time in advance of when the requested at least one section is to be transmitted by the display controller. When the requested section is received, a time value is compared to a display controller timing value and, if the difference between the compared times is outside of an acceptable range, the client adjusts a predetermined time at which time the client requests image sections from the host.

Owner:TERADICI CORP

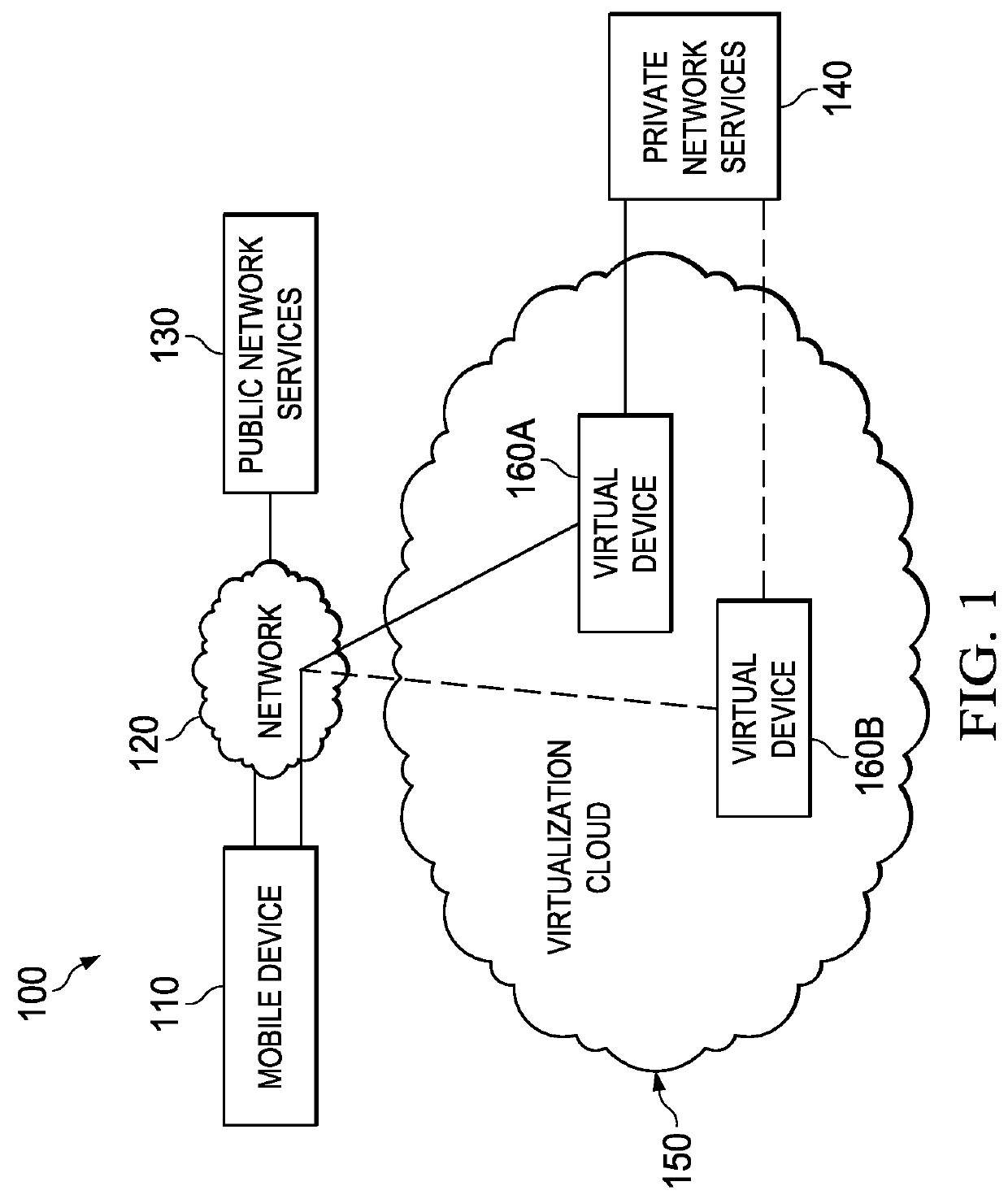

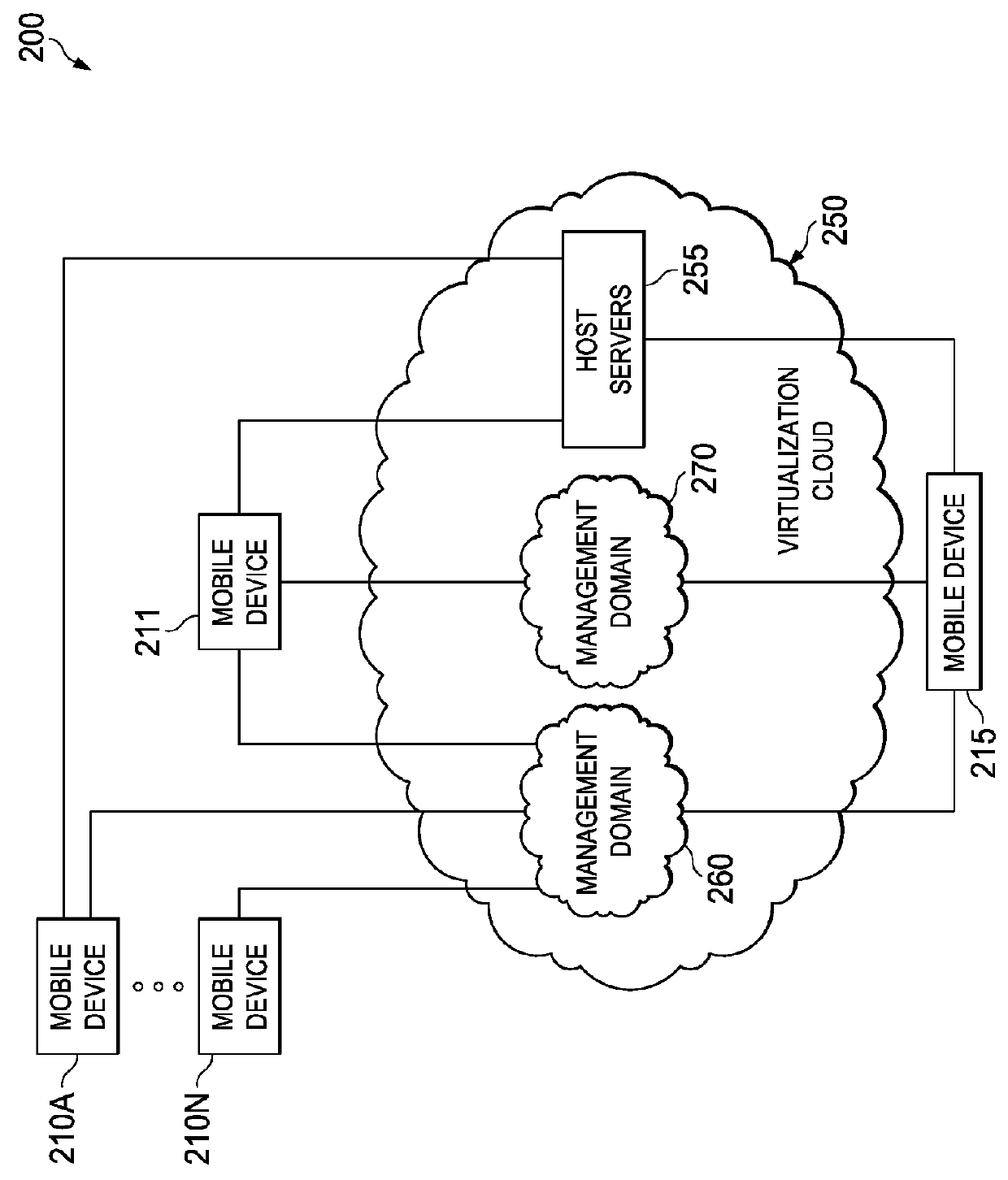

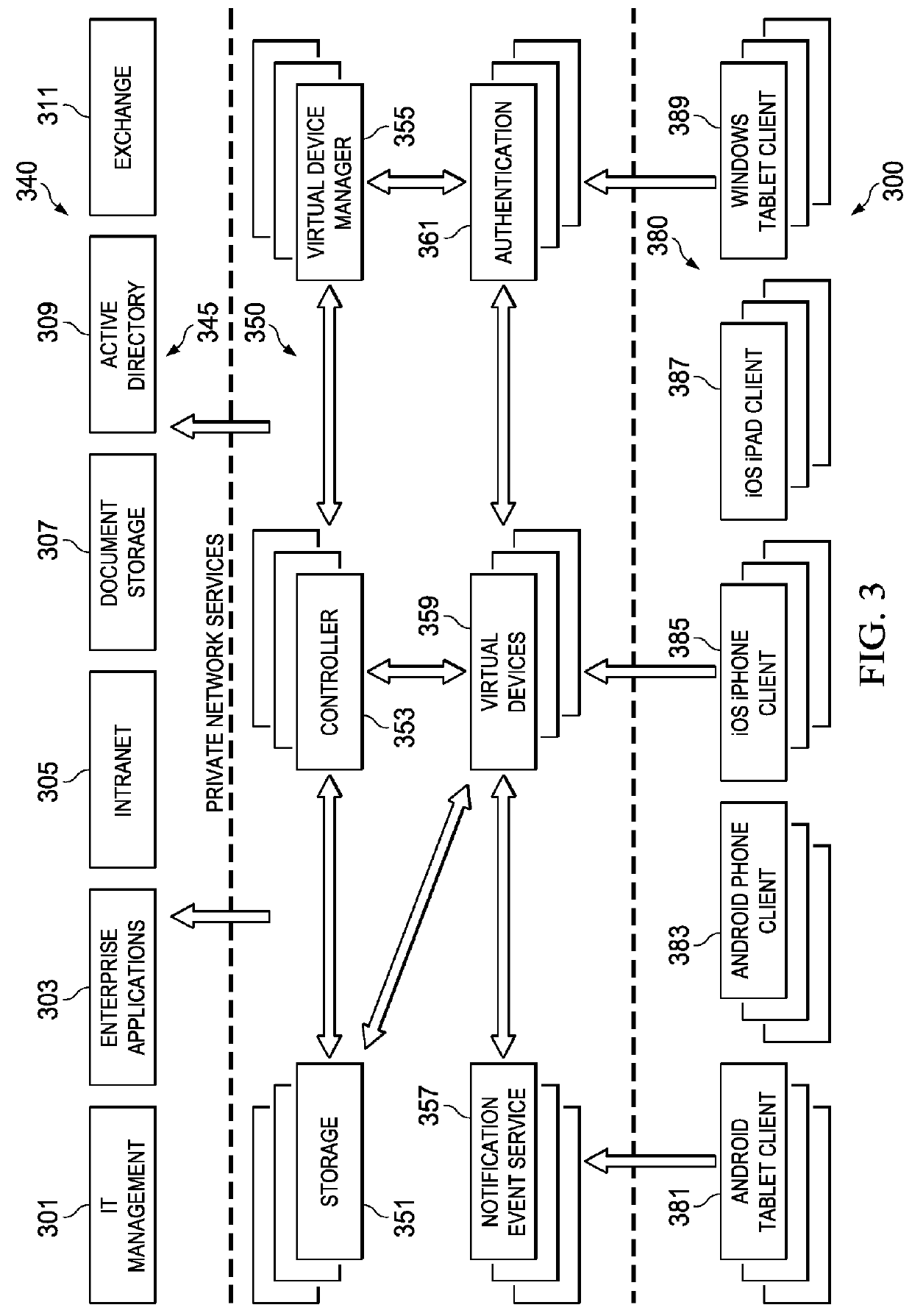

System, method and computer program product for connecting roaming mobile devices to a virtual device platform

ActiveUS9380523B1Reduce data latencyReduce the amount of resourcesAssess restrictionNetwork topologiesRoamingMobile device

Systems, methods and computer program products that enable efficient roaming of virtual mobile devices. In one embodiment, multiple PoP locations having a set of common master images are maintained. A communication from a mobile device received at a central facility identifies a user, a location and a type of the mobile device. The central facility determines performance measures for the PoP locations and identifies a preferred PoP location in response to the communication. If the preferred PoP location has available capacity, the central facility directs the preferred PoP location to provision resources and instantiate a virtual device from a selected master image corresponding to the mobile device. If the preferred PoP location persistently stores a user data volume for the user, the virtual device is attached to the stored user data volume. Otherwise, data is transferred from the user's data volume to a cache attached to the virtual device.

Owner:HYPORI INC

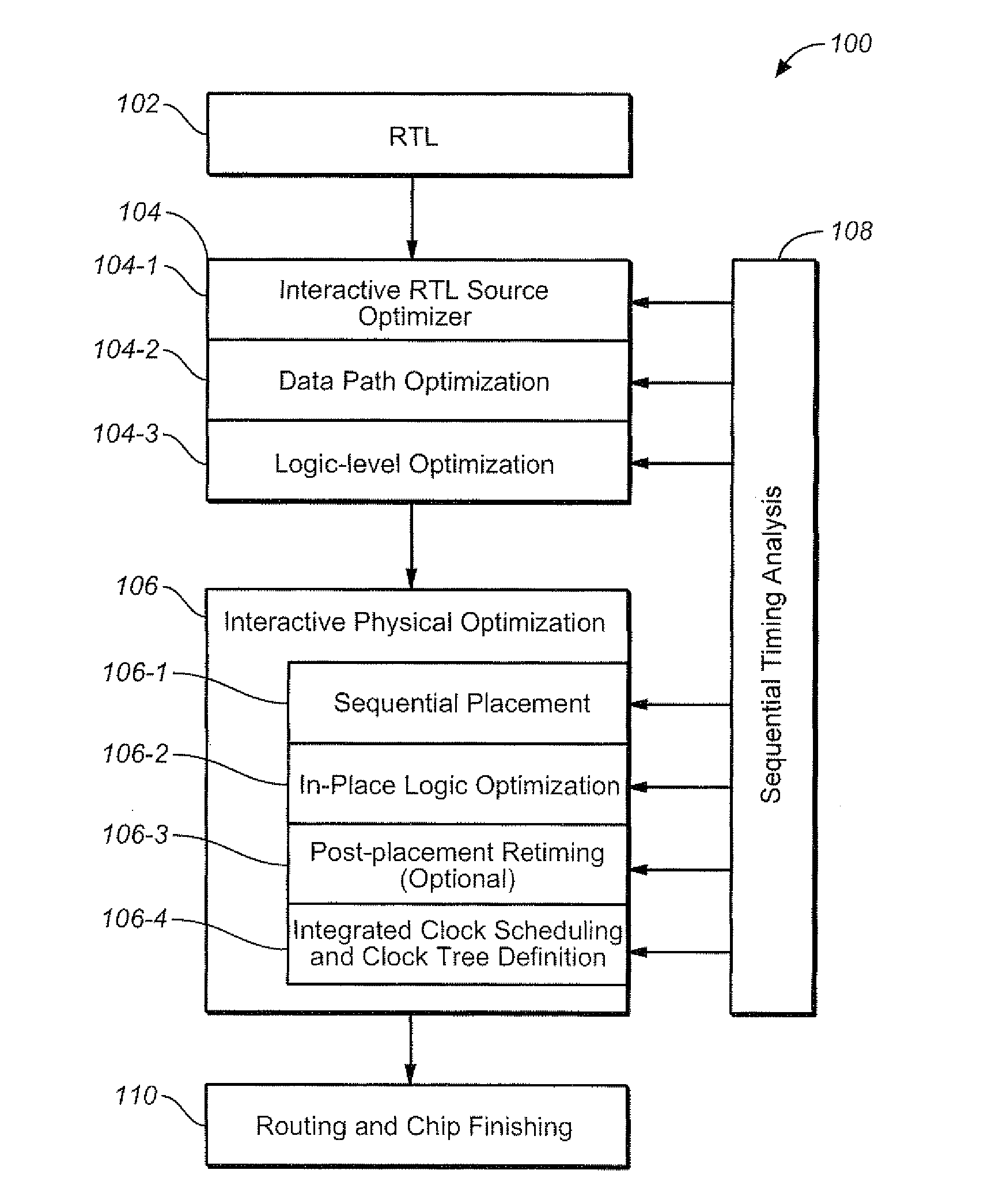

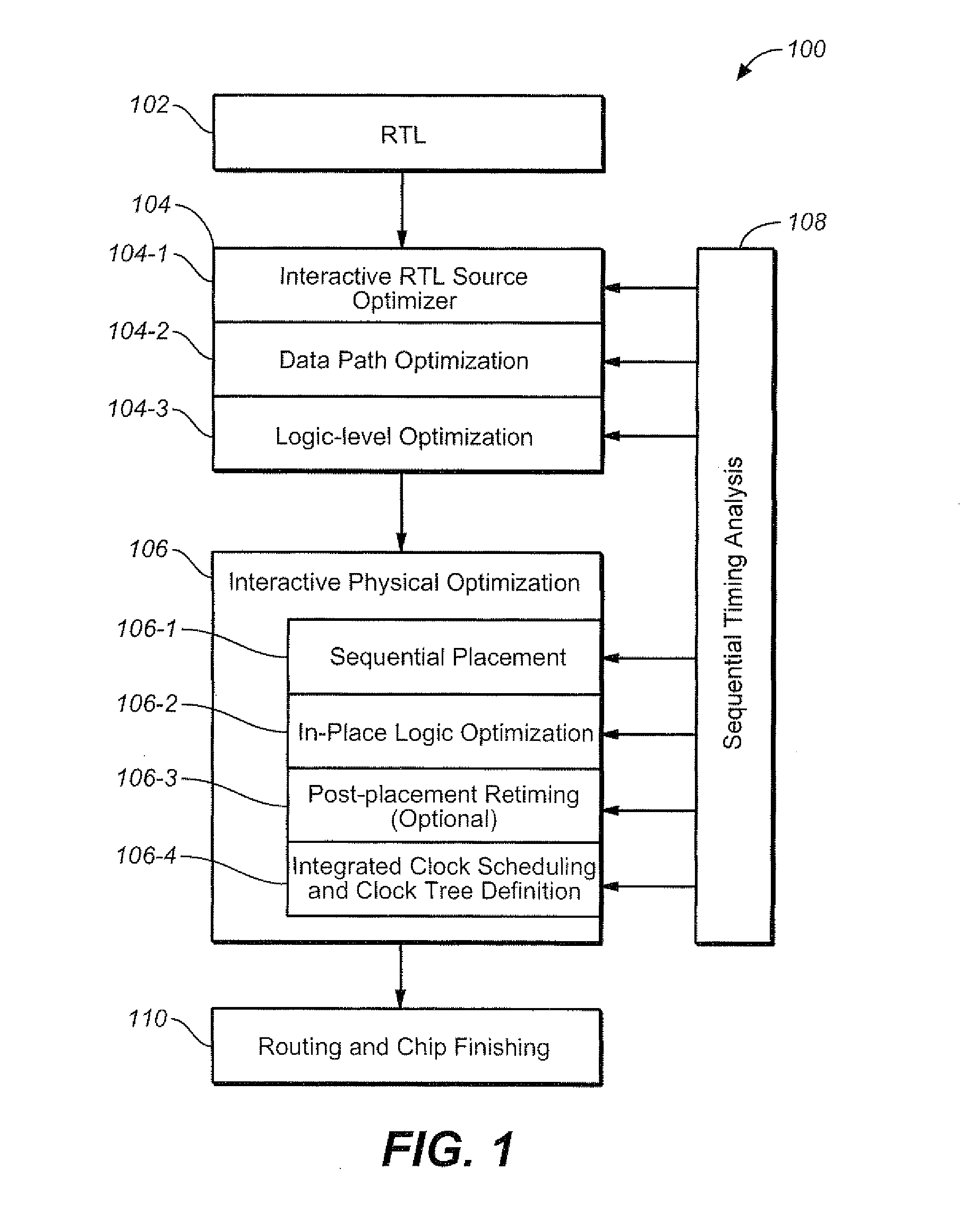

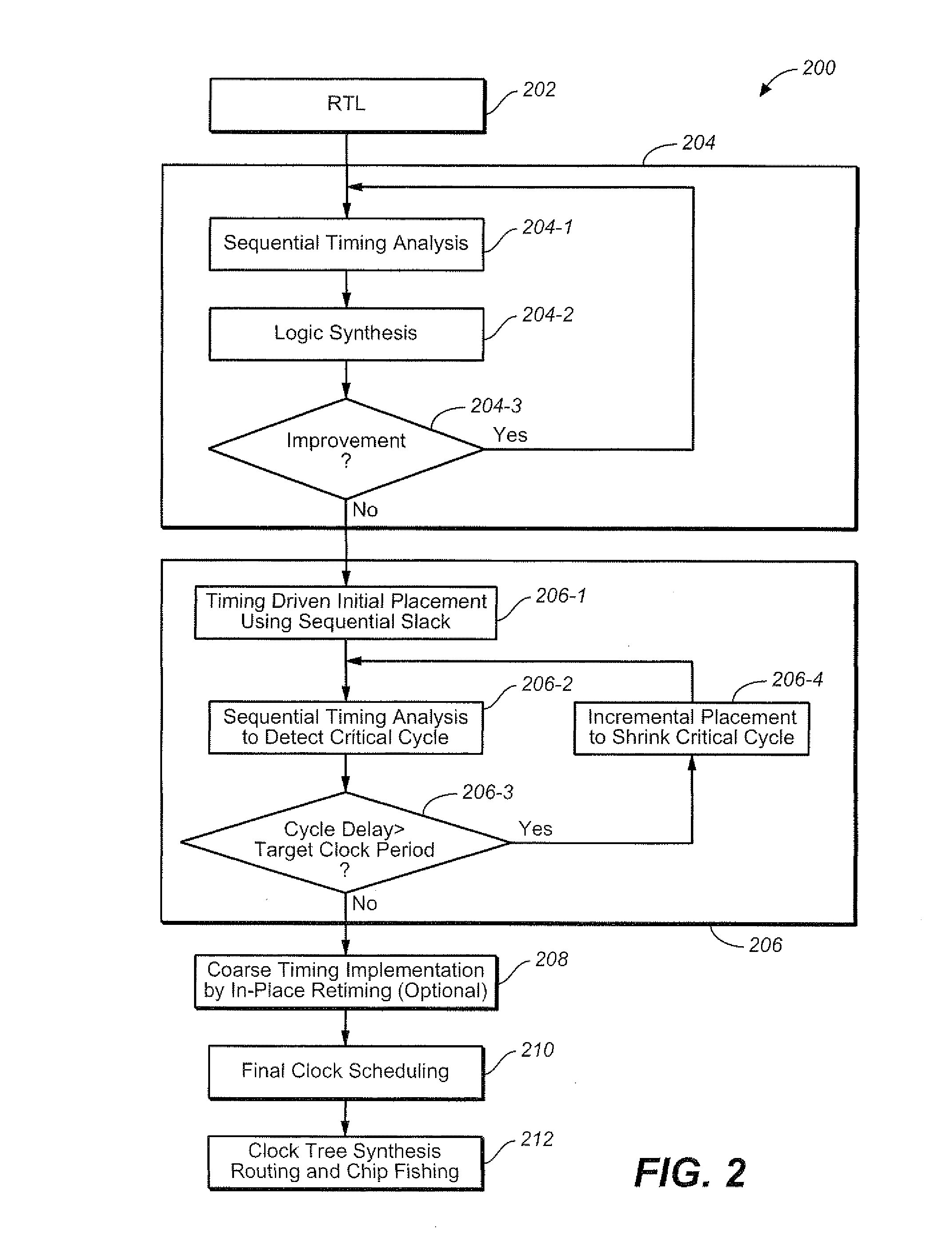

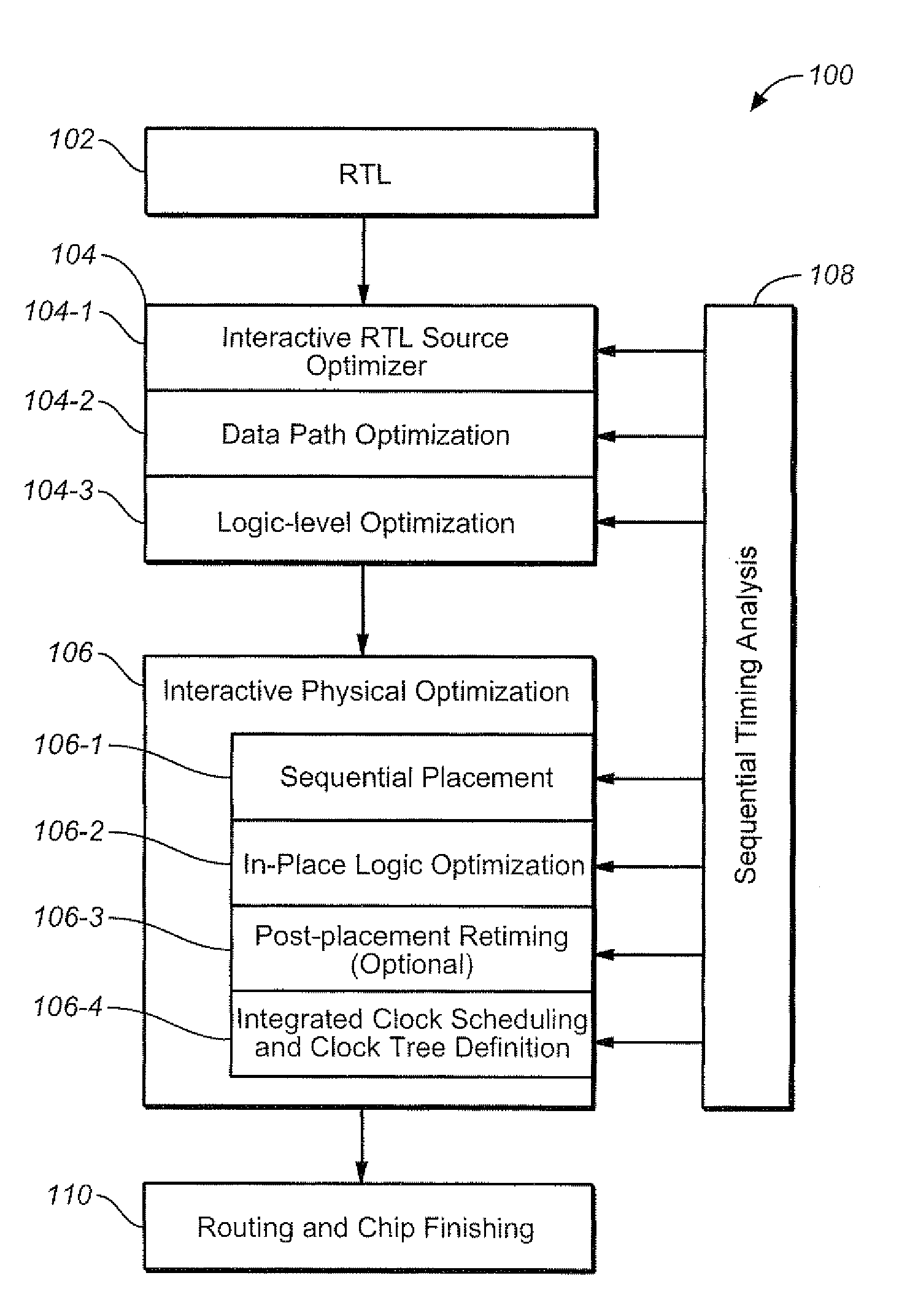

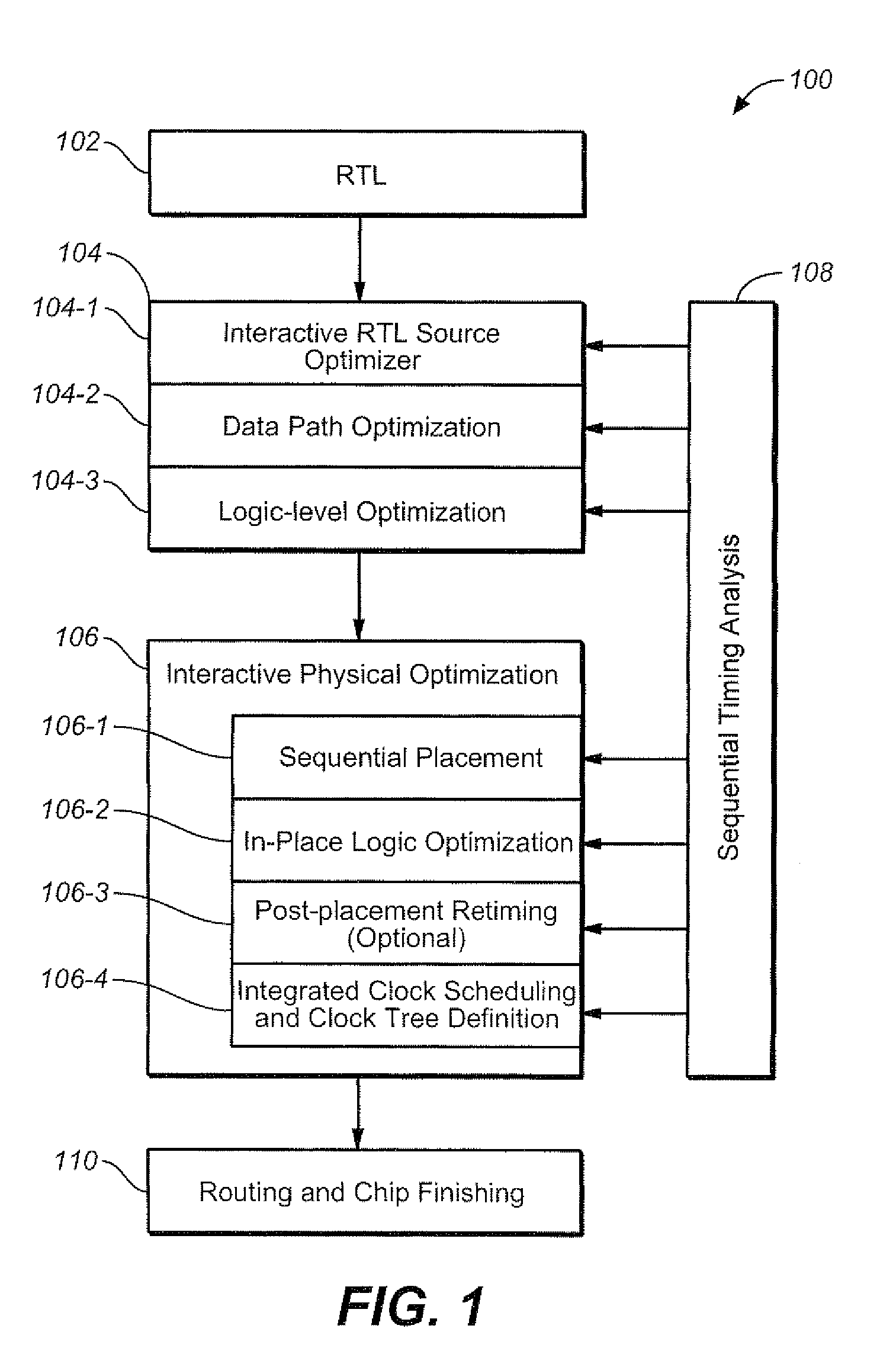

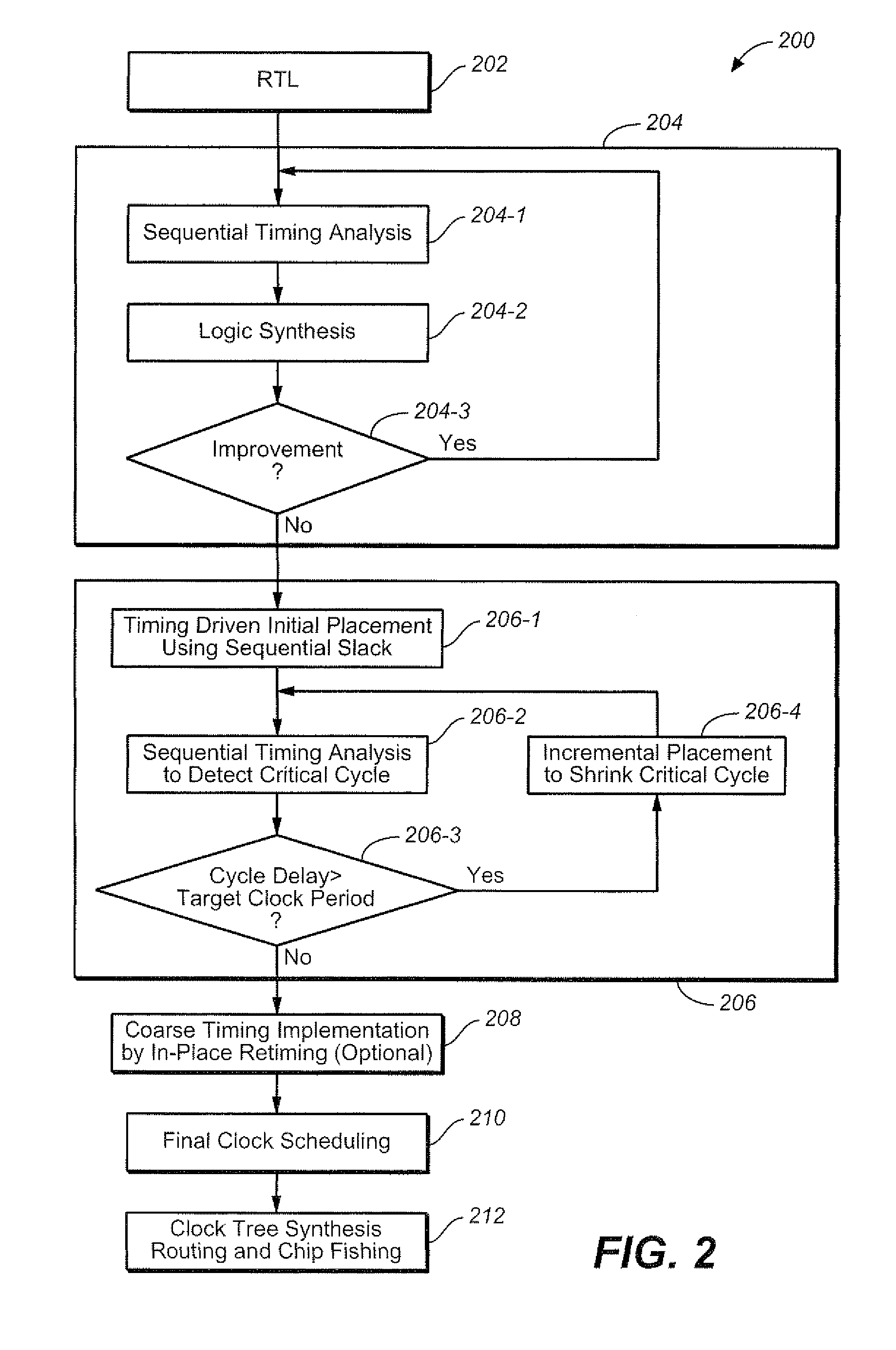

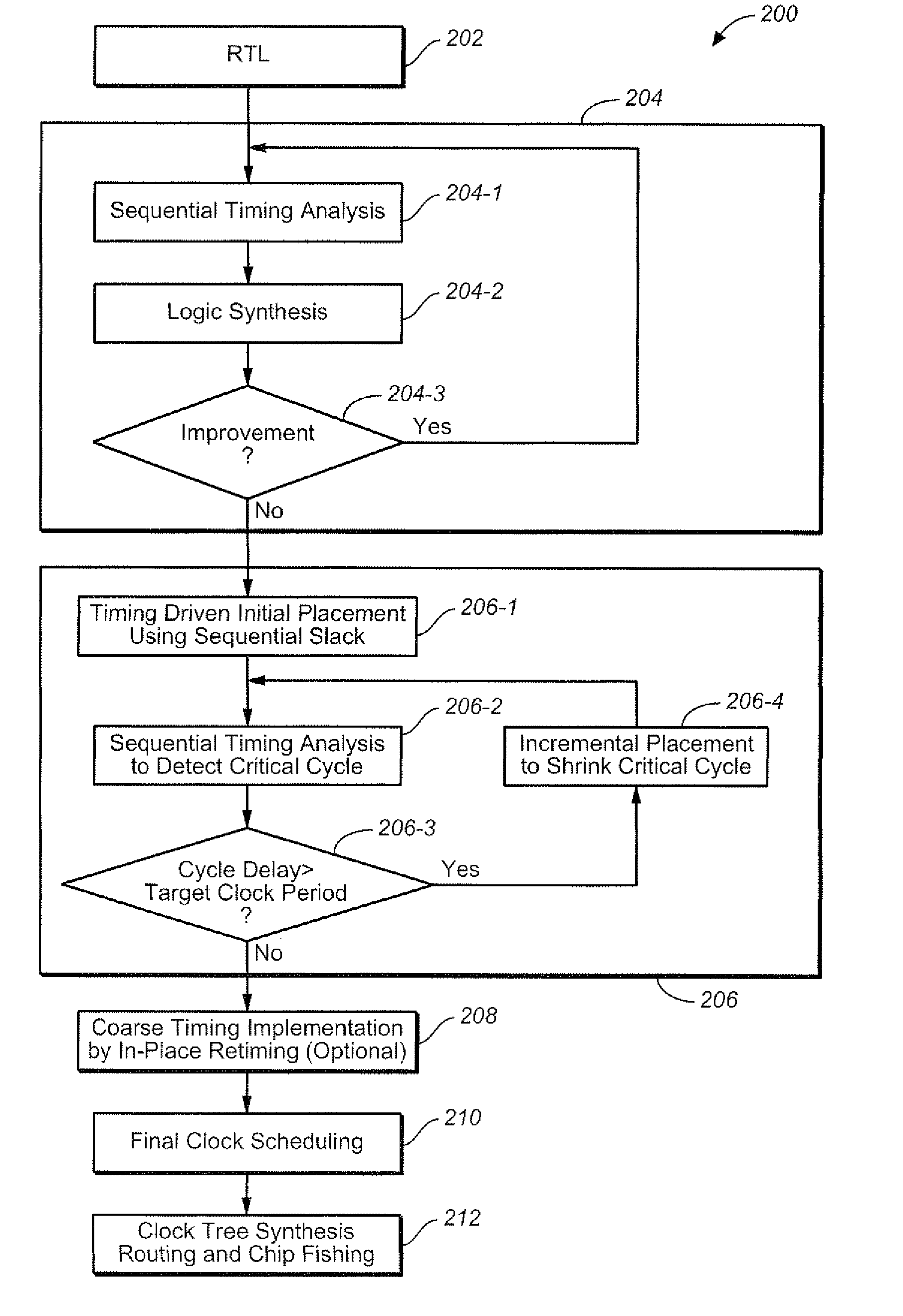

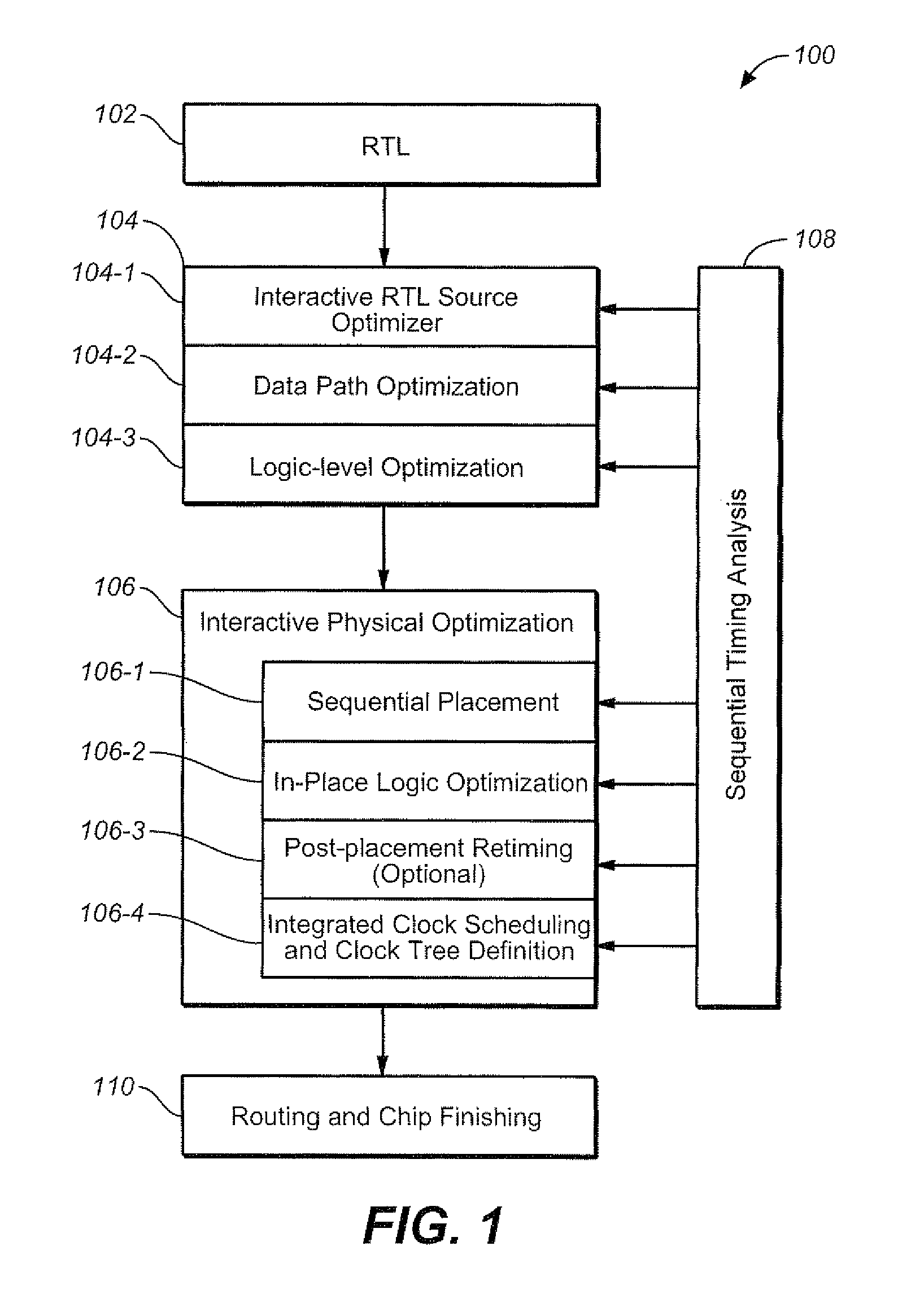

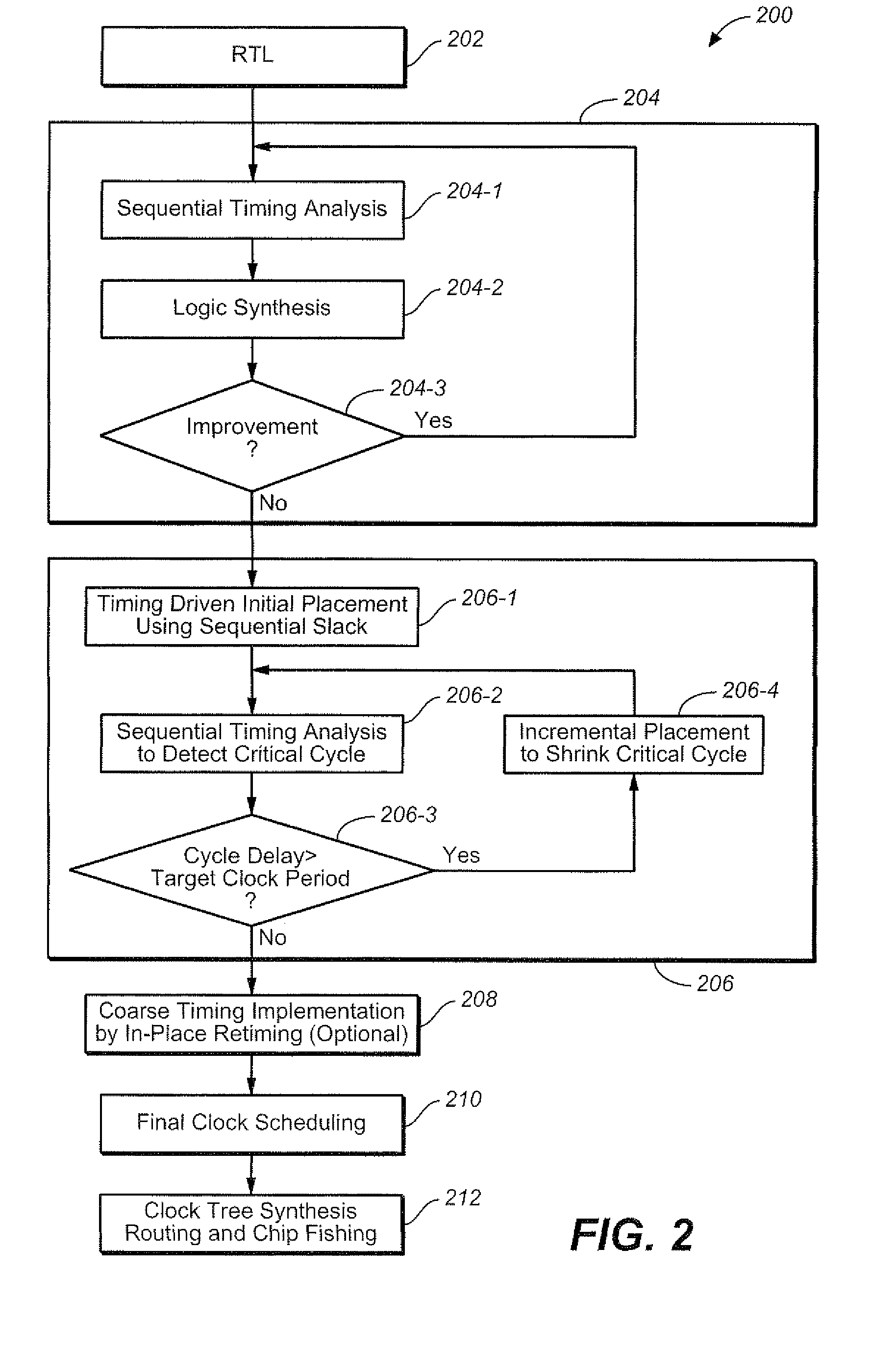

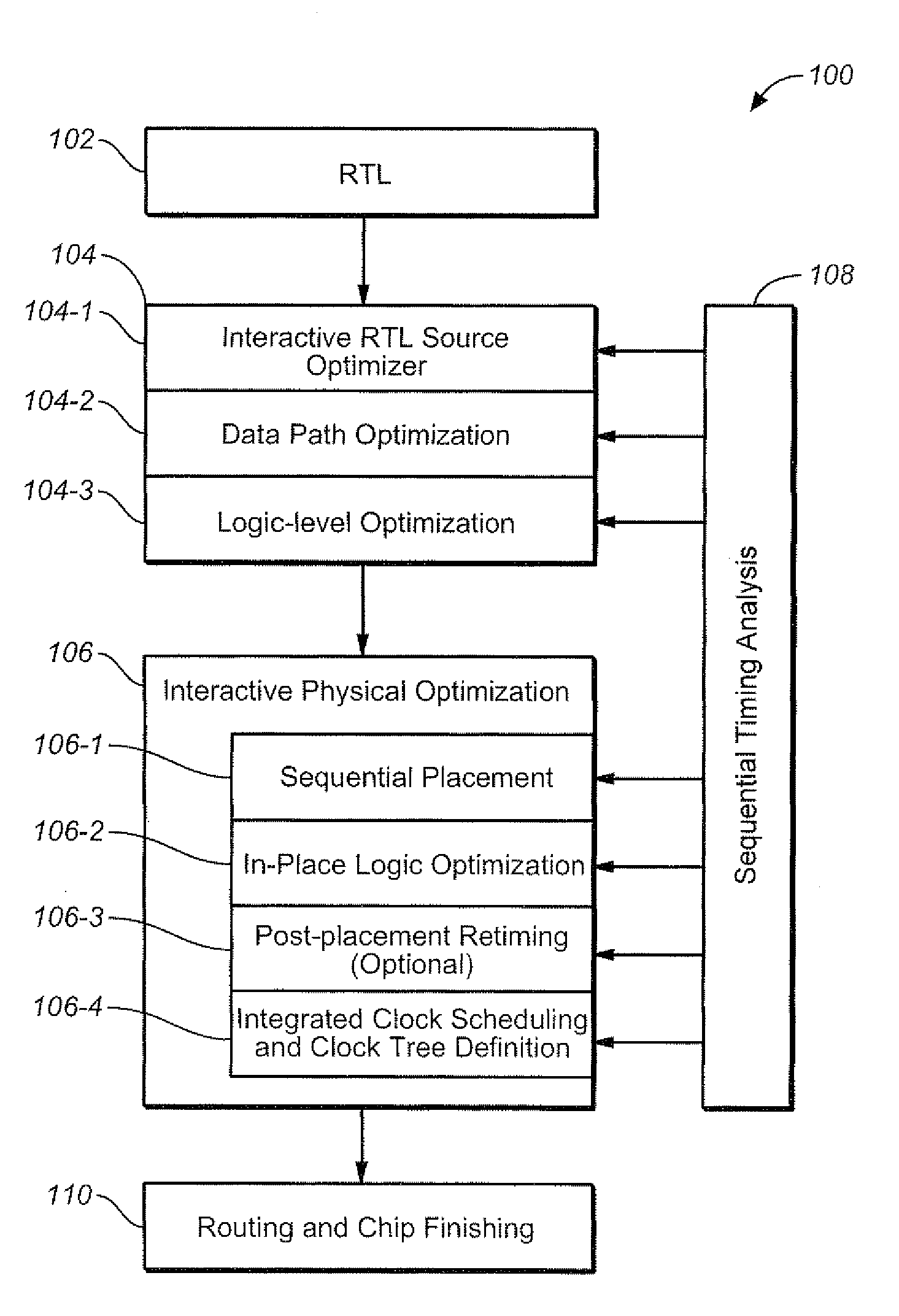

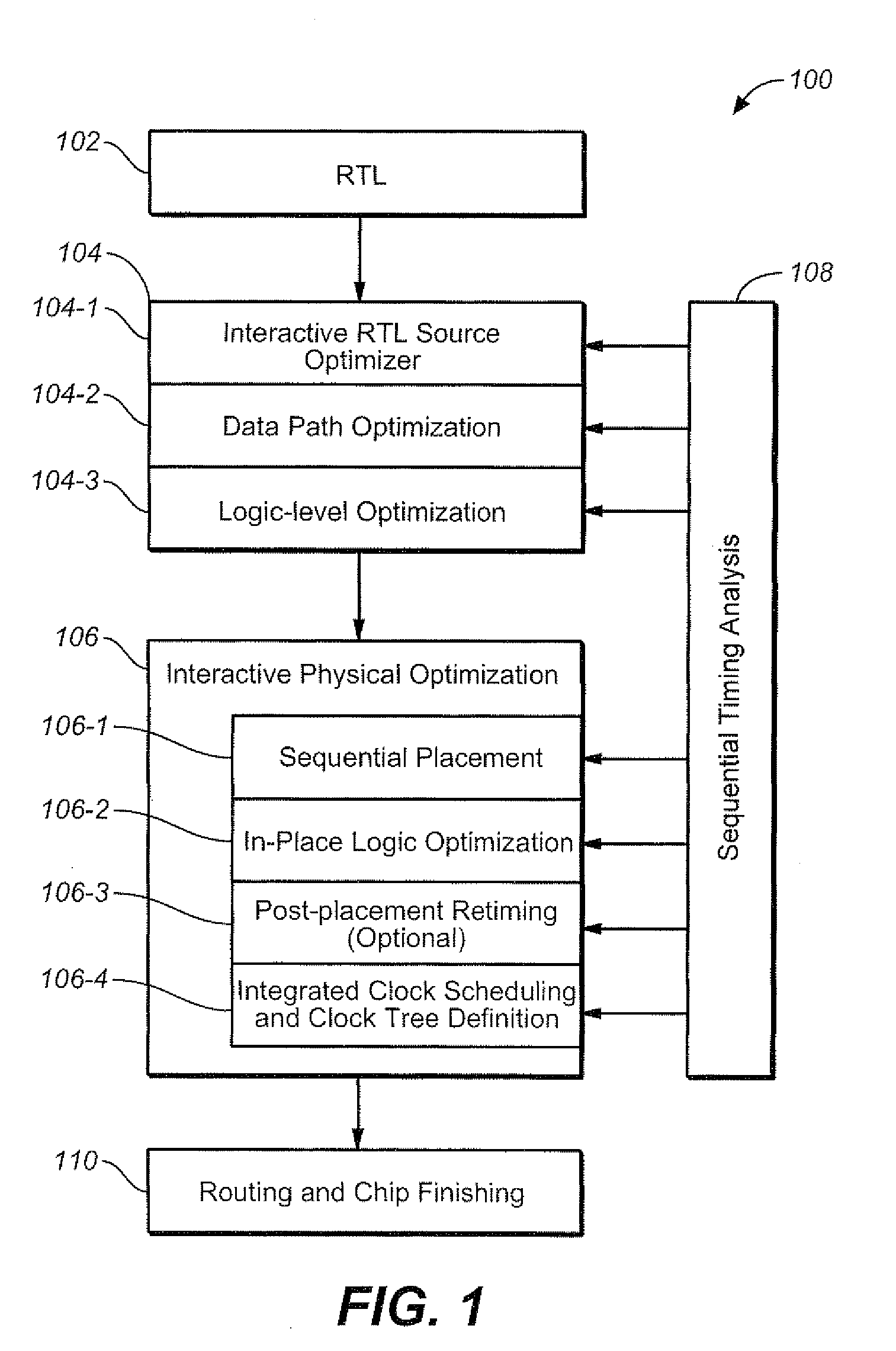

Optimizing integrated circuit design through use of sequential timing information

InactiveUS20080276209A1More optimizedLess minimum cycle timeCAD circuit designSoftware simulation/interpretation/emulationProcessor registerEngineering

A method is provided that includes: determining a minimum clock cycle that can be used to propagate a signal about the critical cycle in a circuit design; wherein the critical cycle is a cycle in the design that has a highest proportionality of delay to number of registers; determining for a circuit element in the circuit design, sequential slack associated with the circuit element; wherein the sequential slack represents a minimum delay from among respective maximum delays that can be added to respective structural cycles of which the circuit element is a constituent, based upon the determined limit upon clock cycle duration; using the sequential slack to ascertain sequential optimization based design flexibility throughout multiple stages of a design flow.

Owner:CADENCE DESIGN SYST INC

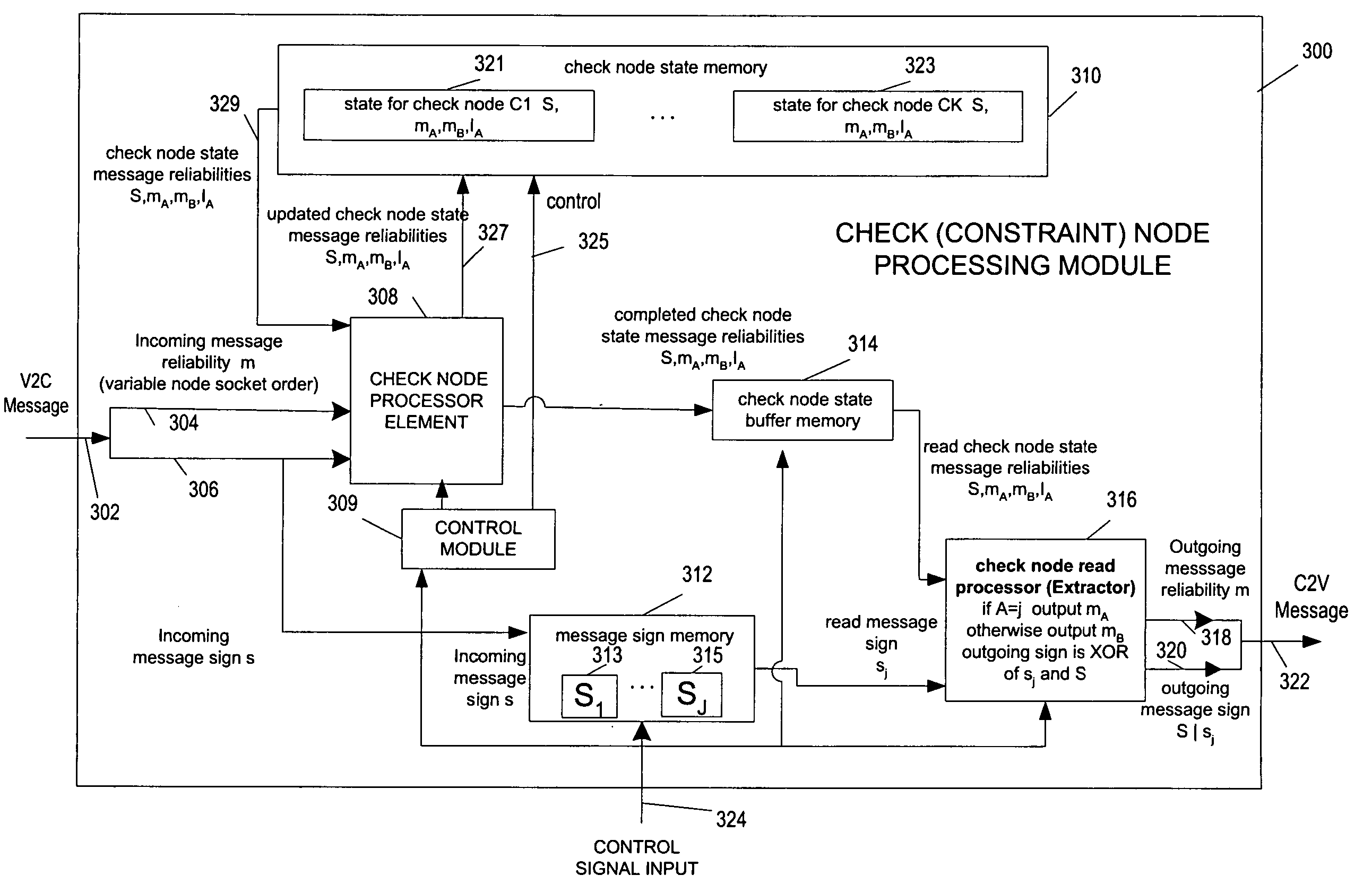

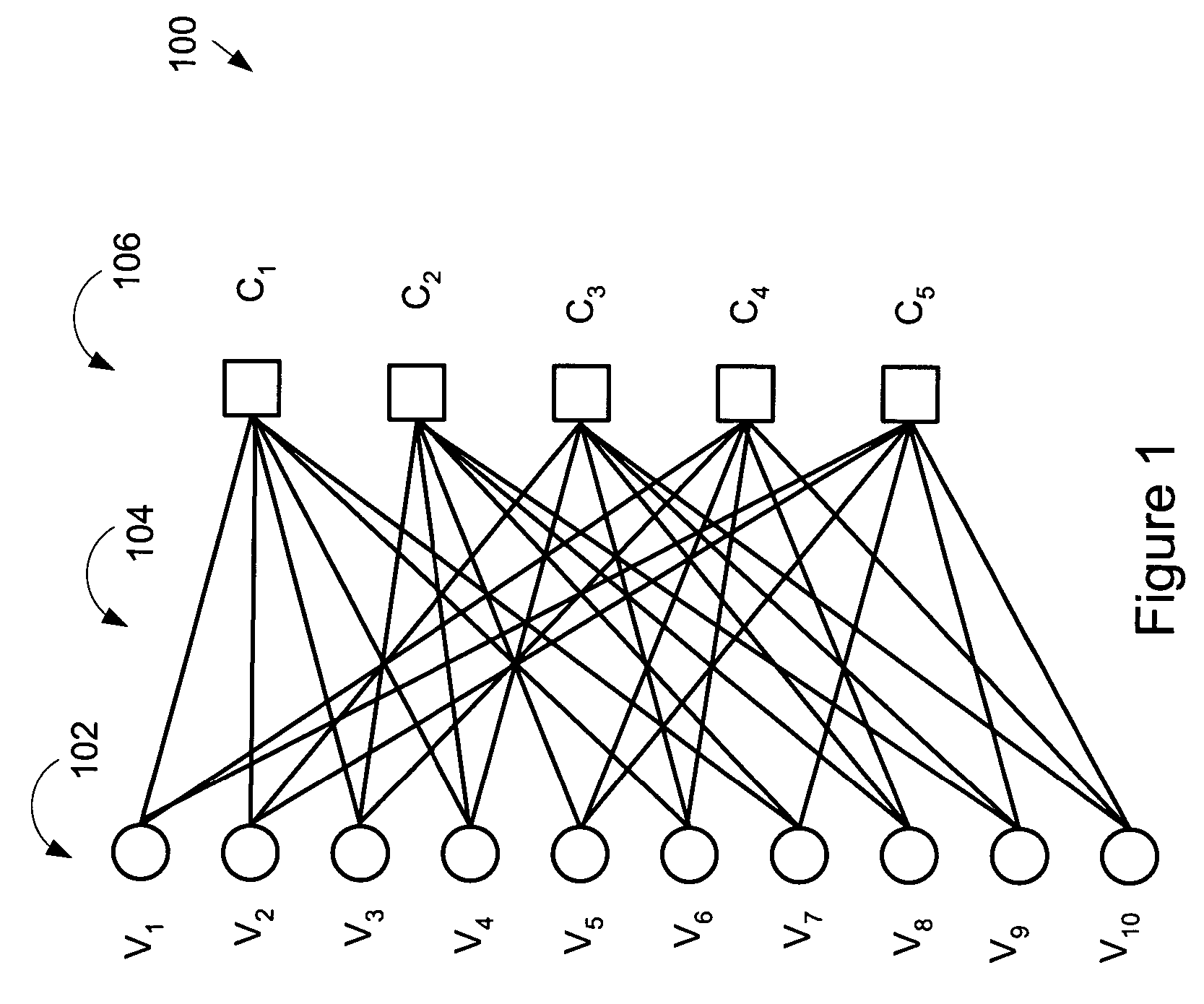

Memory efficient LDPC decoding methods and apparatus

ActiveUS20060026486A1Significant delayAvoiding and reducing delayError detection/correctionError correction/detection using multiple parity bitsLdpc decodingDecodes

Methods and apparatus for implementing memory efficient LDPC decodes are described. In accordance with the invention message information is stored in a compressed state for check node processing operations. The state for a check node is fully updated and then subject to an extraction process to generate check node to variable node messages. The signs of messages received from variable nodes may be stored by the check node processor module of the invention for use in message extraction. The check node processor can process messages in variable node order thereby allowing the variable node processor and check node processor to operate on messages in the same order reducing or eliminating the need to buffer and / or reorder messages passed between check nodes and variable nodes. Graph structures which allow check node processing on one graph iteration to proceed before the previous graph iteration has been completed are also described.

Owner:QUALCOMM INC

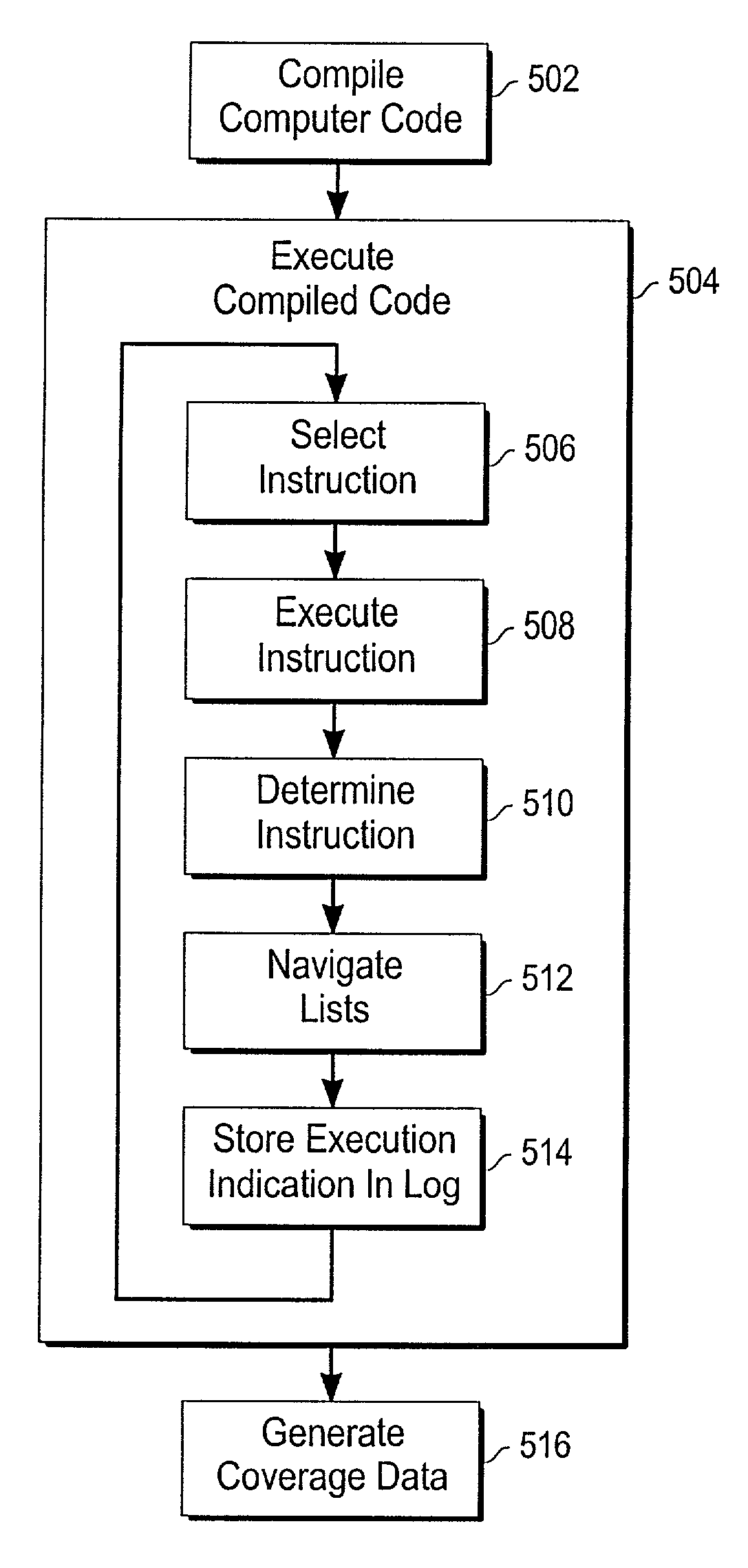

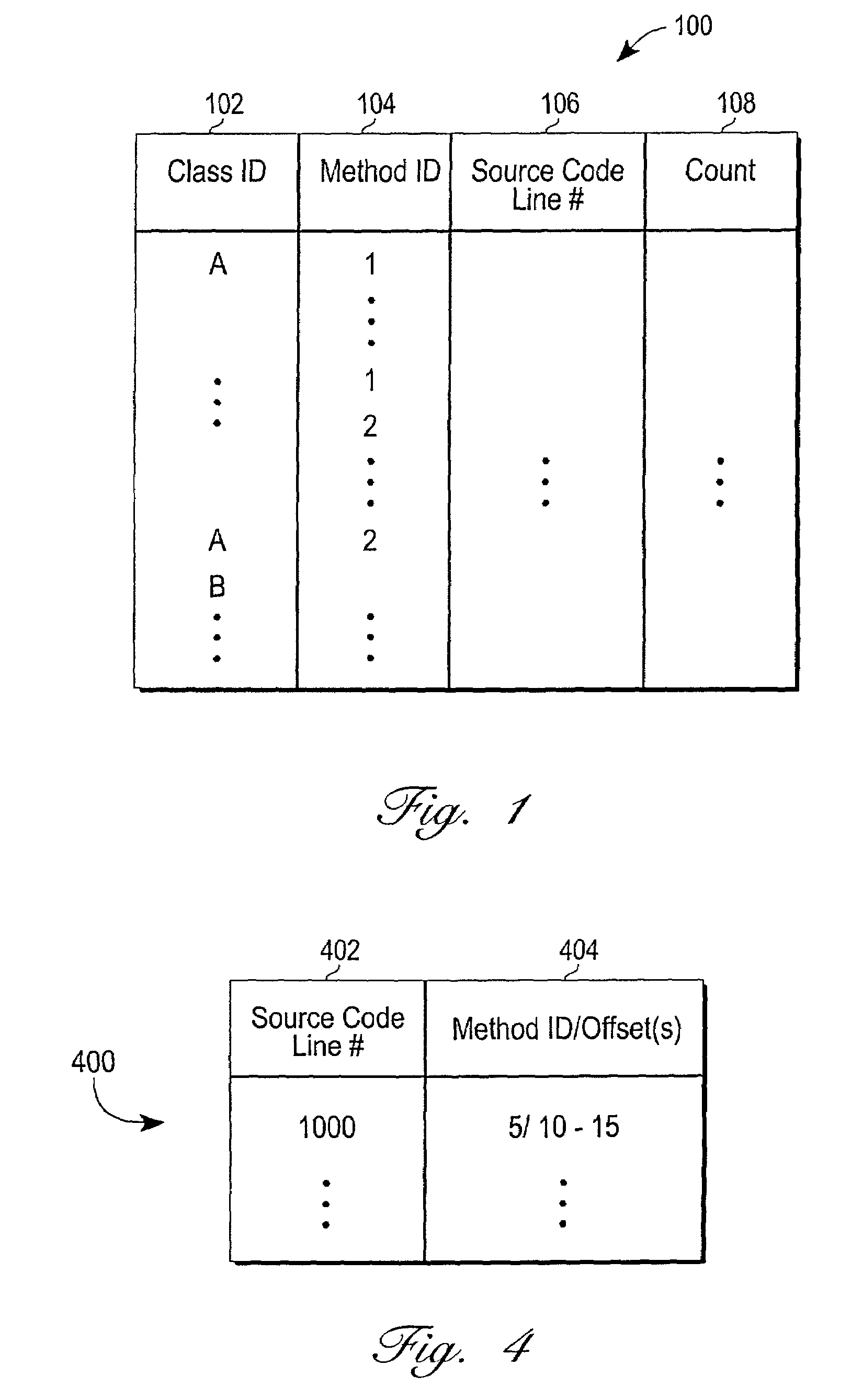

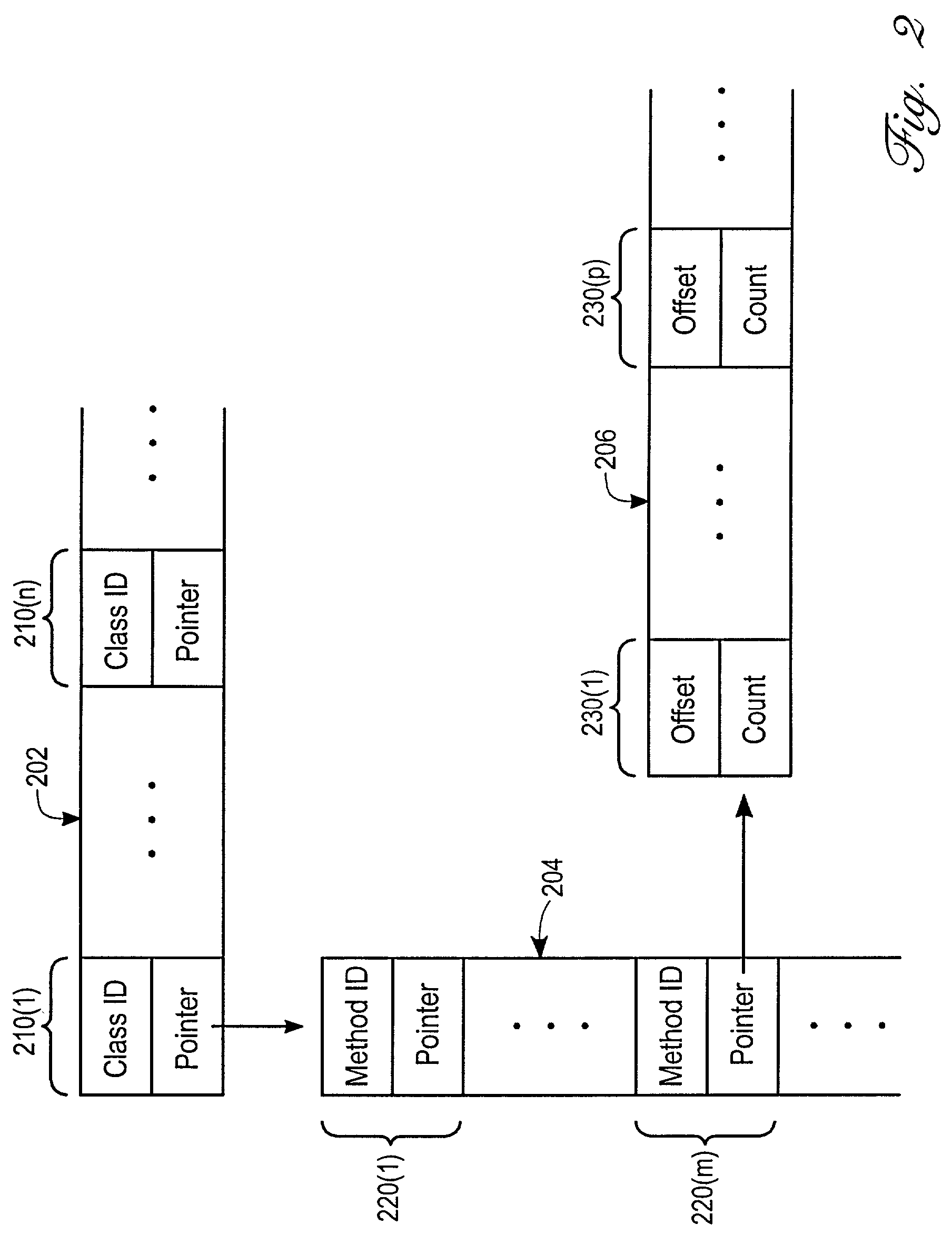

Mechanism for generating an execution log and coverage data for a set of computer code

ActiveUS7080358B2Minimal amount of storageTo overcome the large delaySoftware testing/debuggingSpecific program execution arrangementsParallel computingCoverage data

An improved mechanism is provided for generating an execution log and coverage data for a set of computer code. To minimize the amount of storage required for storing execution log information, the mechanism: (1) stores only information pertaining to instructions that are actually executed during execution; and (2) stores the information in a hierarchically organized set of lists. In addition, to minimize the impact of execution log and coverage data generation on the execution of the computer code, coverage data is generated after execution has completed. By generating the execution log and coverage data in this manner, storage requirements are reduced, and execution performance is improved.

Owner:ORACLE INT CORP

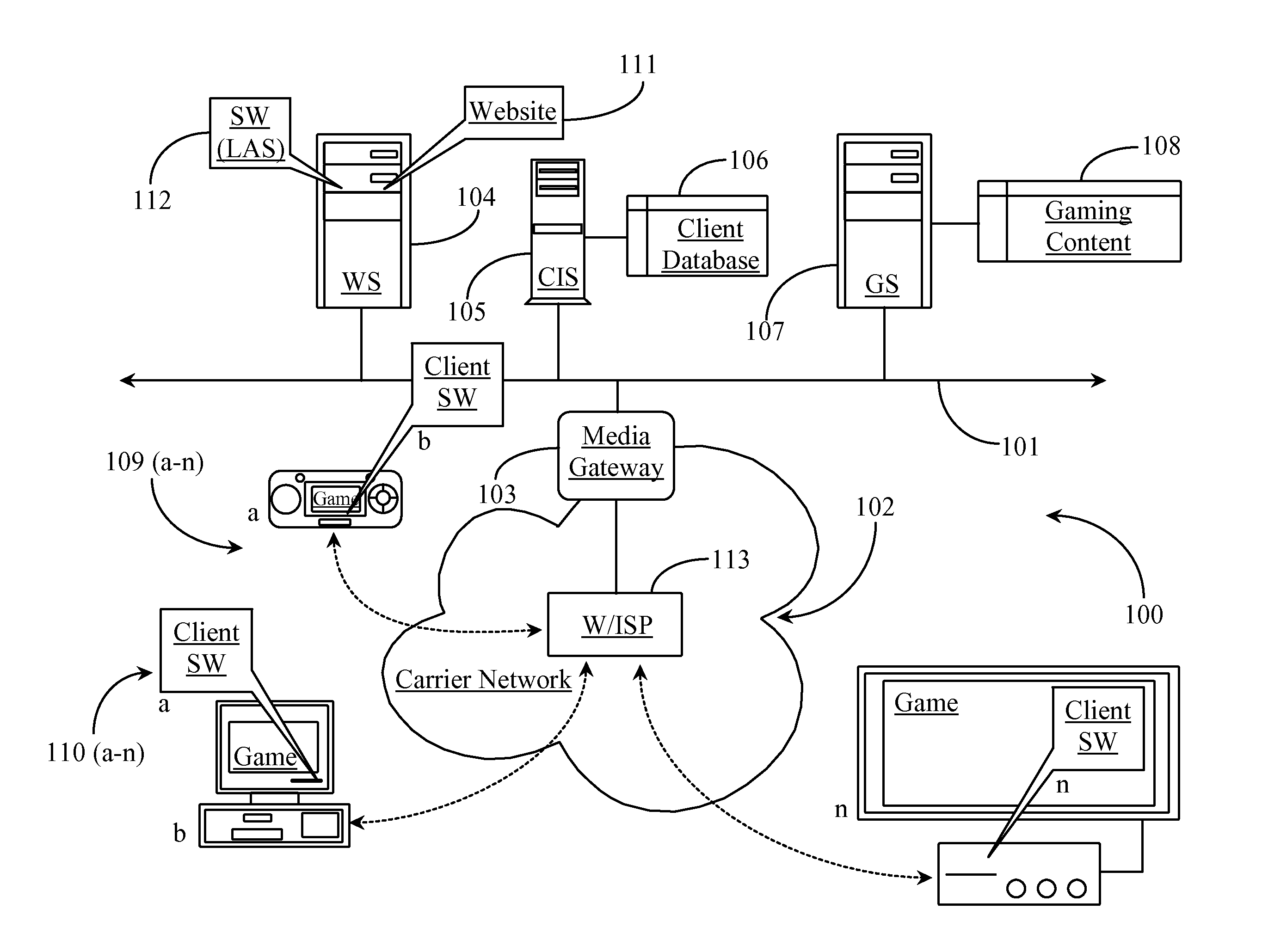

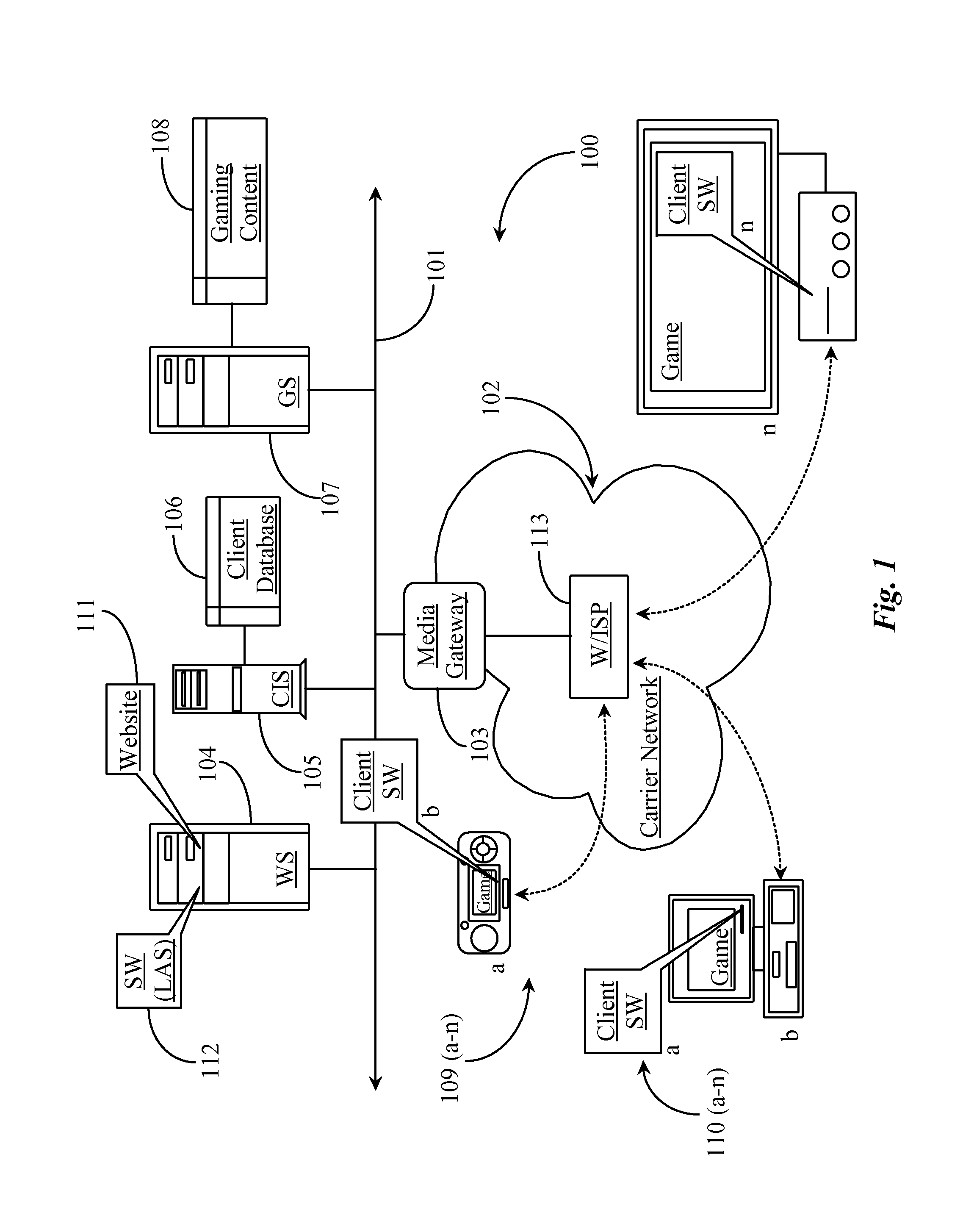

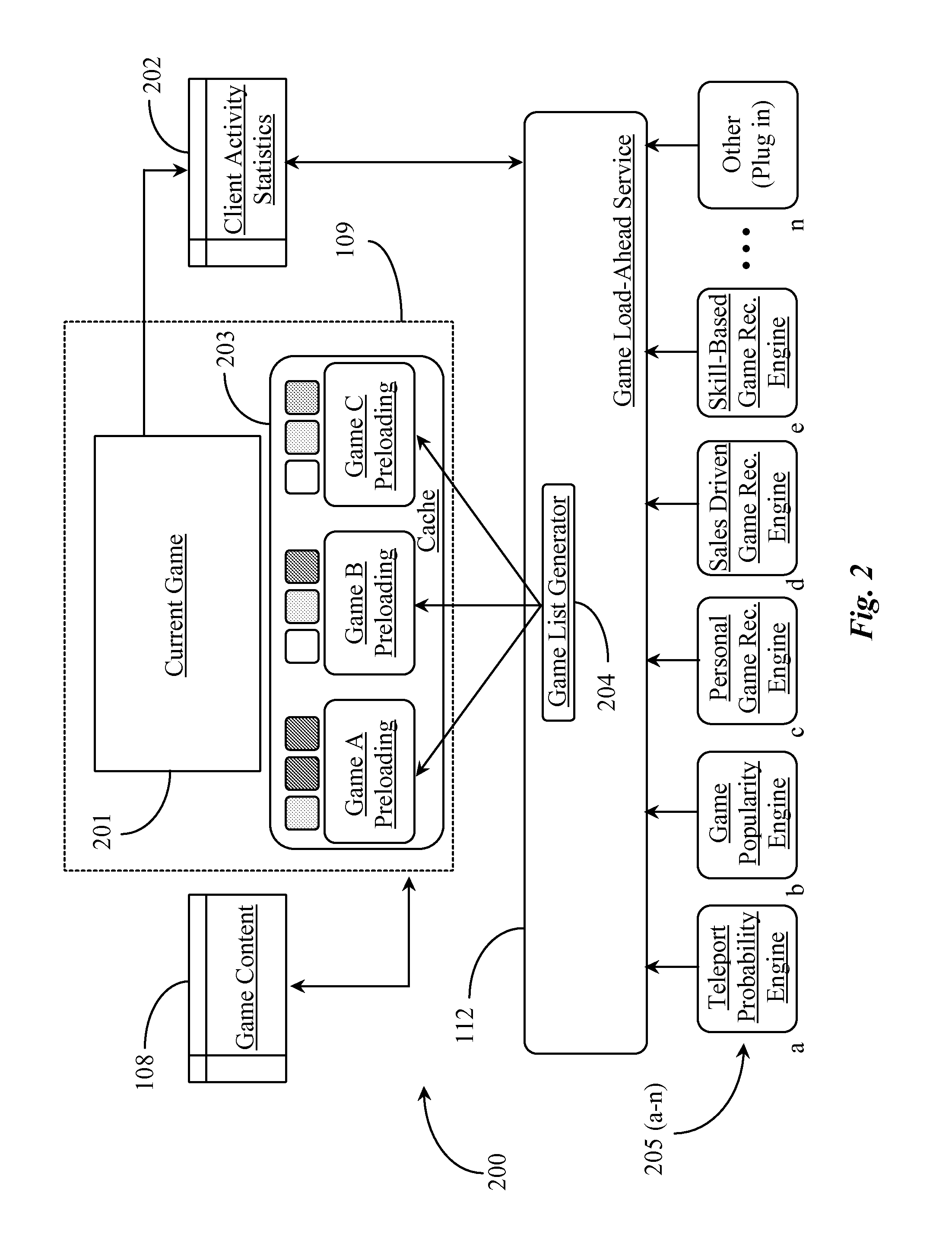

System for Pre-Caching Game Content Based on Game Selection Probability

InactiveUS20130137518A1Faster game loadingImprove loading timeVideo gamesTransmissionThe InternetDigital resources

A system for serving digital games to clients has an Internet-connected server, a digital data repository coupled to the Internet-connected server, the data repository storing digital resources for playing a plurality of games on a computerized appliance; and software executing on the Internet-connected server from a non-transitory physical medium, the software providing a first function determining for a specific client a list of games by probability of subsequent client selection, a second function causing transmission of resources for the list of games determined by the first function, directed to a computerized appliance associated with client, beginning with the most probable game in the list.

Owner:ROBLOX CORP

Data path and placement optimization in an integrated circuit through use of sequential timing information

InactiveUS7624364B2Increase flexibilityEasy to implementCAD circuit designSoftware simulation/interpretation/emulationProcessor registerDatapath

A method is provided that includes: determining a minimum clock cycle that can be used to propagate a signal about the critical cycle in a circuit design; wherein the critical cycle is a cycle in the design that has a highest proportionality of delay to number of registers; determining for a circuit element in the circuit design, sequential slack associated with the circuit element; wherein the sequential slack represents a minimum delay from among respective maximum delays that can be added to respective structural cycles of which the circuit element is a constituent, based upon the determined limit upon clock cycle duration; using the sequential slack to ascertain sequential optimization based design flexibility throughout multiple stages of a design flow.

Owner:CADENCE DESIGN SYST INC

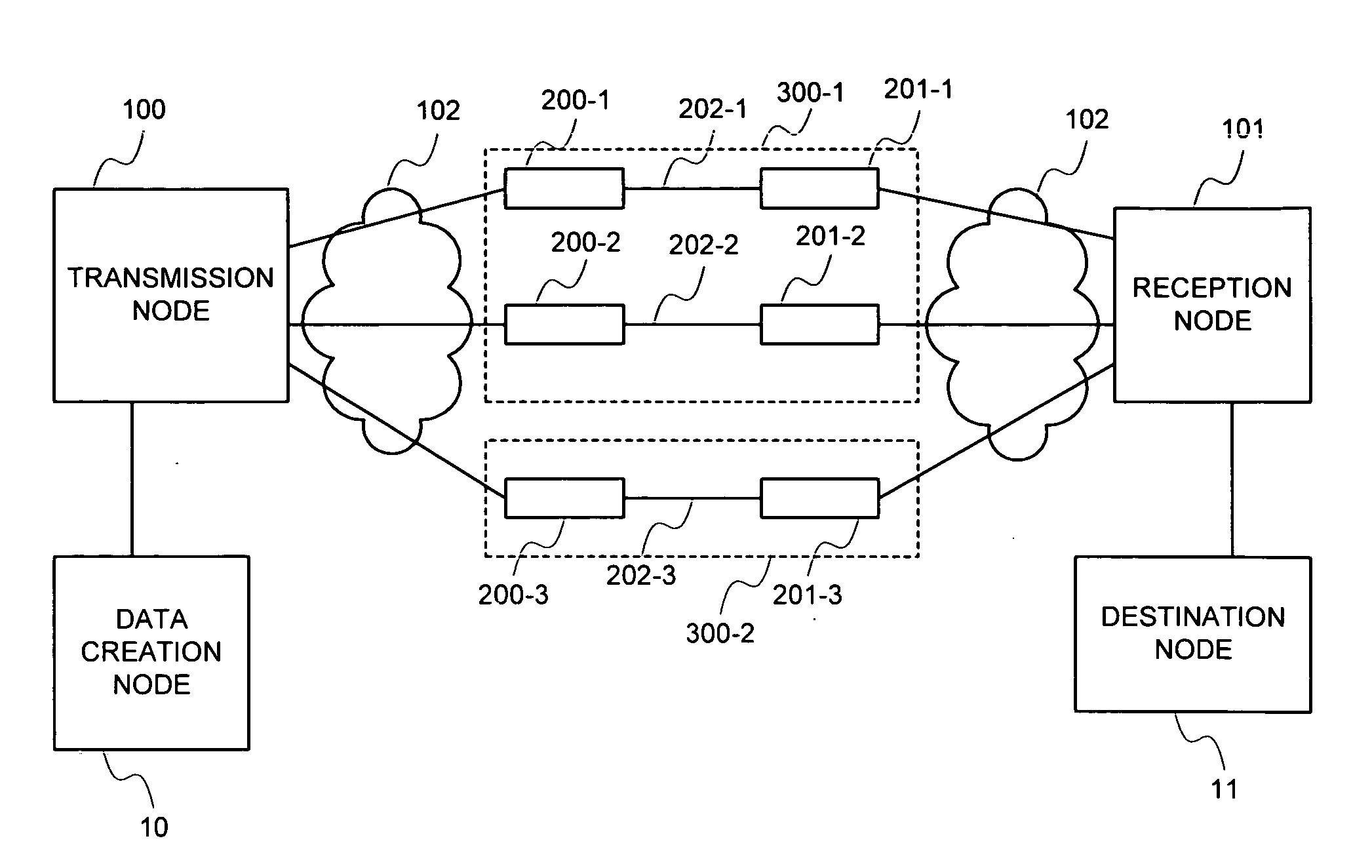

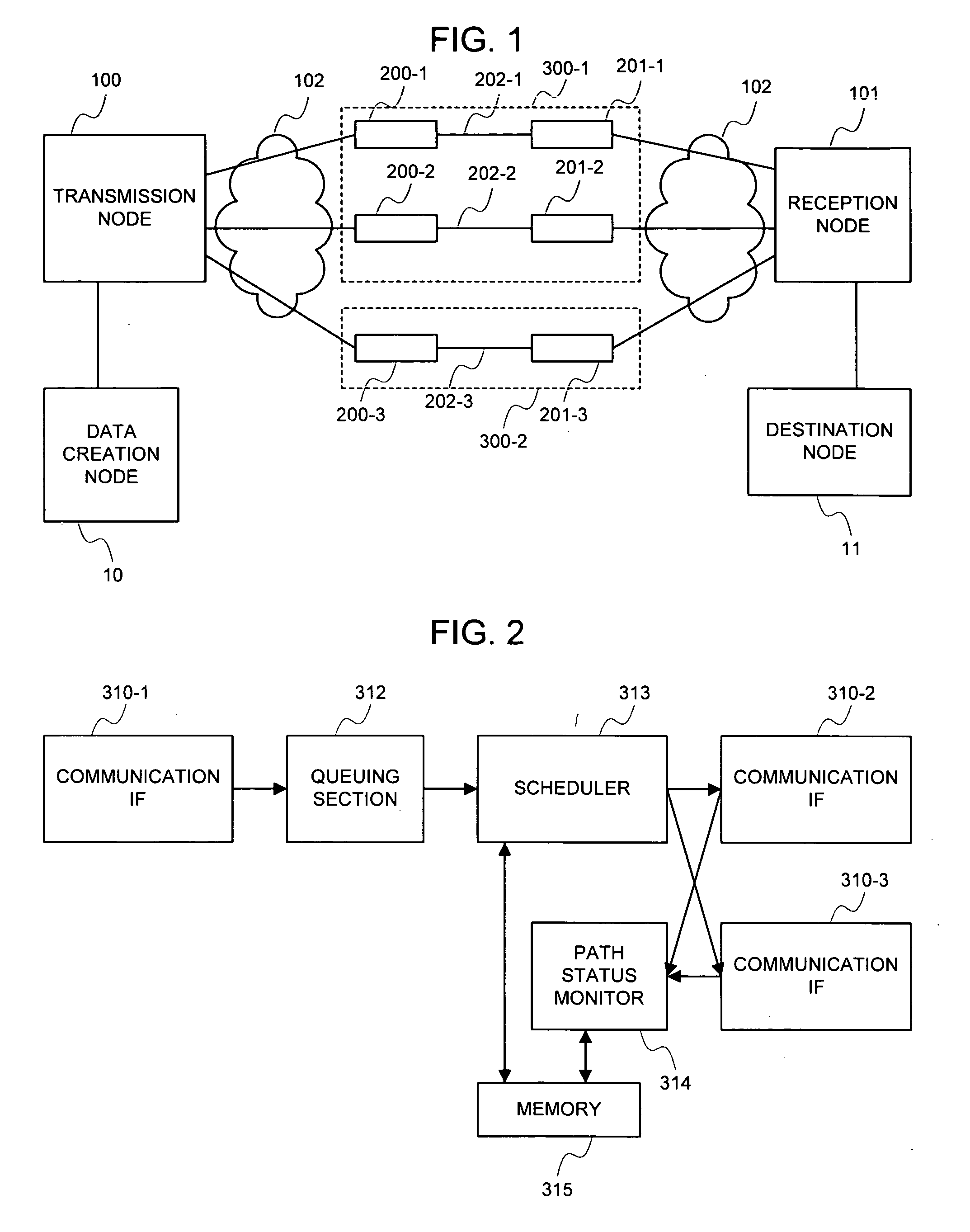

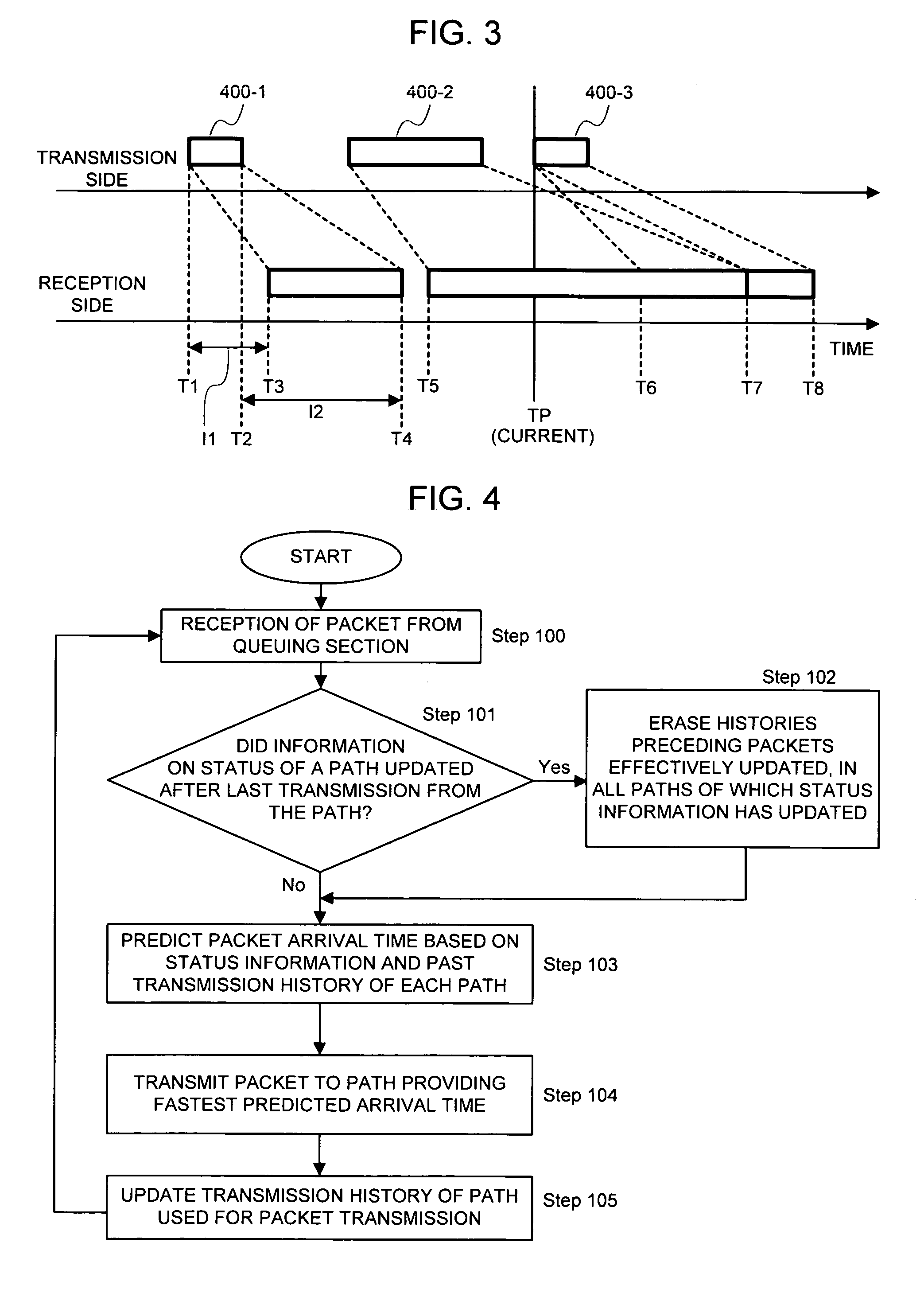

Load distributing method

ActiveUS20070002748A1Improve accuracyMultiplexing efficiency decrease can be avoidedError preventionFrequency-division multiplex detailsCompletion timePacket arrival

When path status information is updated, the time at which the update is effective is recorded. A packet arrival time in each path is predicted based on new status information and data transmission history after the effective time. The packet is transmitted to the path that provides a fastest packet arrival time. This reflects the path status available from the reception side on the data transmitted in past, so that an actual data arrival time, an arrival time close to a reception completion time, or a reception completion time can be predicted.

Owner:NEC CORP

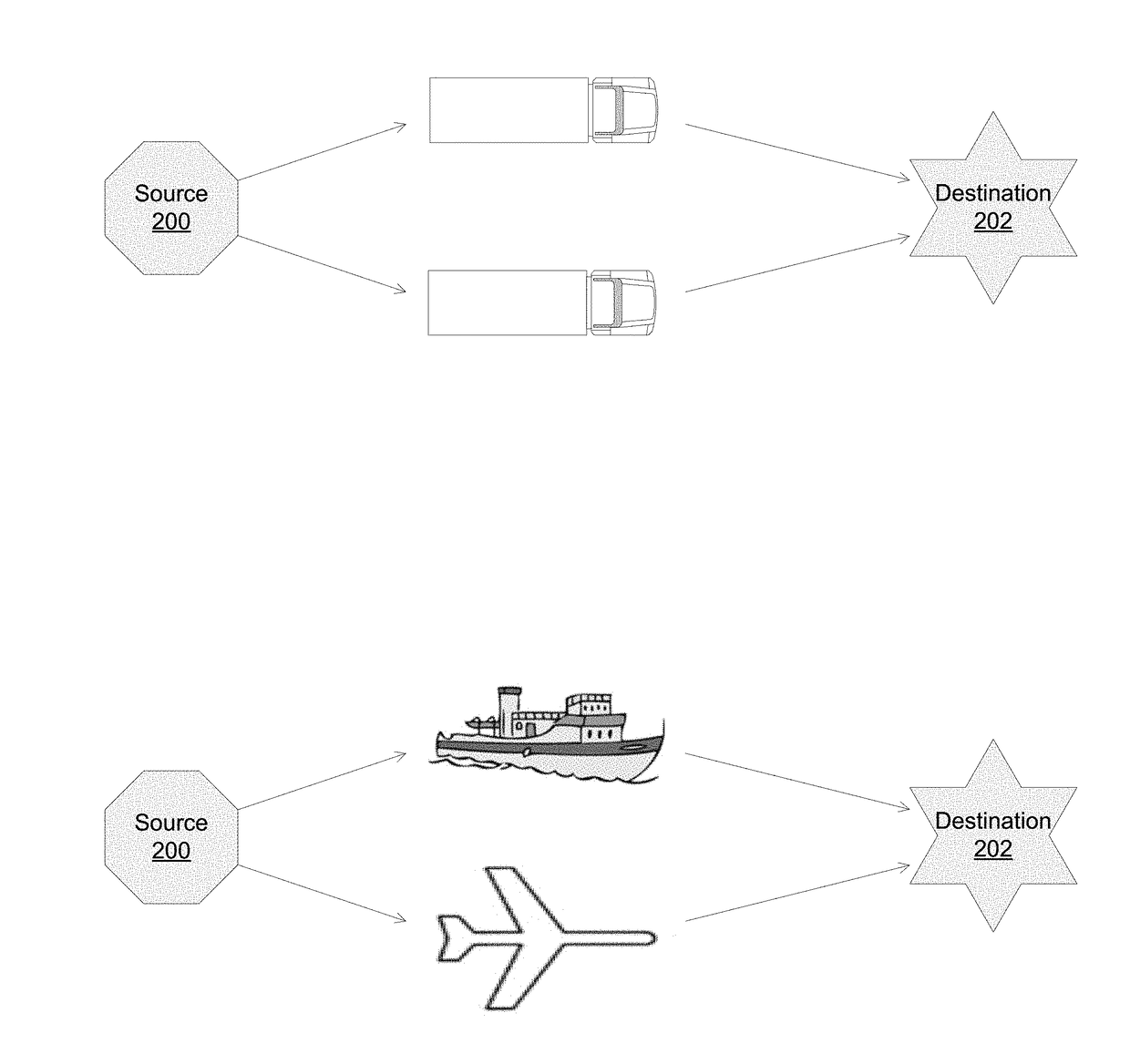

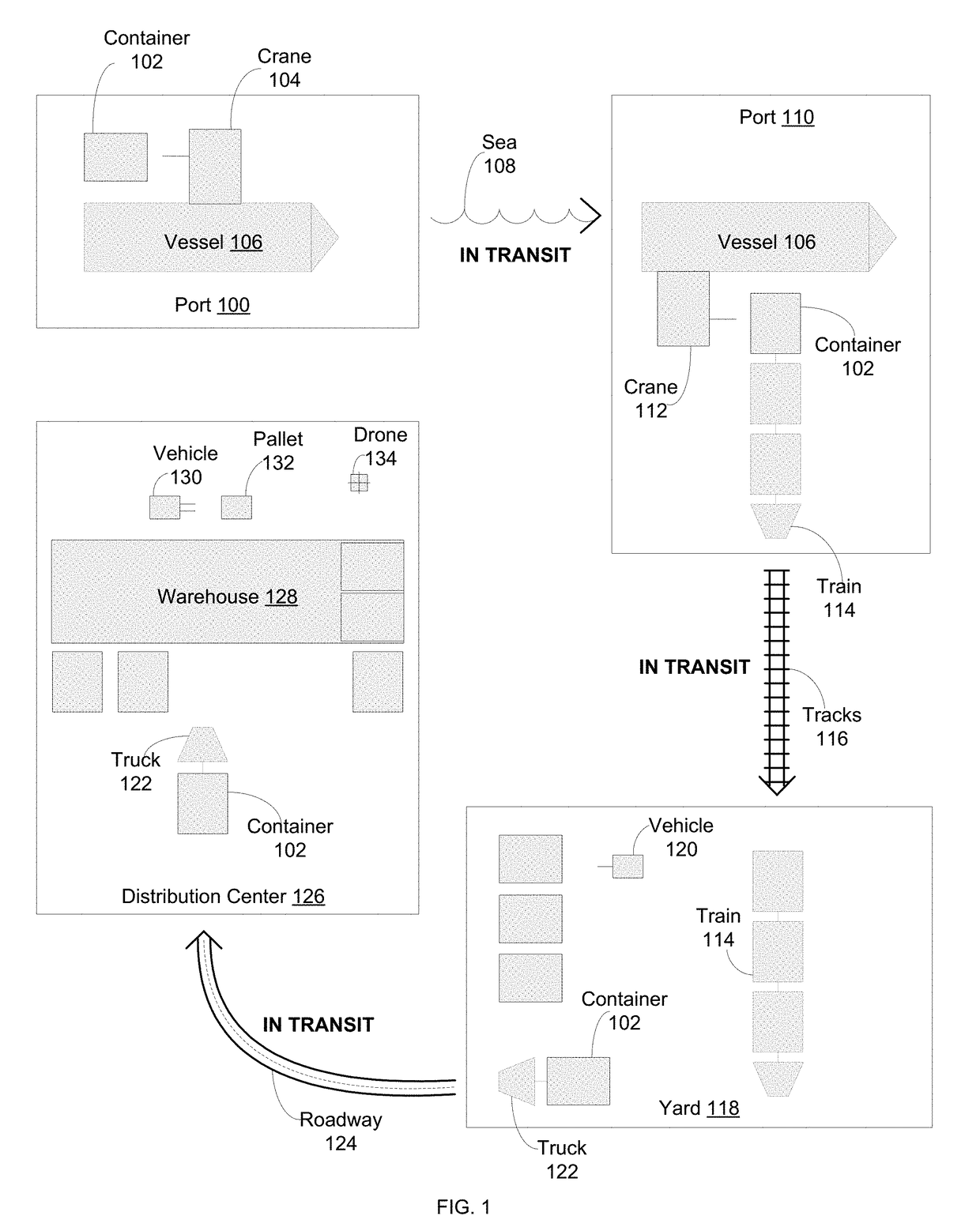

Autonomous supply and distribution chain

ActiveUS20180158020A1Maximise its operationImprove performanceInstruments for road network navigationLogisticsPaymentInvoice

Methods and systems for an autonomous supply and distribution chain management network are disclosed. A server may control and coordinate the processes involved in distributing a product from suppliers to the customers, including generation of purchase orders and payment of invoices. A defined set of interactions may occur in a particular sequence and at designated times that may permit the chain to be synchronized between a customer and a supplier. Unlike a regular supply and distribution chain, in which human beings decide vehicle or asset compatibility types, the autonomous chain of the present invention may maintain a compatibility database within the platform, as well as detailed information about each asset and how it can function interactively with the others. The invention may also allow for dynamic modification of transit operations to alter one or more destinations of the inventory while it is in transit to a new location at any time.

Owner:ROUTE4ME INC

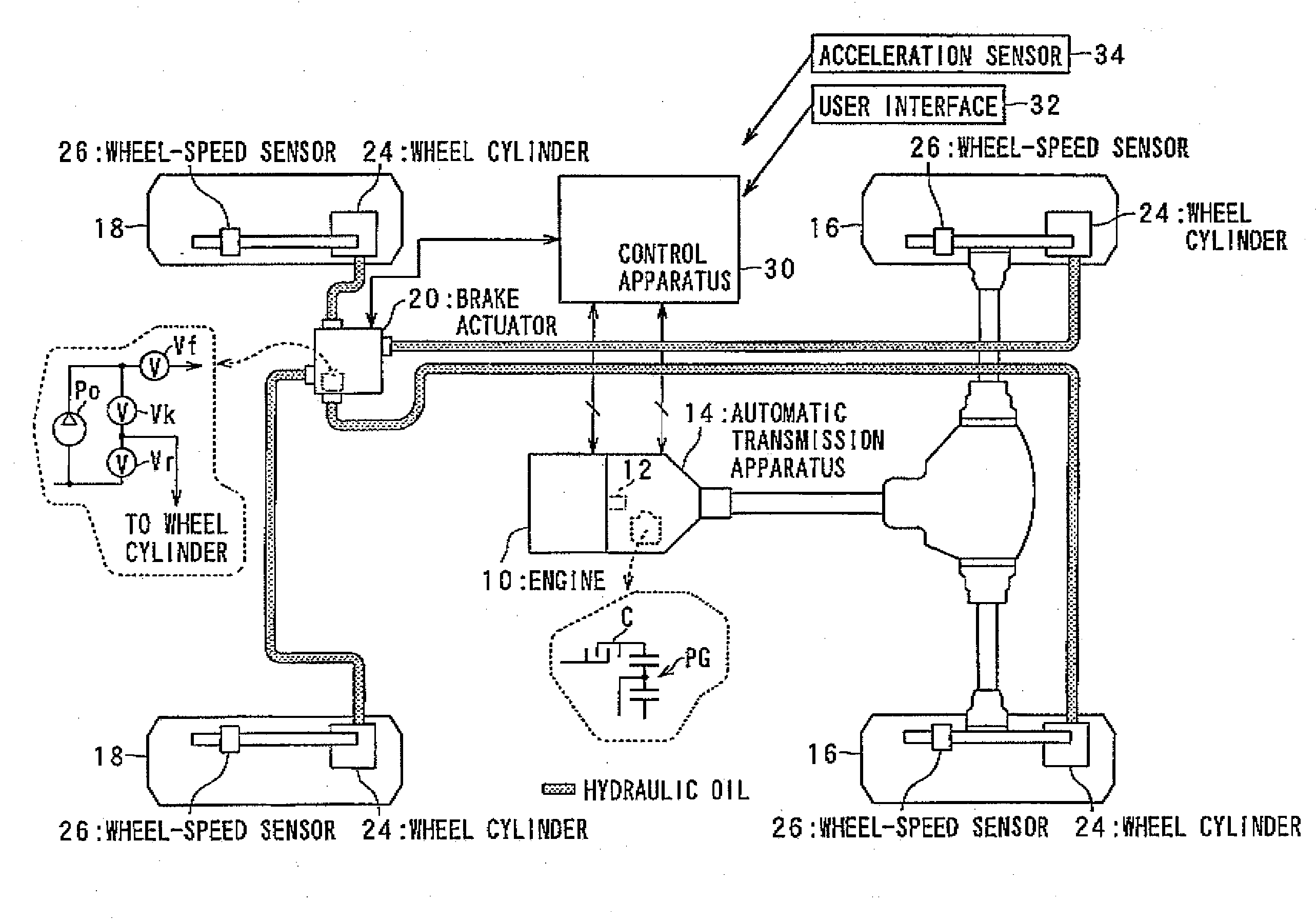

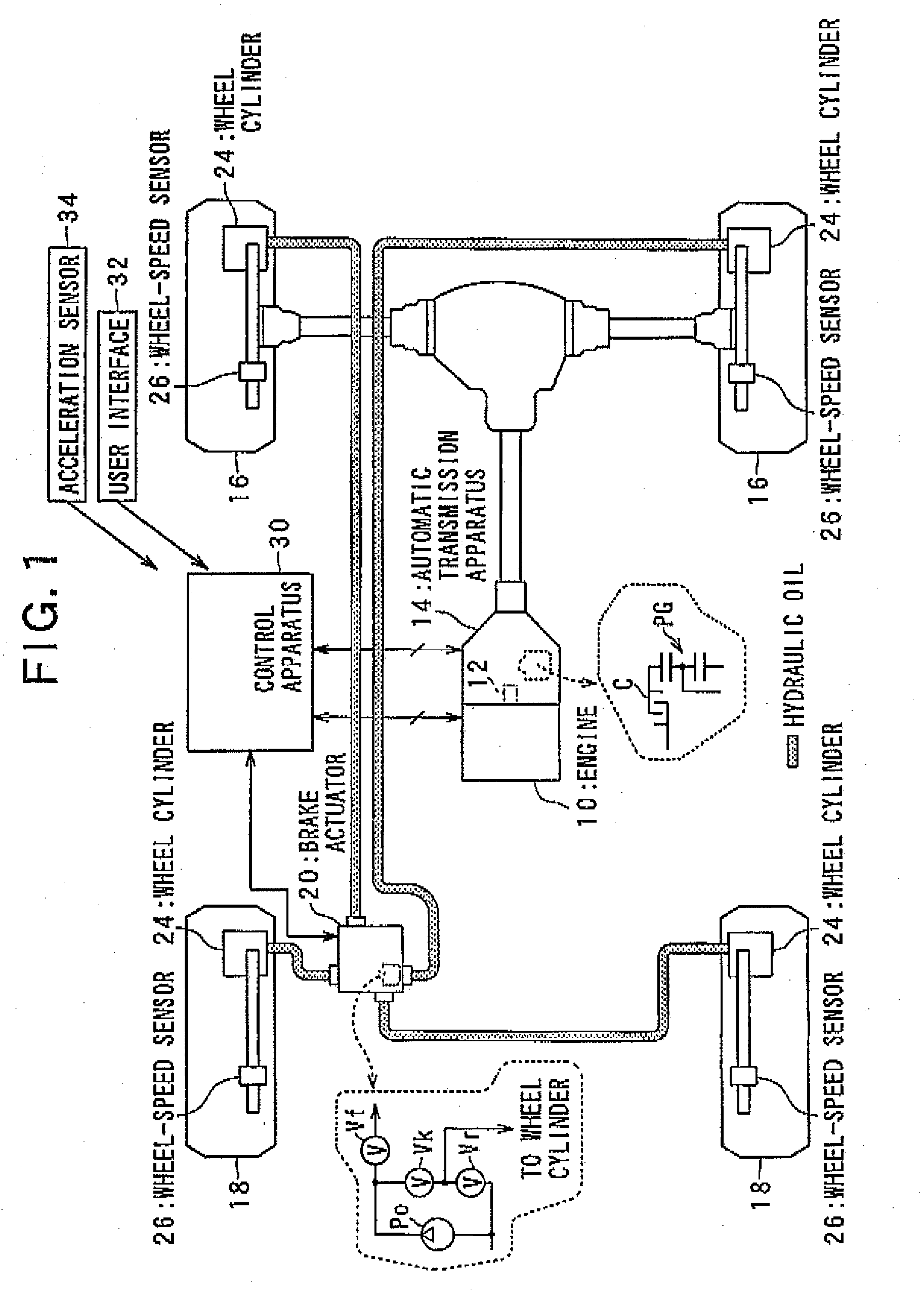

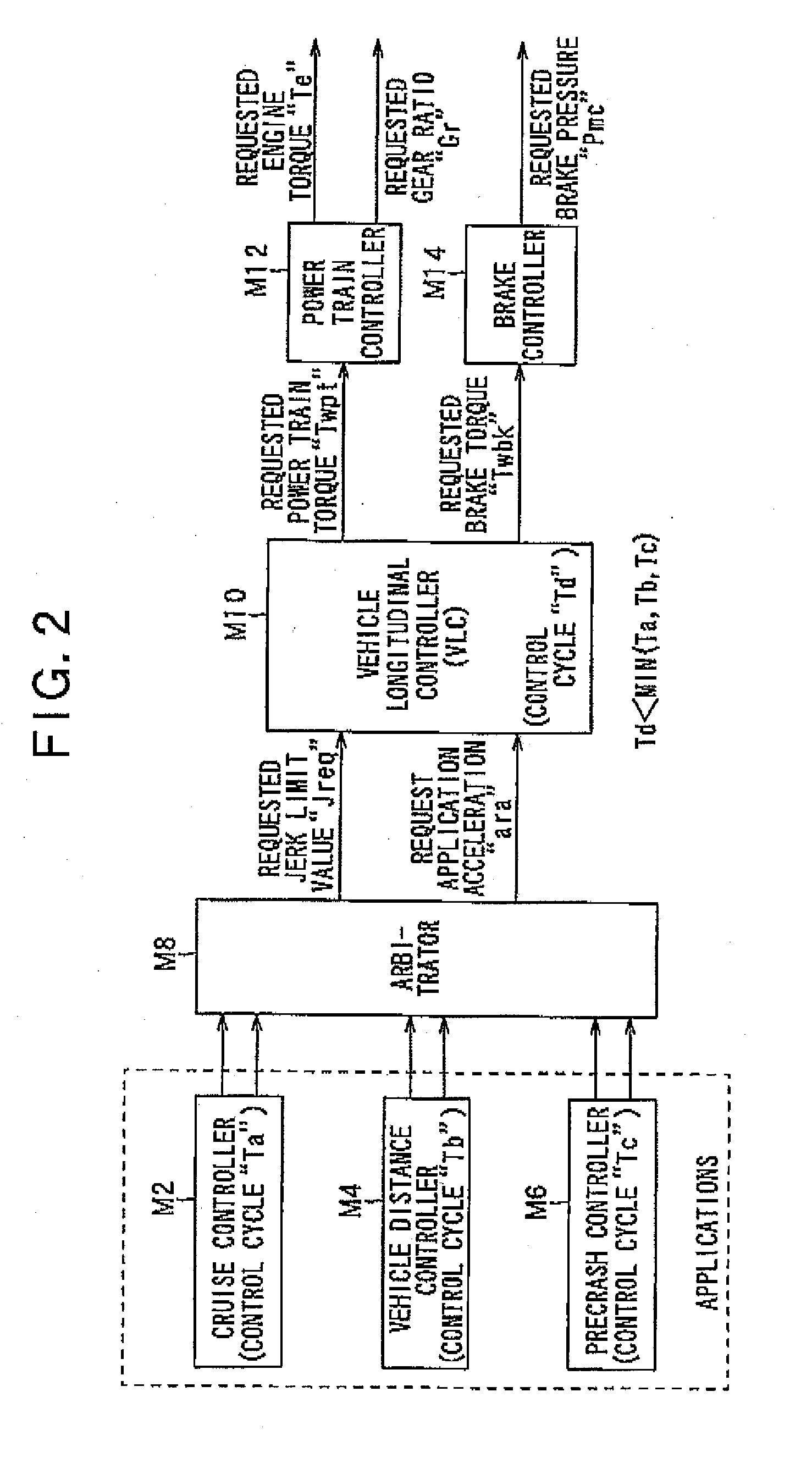

Apparatus for estimating road surface gradient and vehicular control apparatus using the same

InactiveUS20090043473A1Improve travel conditionsImprove ride qualityAnalogue computers for trafficExternal condition input parametersEngineeringRoad surface

An apparatus is provided to estimate a gradient of a road surface on which a vehicle travels. The apparatus comprises acquisition, estimation, and compensation members. The acquisition member acquires at least one of acceleration of the vehicle calculated on changes in a travel speed of the vehicle and acceleration sensed from a force applied to the vehicle. The estimation means estimates the gradient of the road surface based on the acquired acceleration. The compensation member compensates the acquired acceleration in terms of influence of noise superposed on the acceleration, depending on an operational condition of the vehicle. The compensated acceleration is used by the estimation. The compensation is carried out by cutting off the noise by a filter, for example.

Owner:DENSO CORP

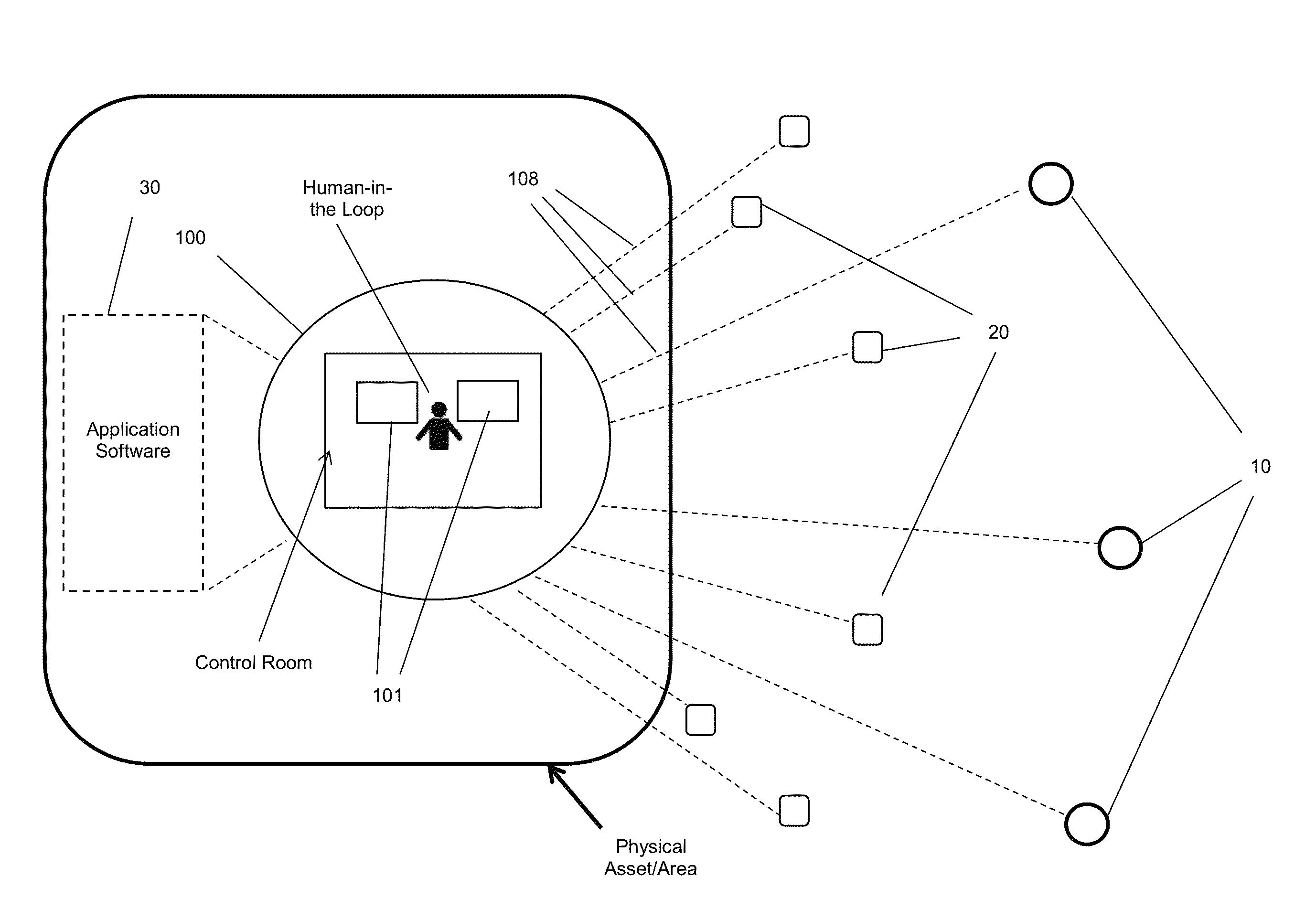

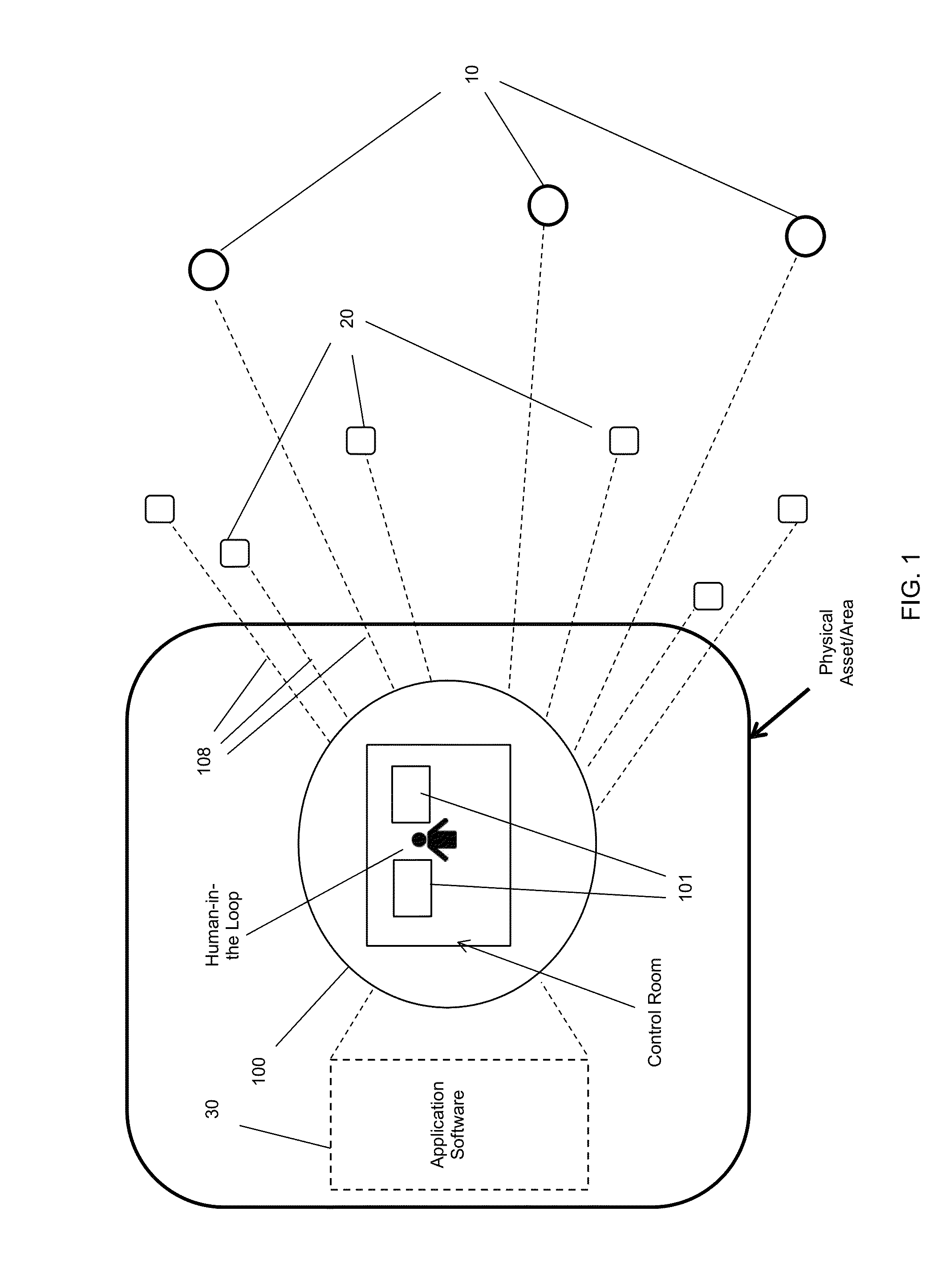

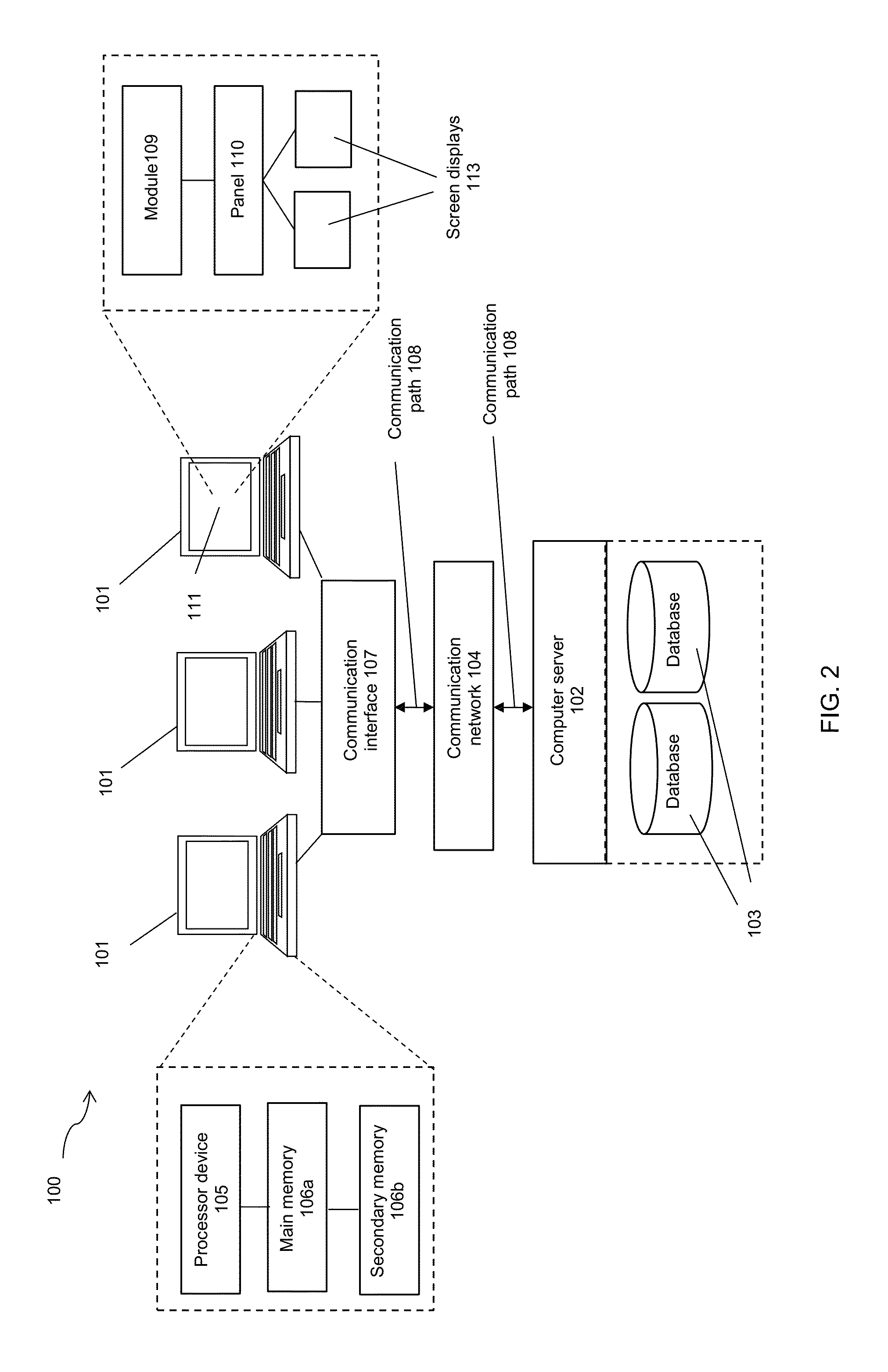

Defense and Denial Method

ActiveUS20150347902A1Effective distributionSignificant delayComputer security arrangementsKnowledge representationCountermeasureApplication software

The presently disclosed method and system includes a network of computer devices, sensors, and actuators operating in concert with application software to actively detect, identify, and localize threats and generate real-time countermeasures designed to delay and / or mitigate damage that may be caused by the threats. Application software, in the form of automated reasoning and logic control, initiates preparatory and countermeasure sequences automatically, which may be used by users or automatically executed by the system to at least delay an attack to a physical asset / area by adversaries with use of non-lethal actuators. Learned scenarios are generated and continuously adapted via feedback loops and decision rules to provide preparatory and countermeasure sequences that maximize results with minimal expenditure of assets.

Owner:THE SECURITY ORACLE

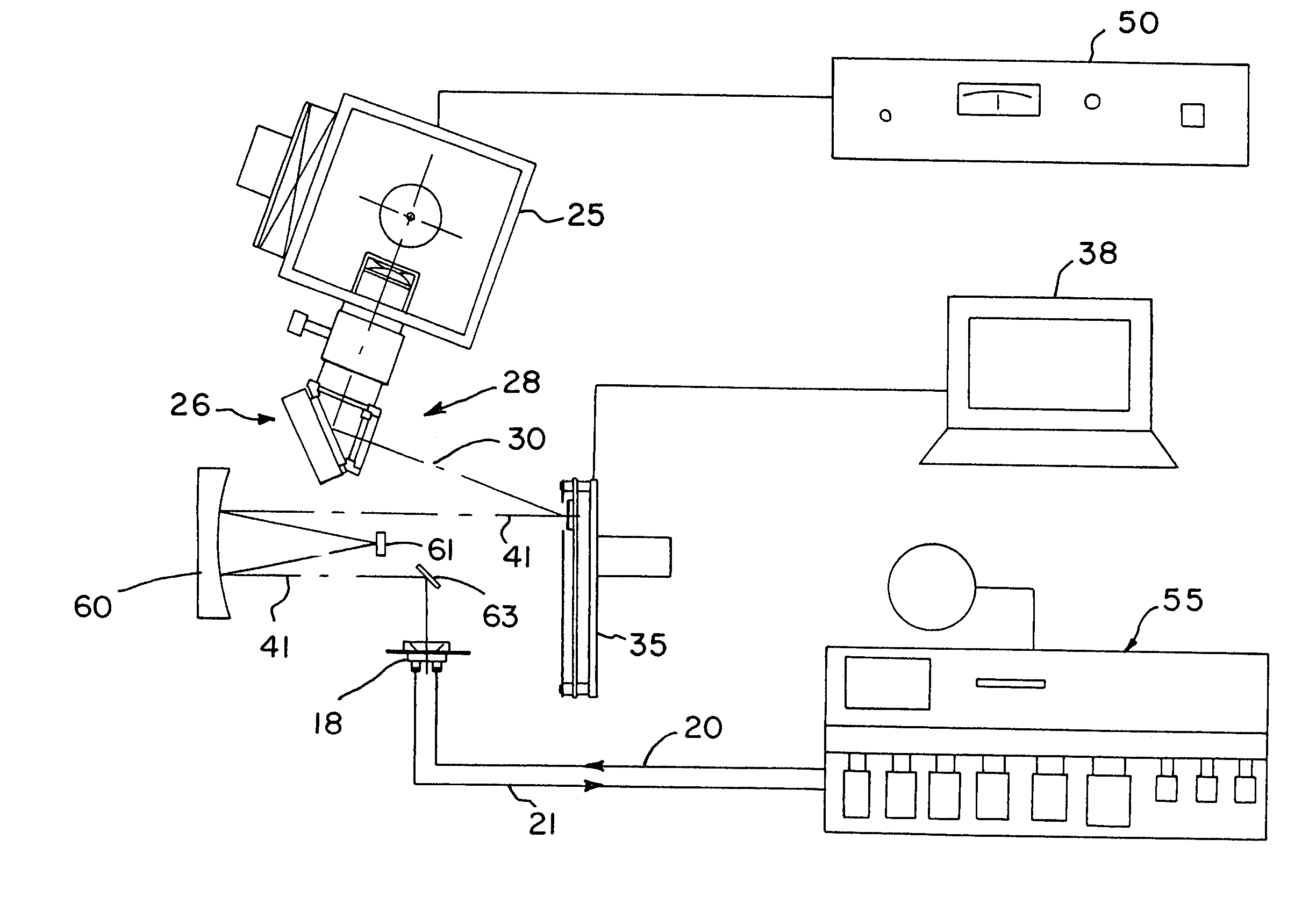

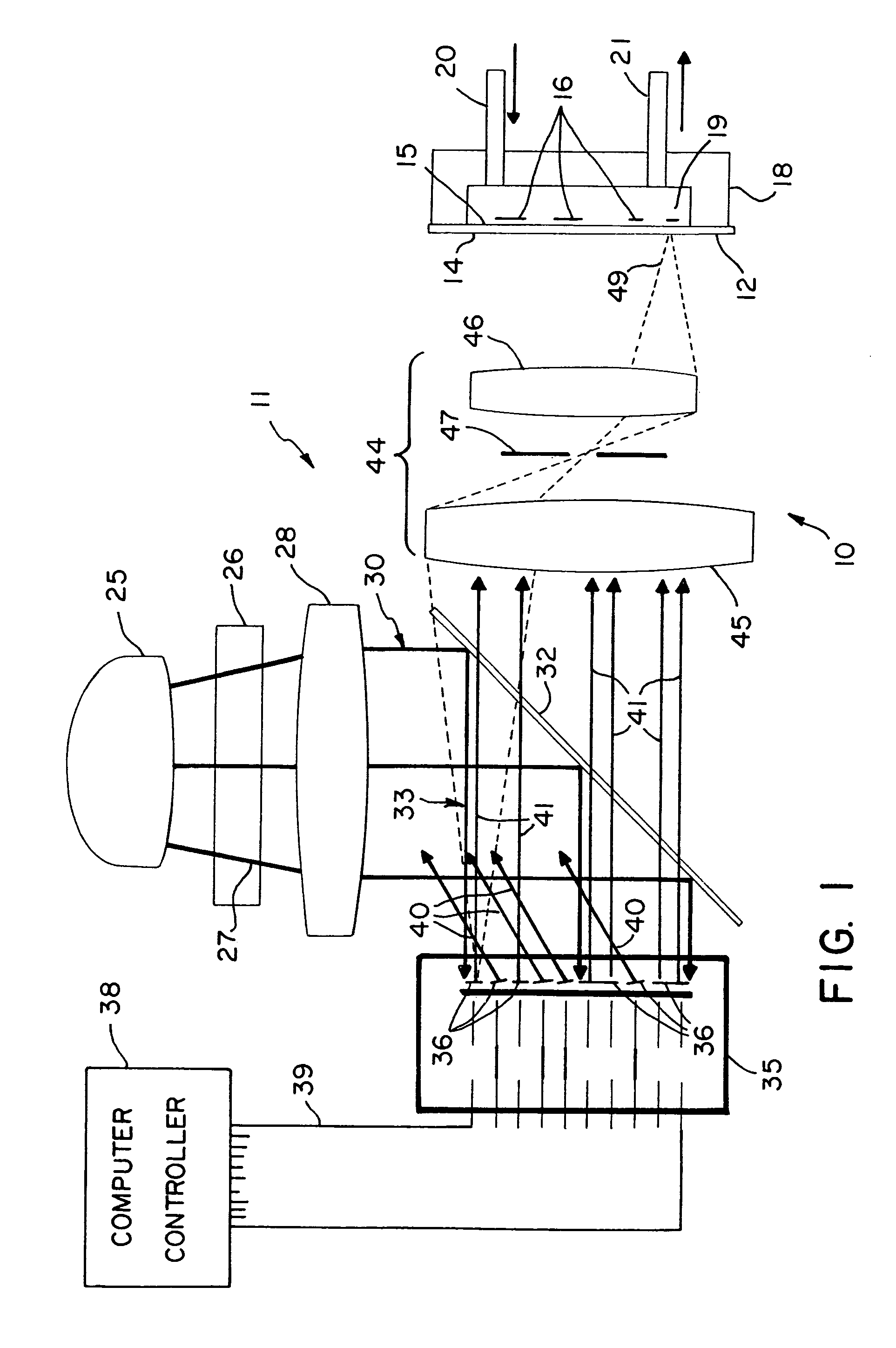

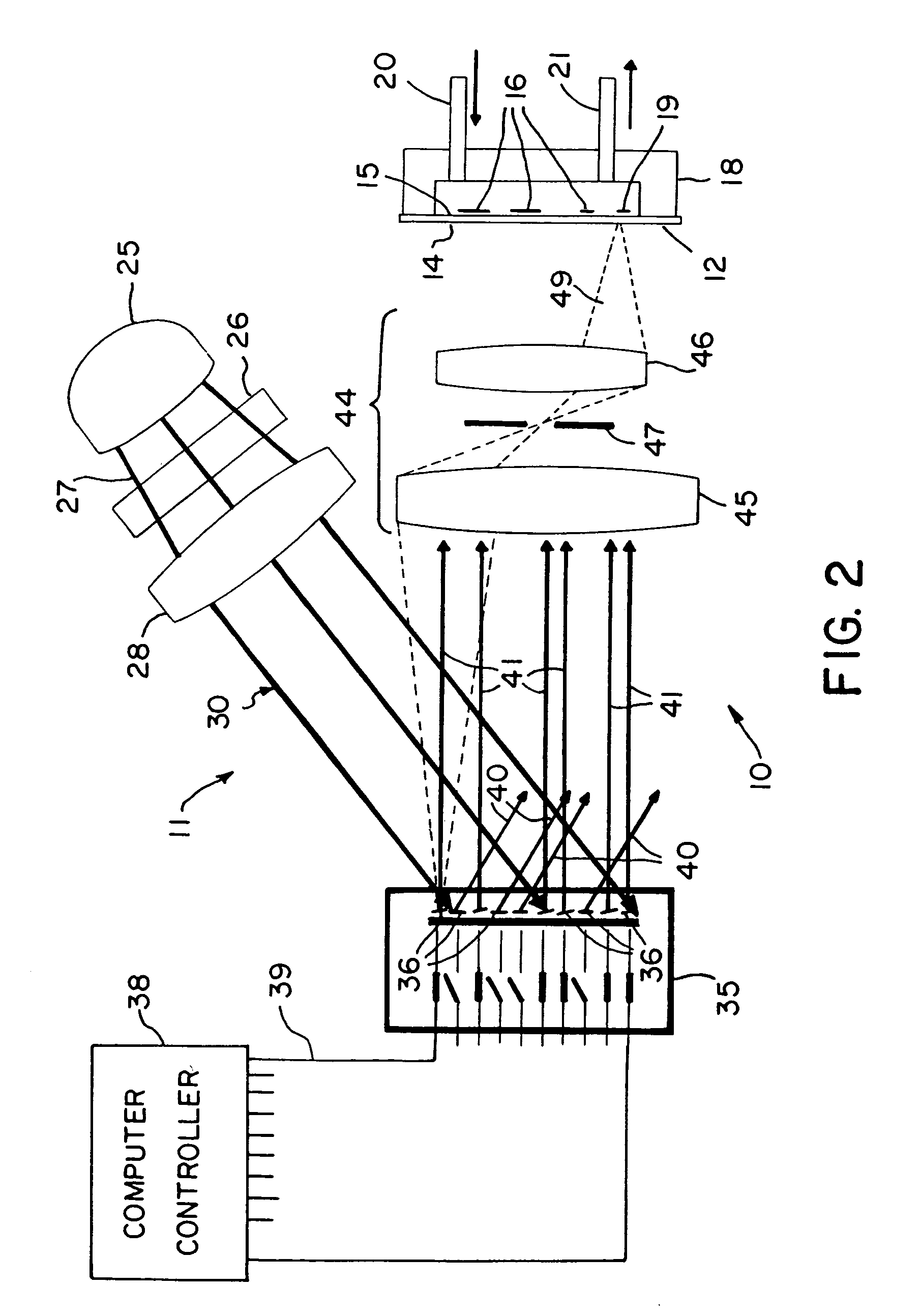

Methods for the synthesis of arrays of DNA probes

InactiveUS8030477B2Avoid time-consuming operationsSignificant costBioreactor/fermenter combinationsMaterial nanotechnologyProjection opticsDNA

The synthesis of arrays of DNA probes sequences, polypeptides, and the like is carried out using a patterning process on an active surface of a substrate. An image is projected onto the active surface of the substrate utilizing reflective projection optics. The projection optics project a light image onto the active surface of the substrate to deprotect linker molecules thereon. A first level of bases may then be applied to the substrate, followed by development steps, and subsequent exposure of the substrate utilizing a different light image, with further repeats until the elements of a two dimensional array on the substrate surface have an appropriate base bound thereto.

Owner:WISCONSIN ALUMNI RES FOUND

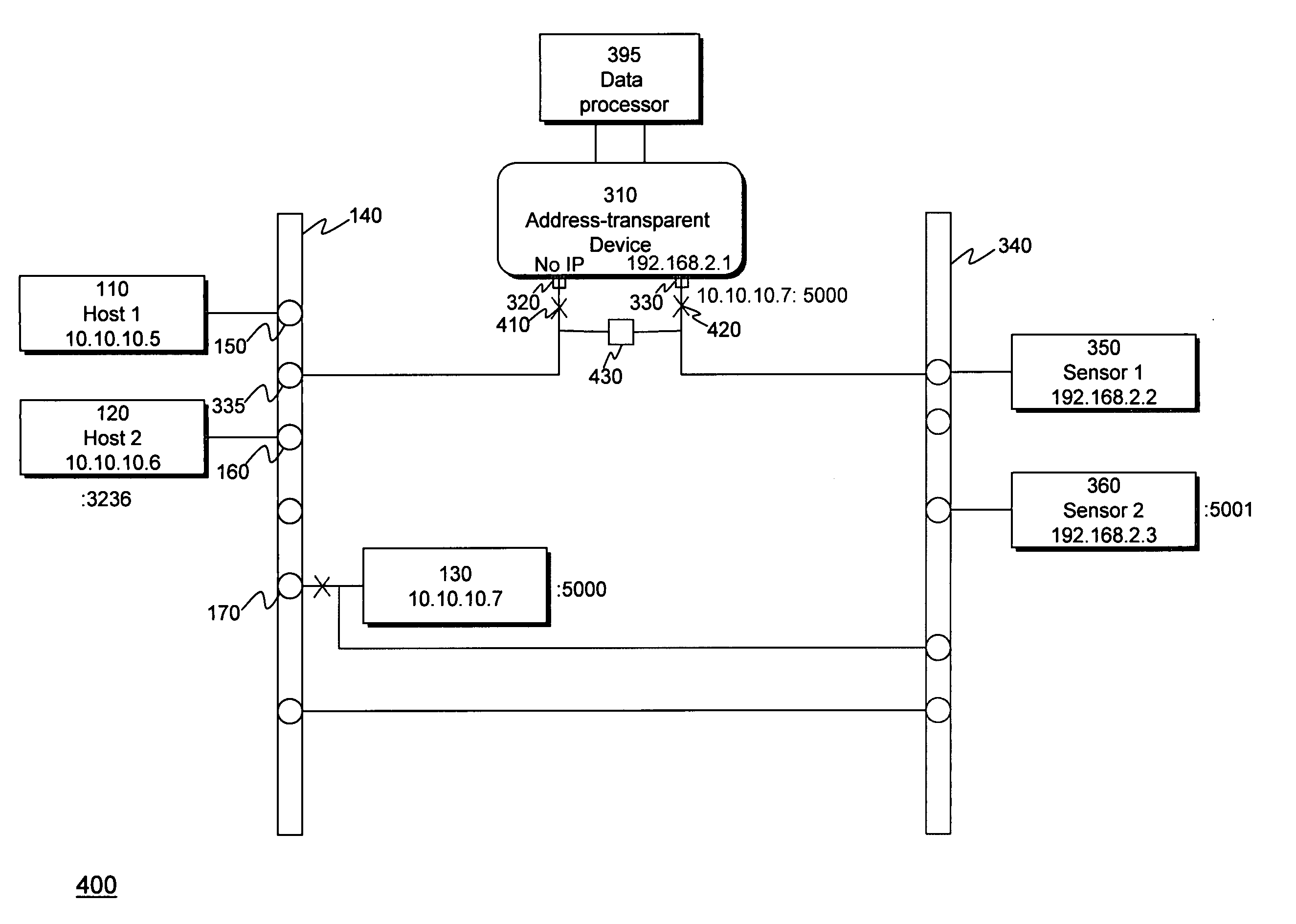

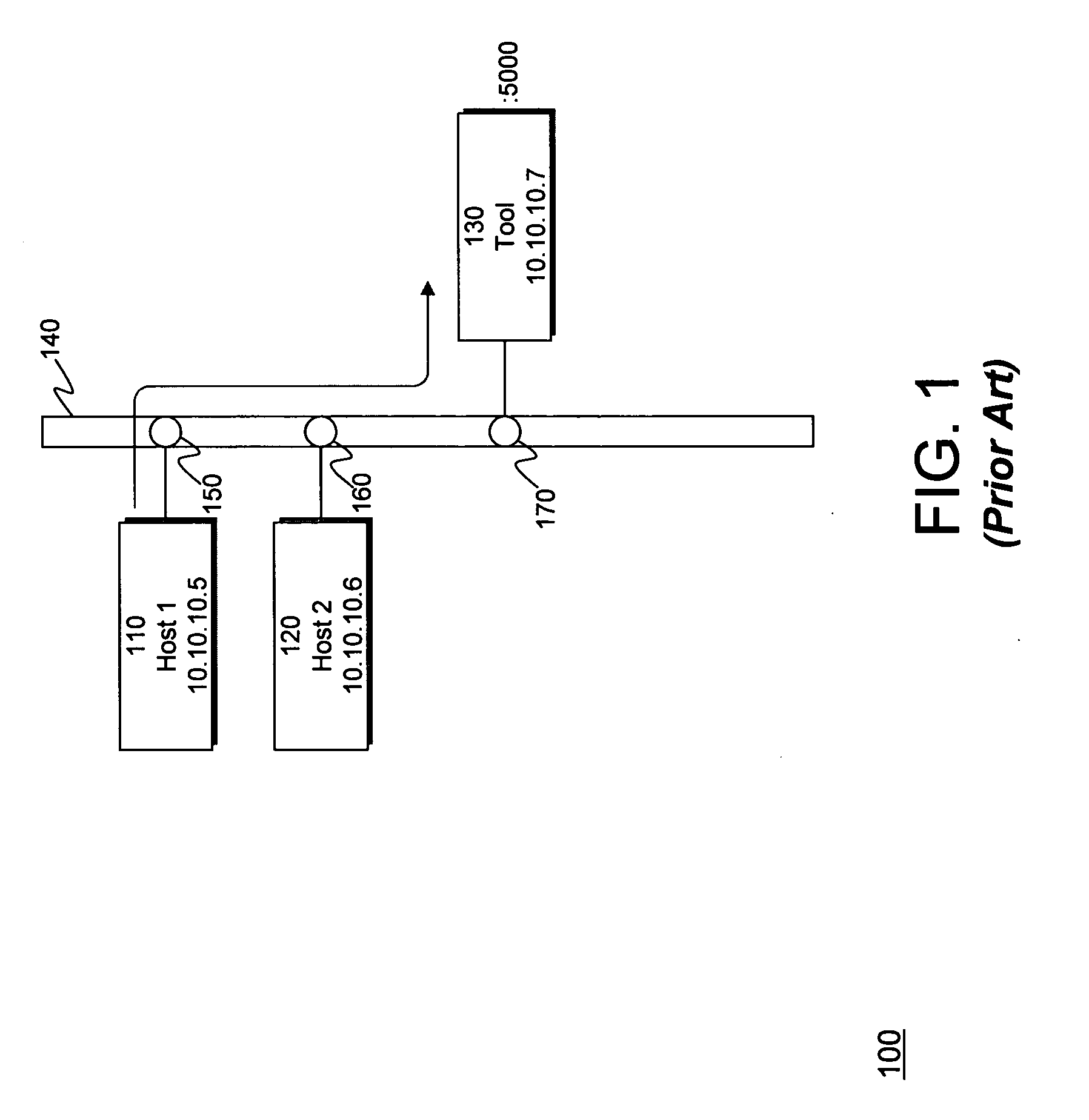

Address-transparent device and method

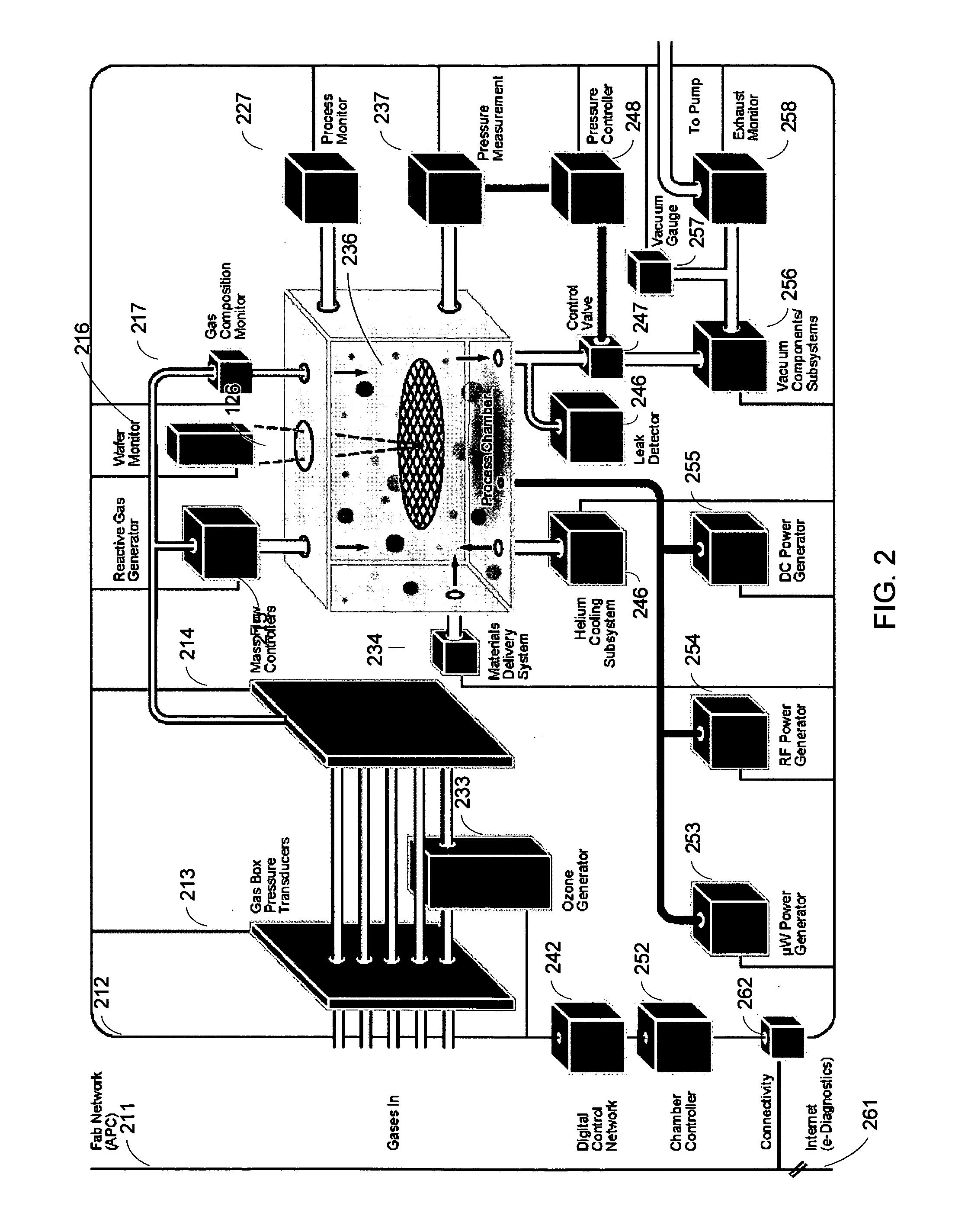

ActiveUS20070008972A1Significant delaySignificant feeSemiconductor/solid-state device manufacturingData switching by path configurationData streamIp address

An address-transparent device is disclosed that couples between two network interfaces in a semiconductor fab for communicating packets between a host coupled to a first network interface and a tool coupled to a second network interface. Alternatively, the address-transparent device couples between two networks in a semiconductor fab for communicating packets between a host on a first network and a tool on a second network. In a first aspect of the invention, the address-transparent device routes packets between the first network and the second network that is independent of any protocol. The address-transparent device couples to the host through the first network and couples to the tool through the second network where the address-transparent device having a first port with no IP address and a second port with a subnet IP address. In a second aspect of the invention, the address-transparent device intercepts packets for local use by a data consumer that resides within or outside of the address-transparent device. The address-transparent device can intercept all or a portion of data streams, while forwards other portions of data streams to a destination. The header of the original packet is stored for subsequent use for sending a reply to an intercepted packet. In a third aspect of the invention, the address-transparent device reroutes packet to another destination by changing the header of the received packet. The header of the original packet is modified, replacing the original header information with the header information of the destination device. The header of the original packet is stored for subsequent use for sending a reply to a rerouted packet.

Owner:MKS INSTR INC

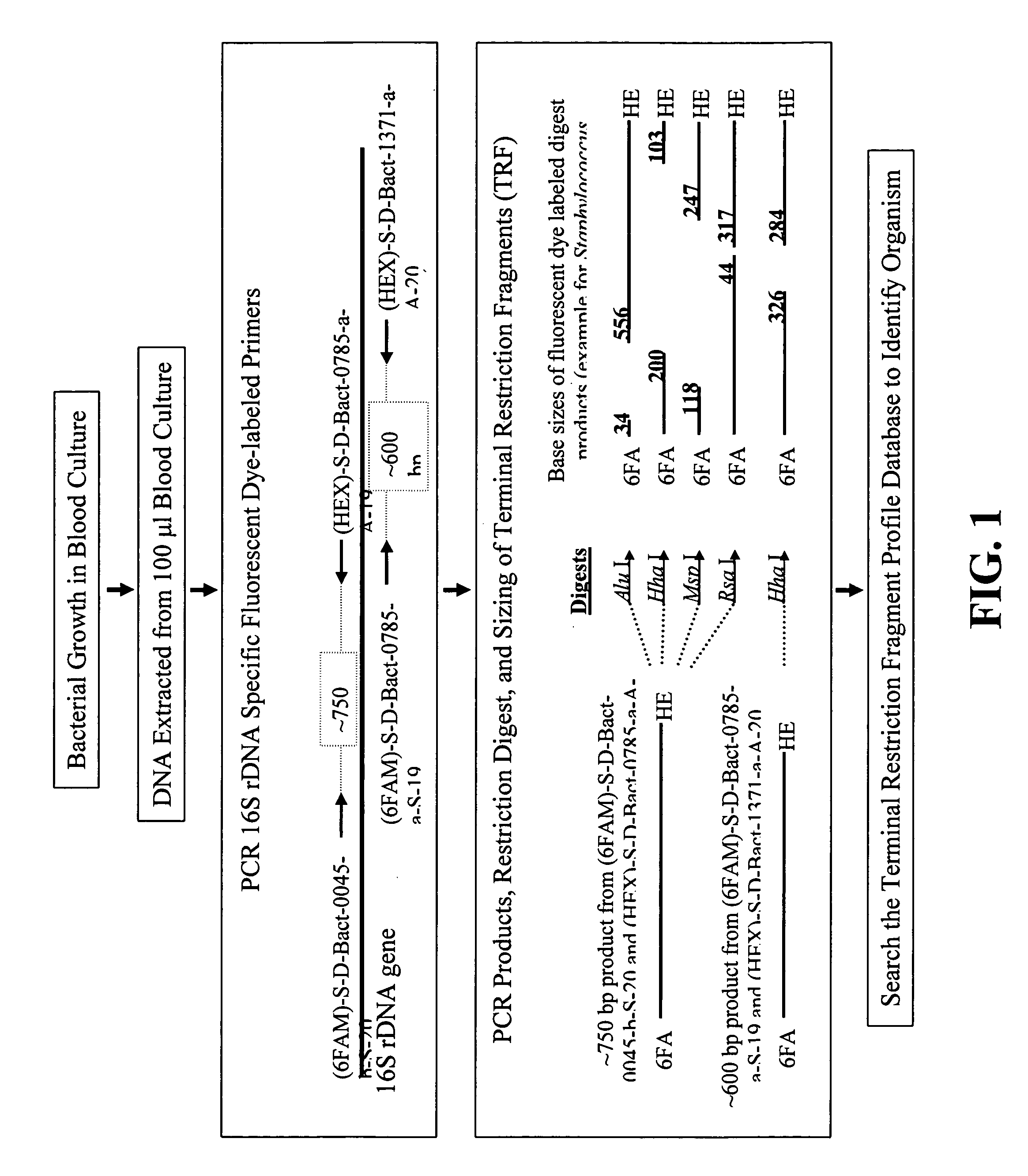

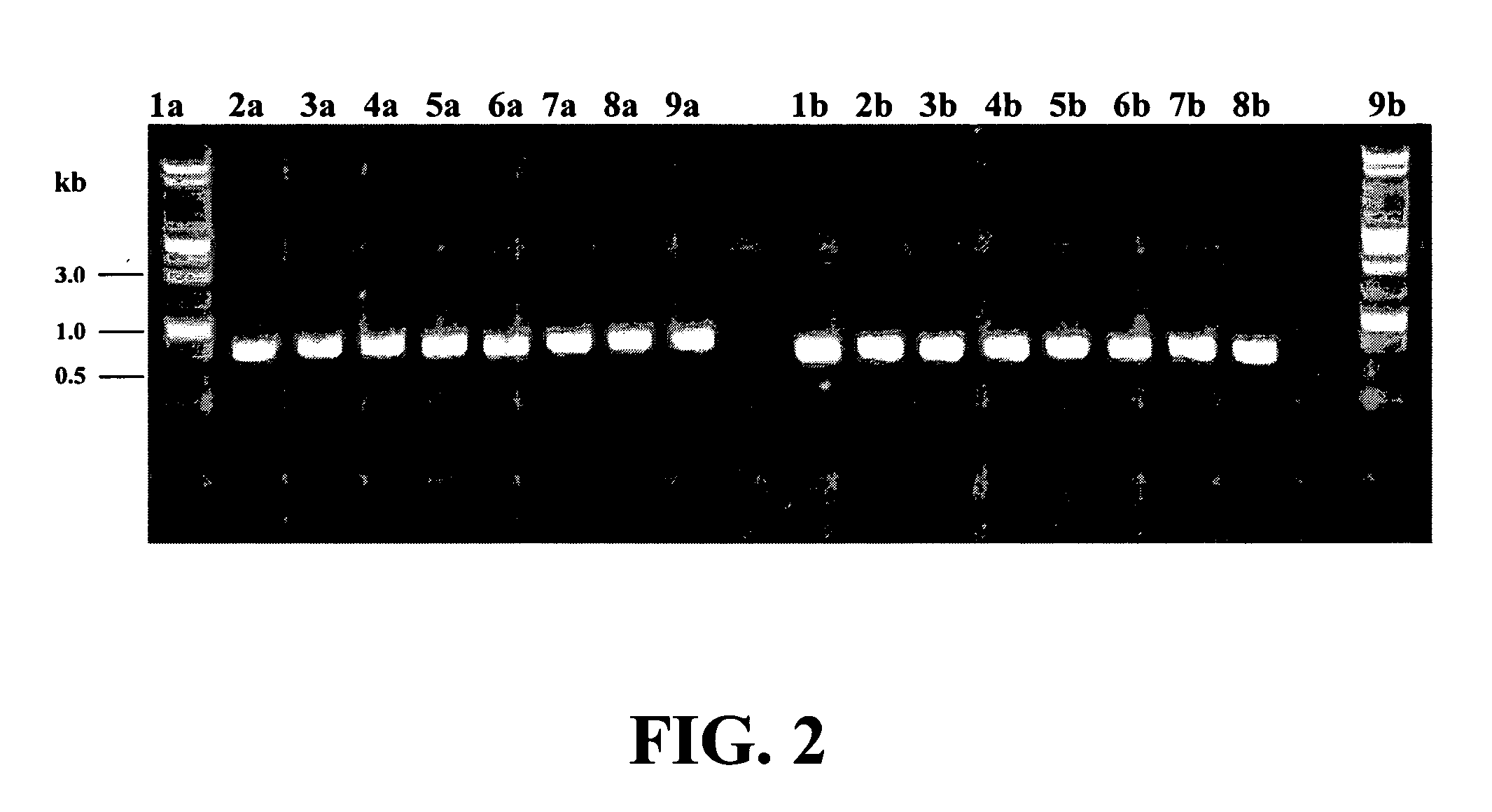

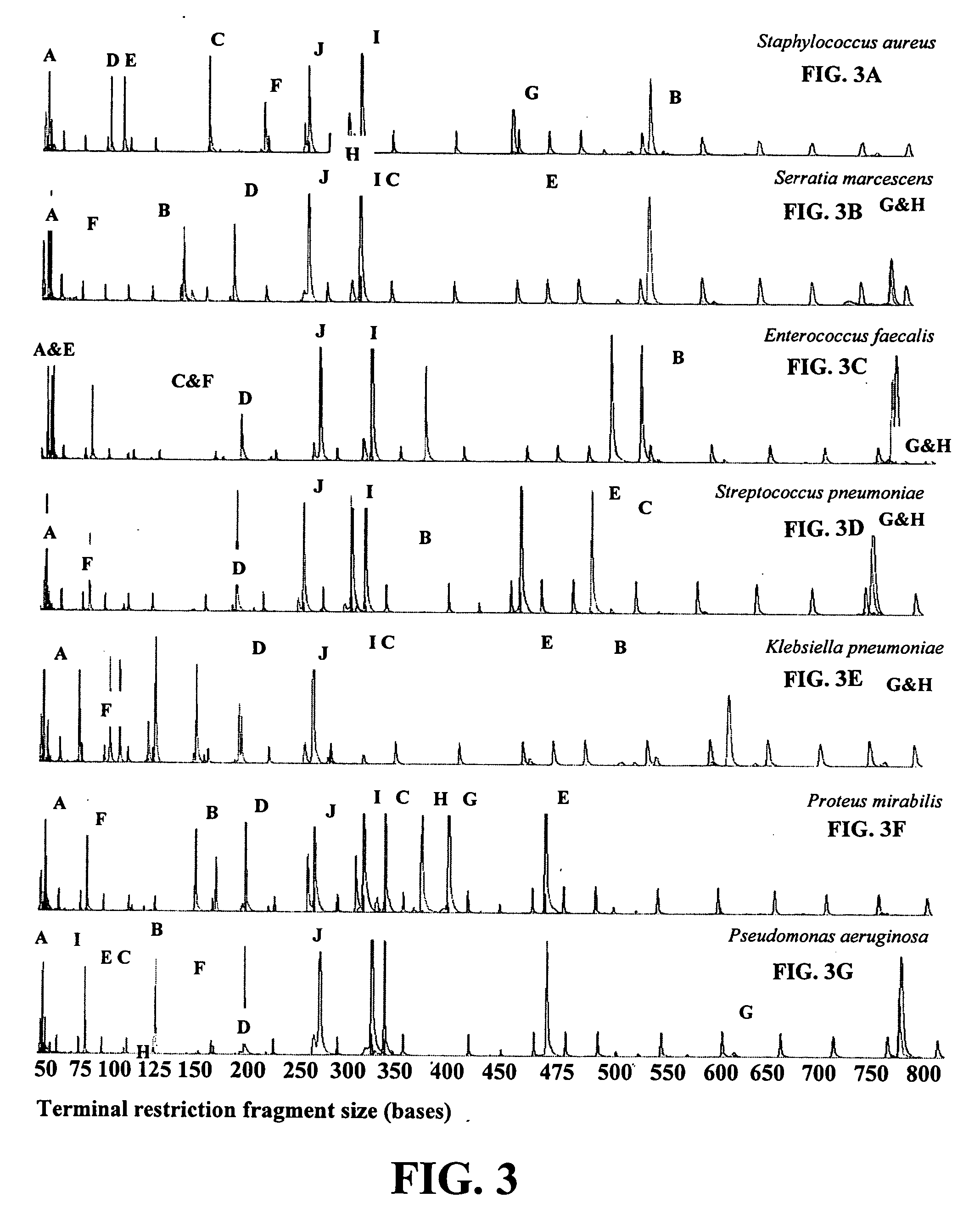

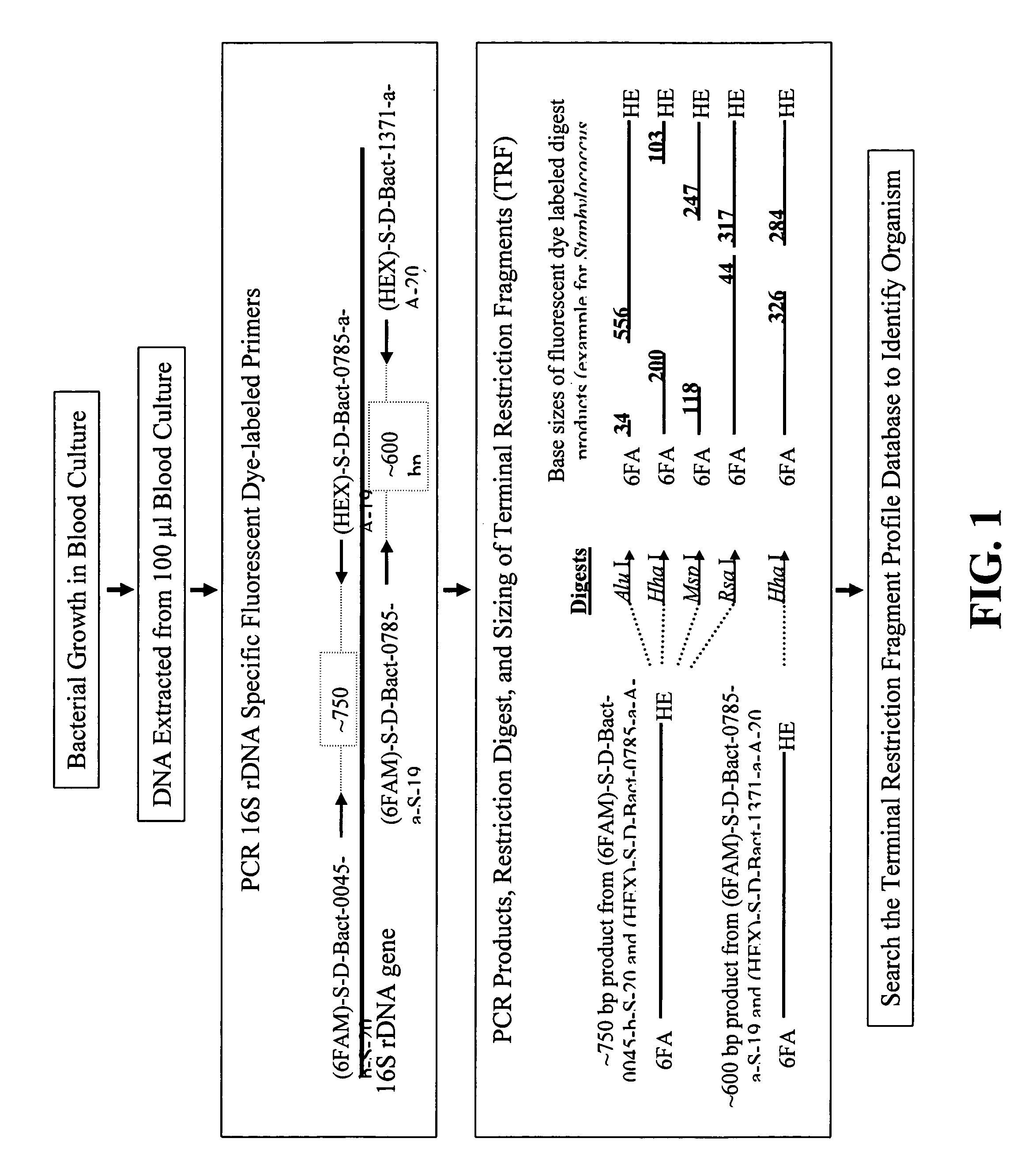

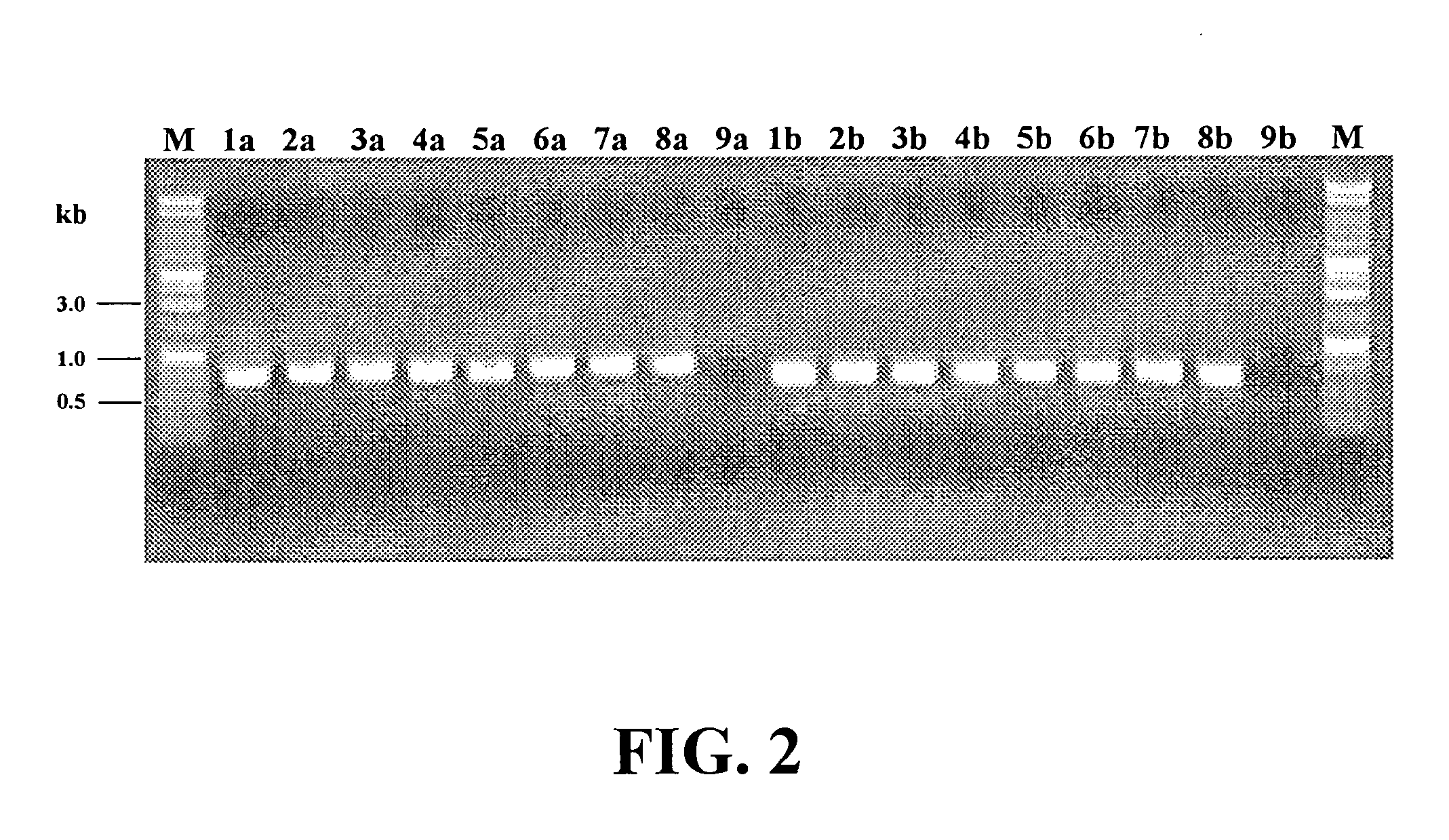

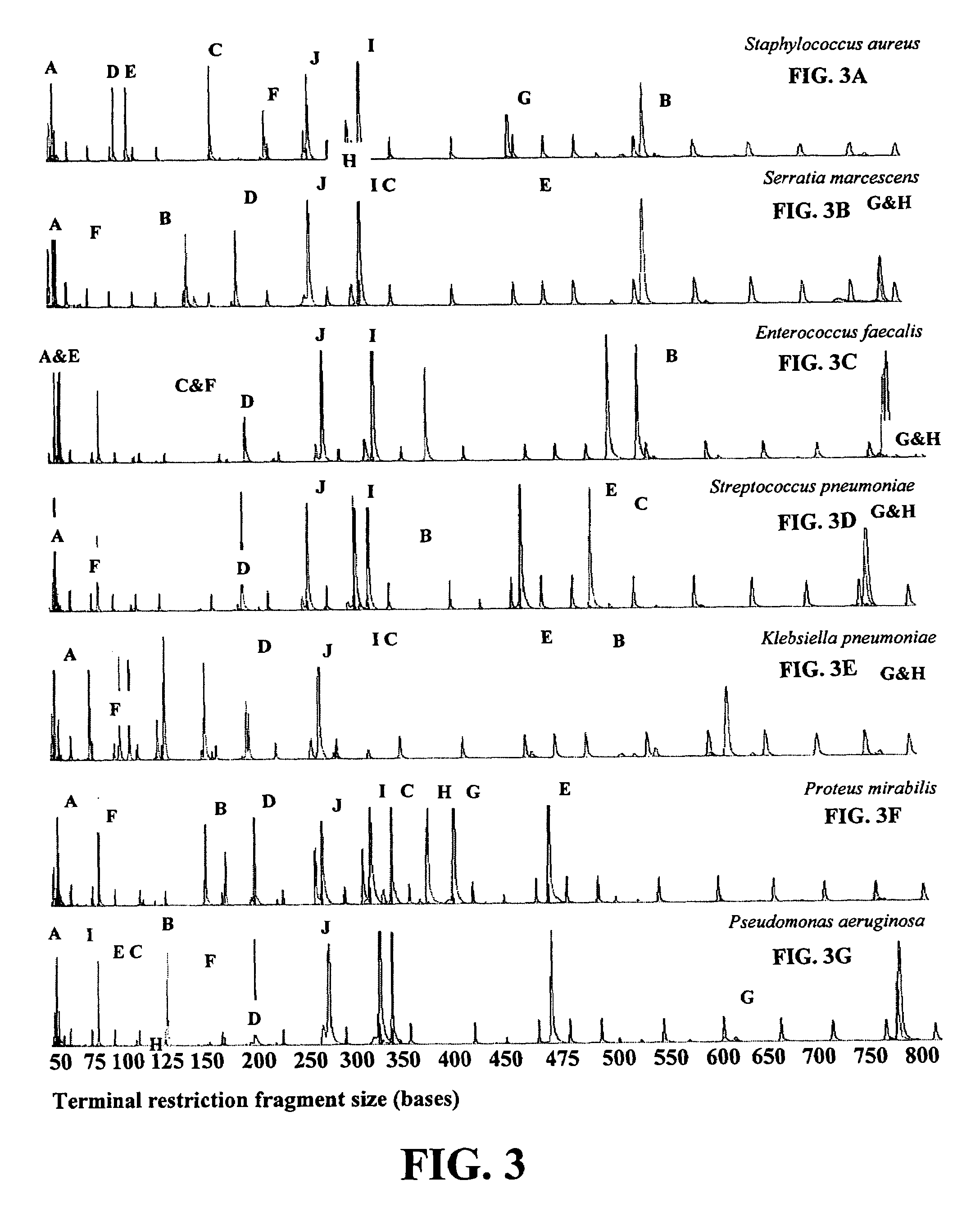

Rapid identification of bacteria from positive blood cultures

InactiveUS20050037408A1Reduce unnecessary useAvoid developmentMicrobiological testing/measurementBiological testingRapid identificationPositive blood culture

Disclosed is a method of detecting bacteria in a biological sample, especially a blood sample, without the need for extensive sub-culturing of the sample. Nucleic acid present within the sample is isolated and bacterial DNA specifically amplified using primers that uniquely prime the amplification of 16s rRNA-encoding nucleic acid. The amplicons are then digested with an endonuclease to yield a restriction fragment length profile for the biological sample. The restriction fragment length profile for the biological sample is then compare to a database of profiles made using cultures of known bacterial species. A match between the sample profile and the database quickly identifies the bacteria present in the sample.

Owner:MARSHFIELD CLINIC

Optimizing integrated circuit design through use of sequential timing information

InactiveUS7743354B2Increase flexibilityEasy to implementCAD circuit designSoftware simulation/interpretation/emulationTiming marginMaximum latency

A method is provided that includes: determining a minimum clock cycle that can be used to propagate a signal about the critical cycle in a circuit design; wherein the critical cycle is a cycle in the design that has a highest proportionality of delay to number of registers; determining for a circuit element in the circuit design, sequential slack associated with the circuit element; wherein the sequential slack represents a minimum delay from among respective maximum delays that can be added to respective structural cycles of which the circuit element is a constituent, based upon the determined limit upon clock cycle duration; using the sequential slack to ascertain sequential optimization based design flexibility throughout multiple stages of a design flow.

Owner:CADENCE DESIGN SYST INC

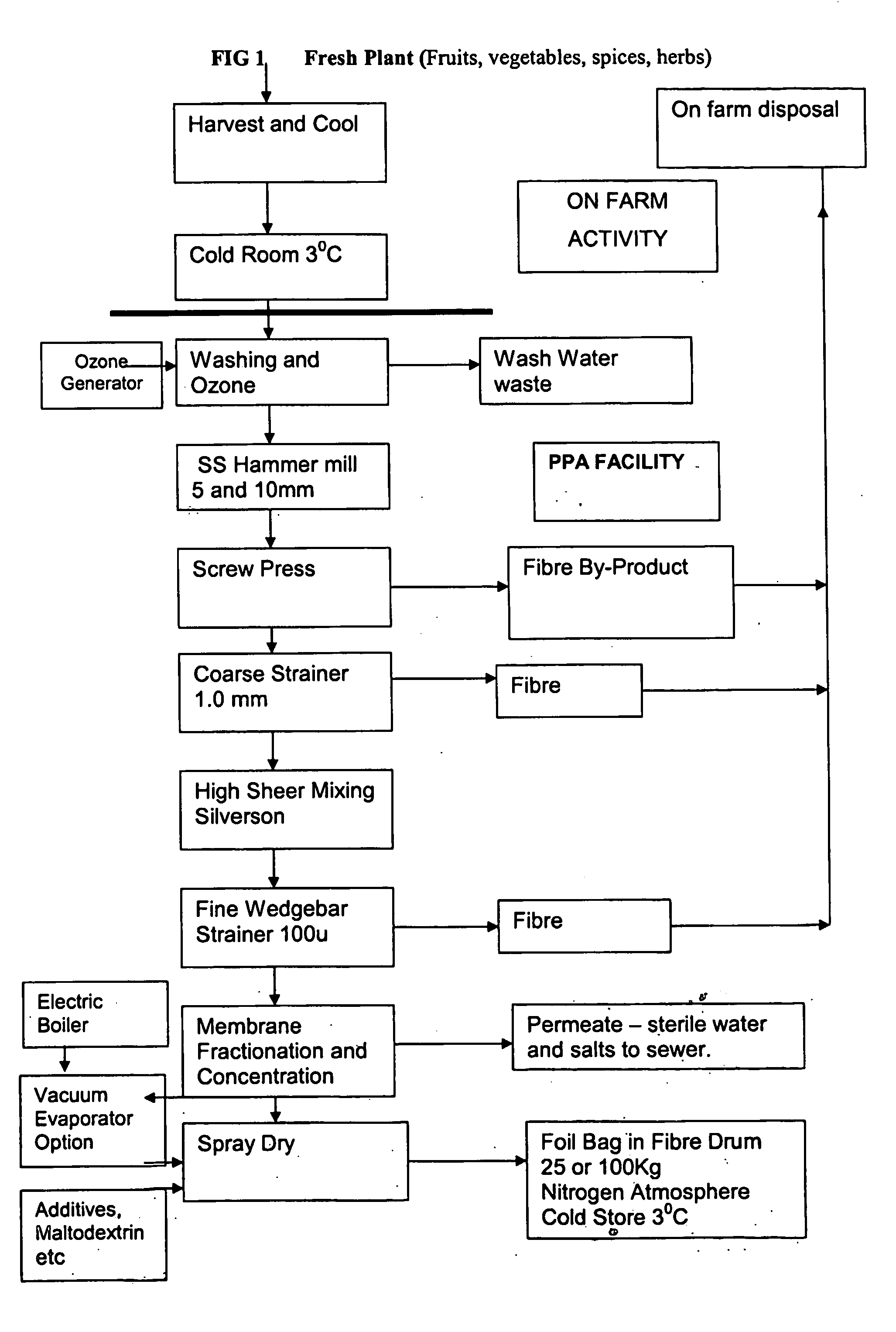

Process and apparatus for modifying plant extracts

InactiveUS20060147556A1Inhibit deteriorationPrevent and to reduce deteriorationBiocideAnimal repellantsFruit juicePlant cell

Phytonutrients or other active materials can be extracted from plant material using a particular process which requires extracting juice from the plant material, followed by breaking open the plant cells to release the phytonutrients by subjecting the juice to high shear conditions, followed by concentrating the juice using a membrane which is preferably a nanofiltration membrane, and collecting the concentrated extract which can then be spray dried info a powder and used as a nutritional supplement, or which can be further extracted using supercritical carbon dioxide to provide an even more concentrated product. The process is designed to maintain a high levels of phytonutrients in the active condition and to reduce plant and equipment costs especially in the use of supercritical carbon dioxide.

Owner:CALTHAPHARM AUSTRALIA

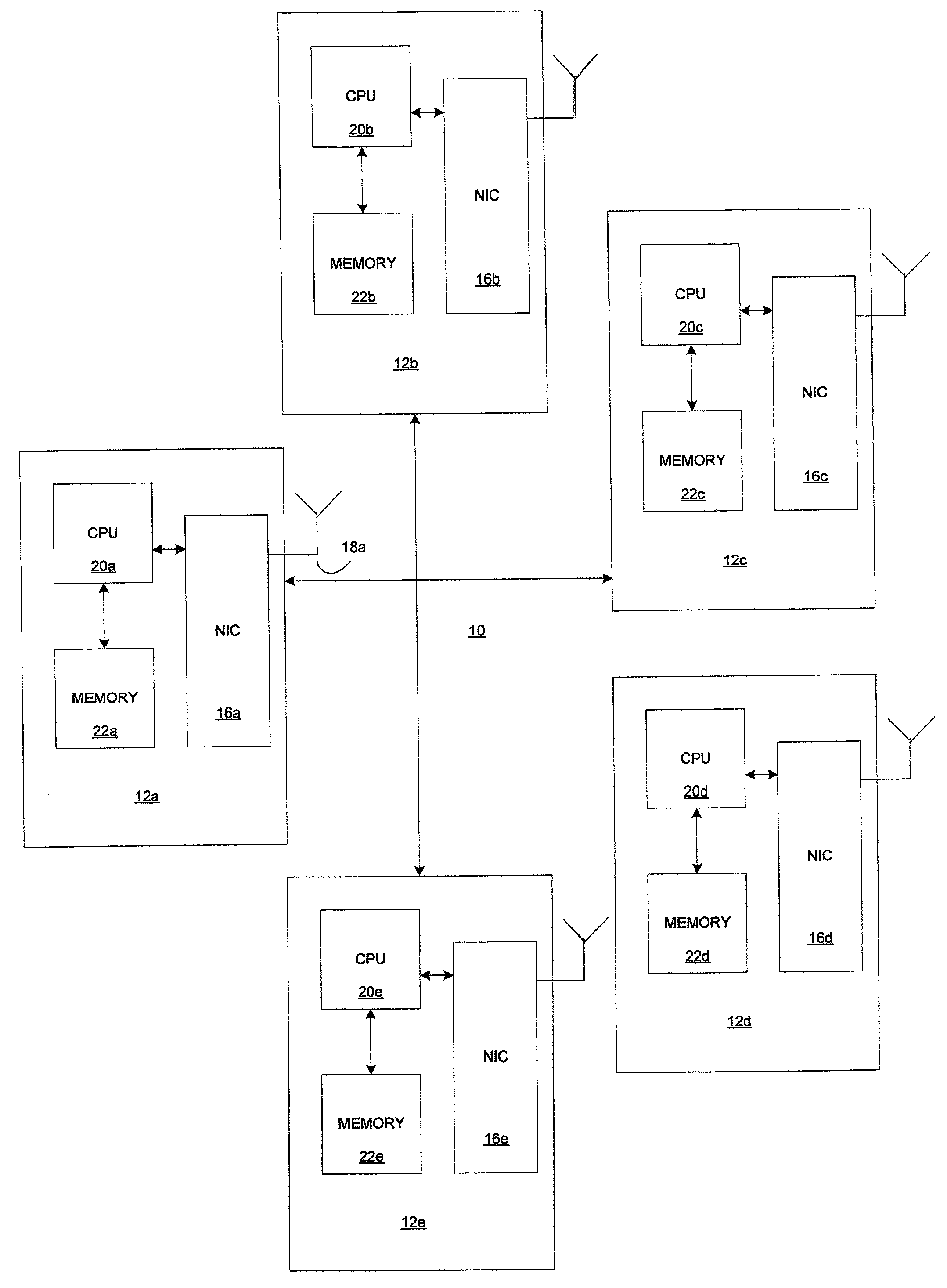

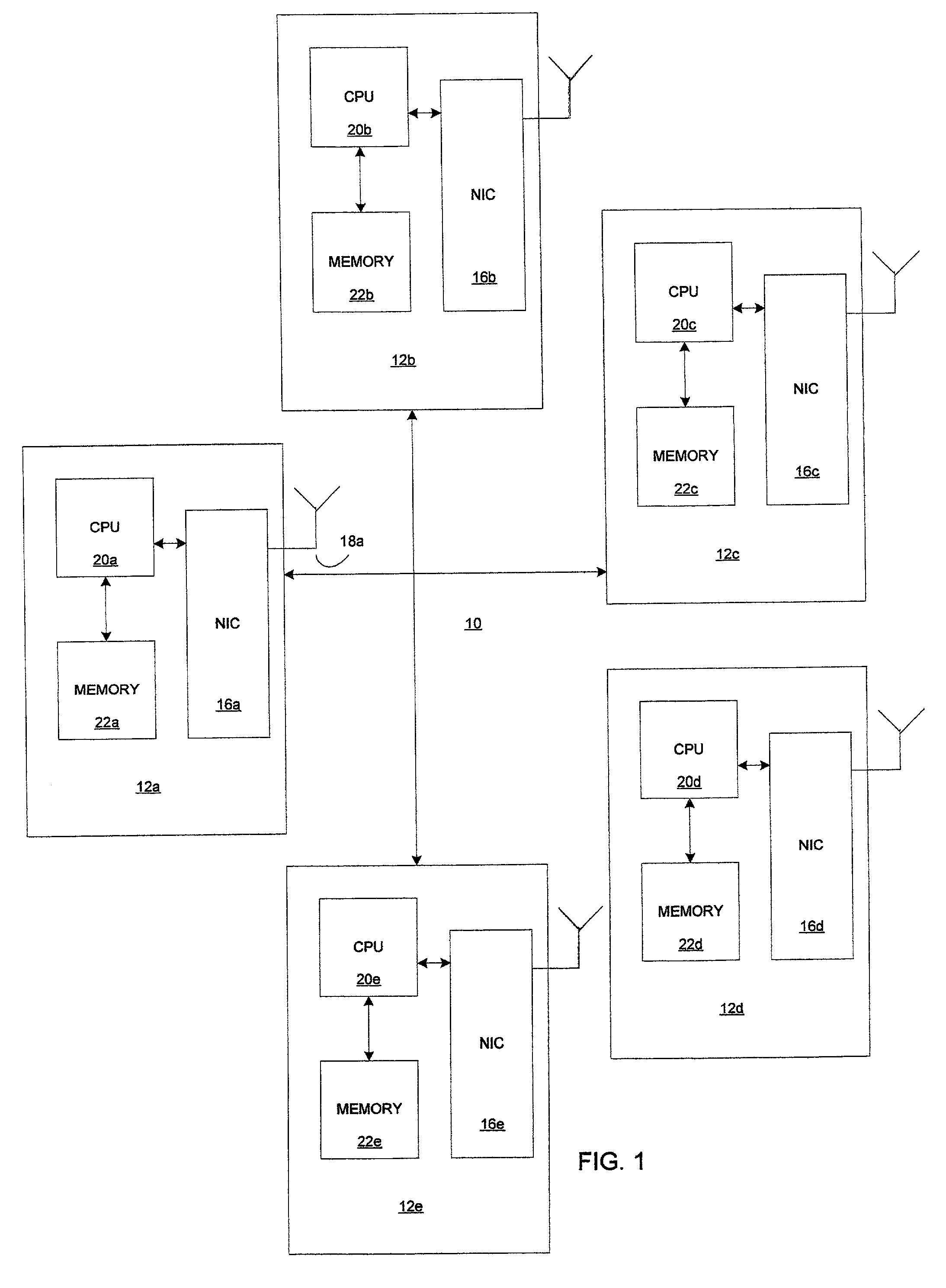

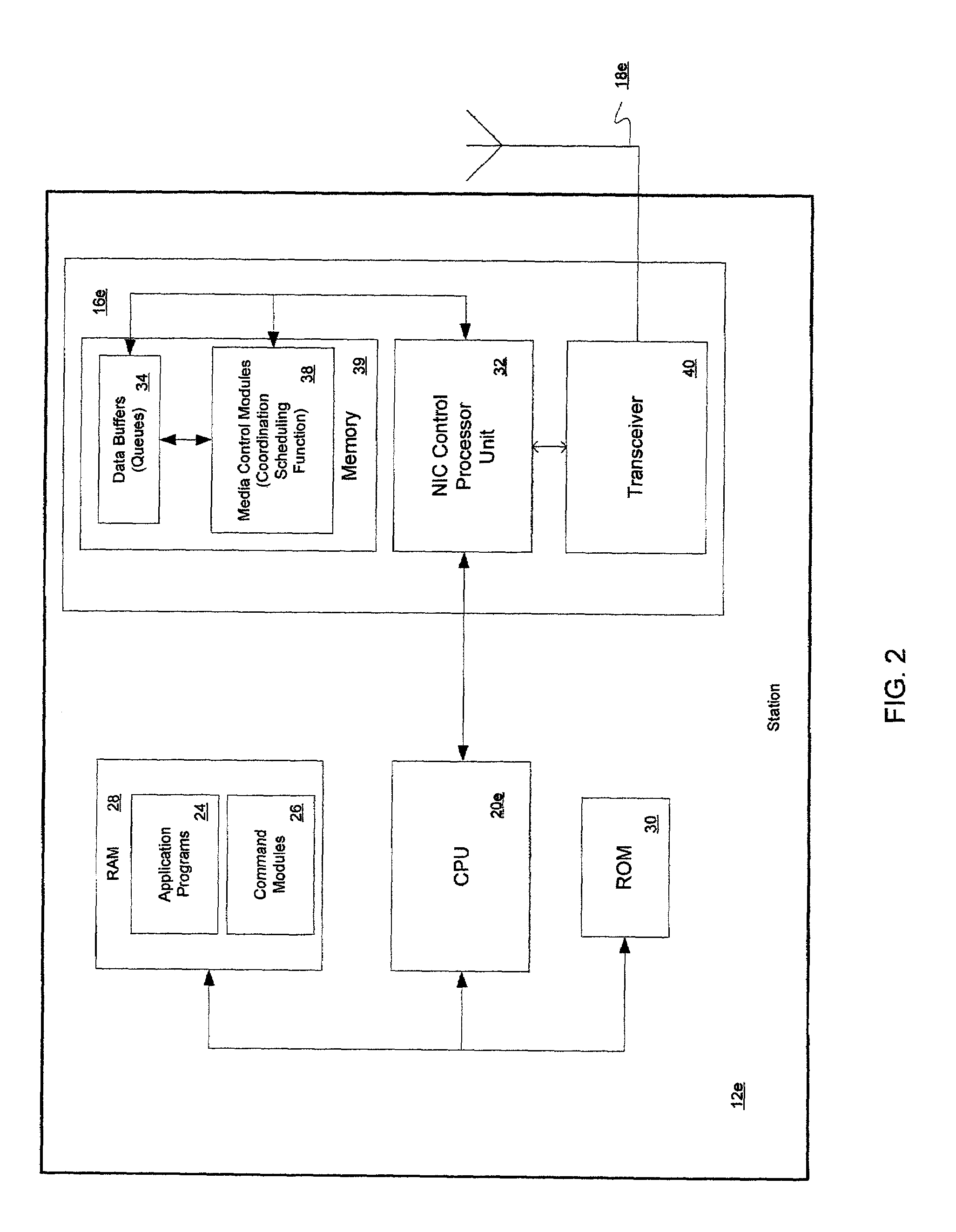

System and method for ordering data messages having differing levels of priority for transmission over a shared communication channel

ActiveUS7136392B2Improve transfer rateSignificant delayNetwork traffic/resource managementData switching by path configurationDistributed computingTransmission opportunity

Stations of a communication network have internal queues for accumulating and transmitting data messages over a shared communication channel. Each queue within a station accumulates and transmits data messages that have a different level of priority than those accumulated and transmitted by other internal queues of that station. While preferential access to the shared channel is given to data messages having higher levels of priority, data messages having the same priority are transmitted according to a set of rules common to all of the stations. That is, a queue in one of the stations is configured to delay and / or transmit data messages of a given priority level according to a set of rules that applies identically to the queue of any other station that handles data messages of that same priority level. Transmission opportunities are thus fairly allocated between all queues containing data messages of the same priority level.

Owner:INTELLECTUAL VENTURES I LLC

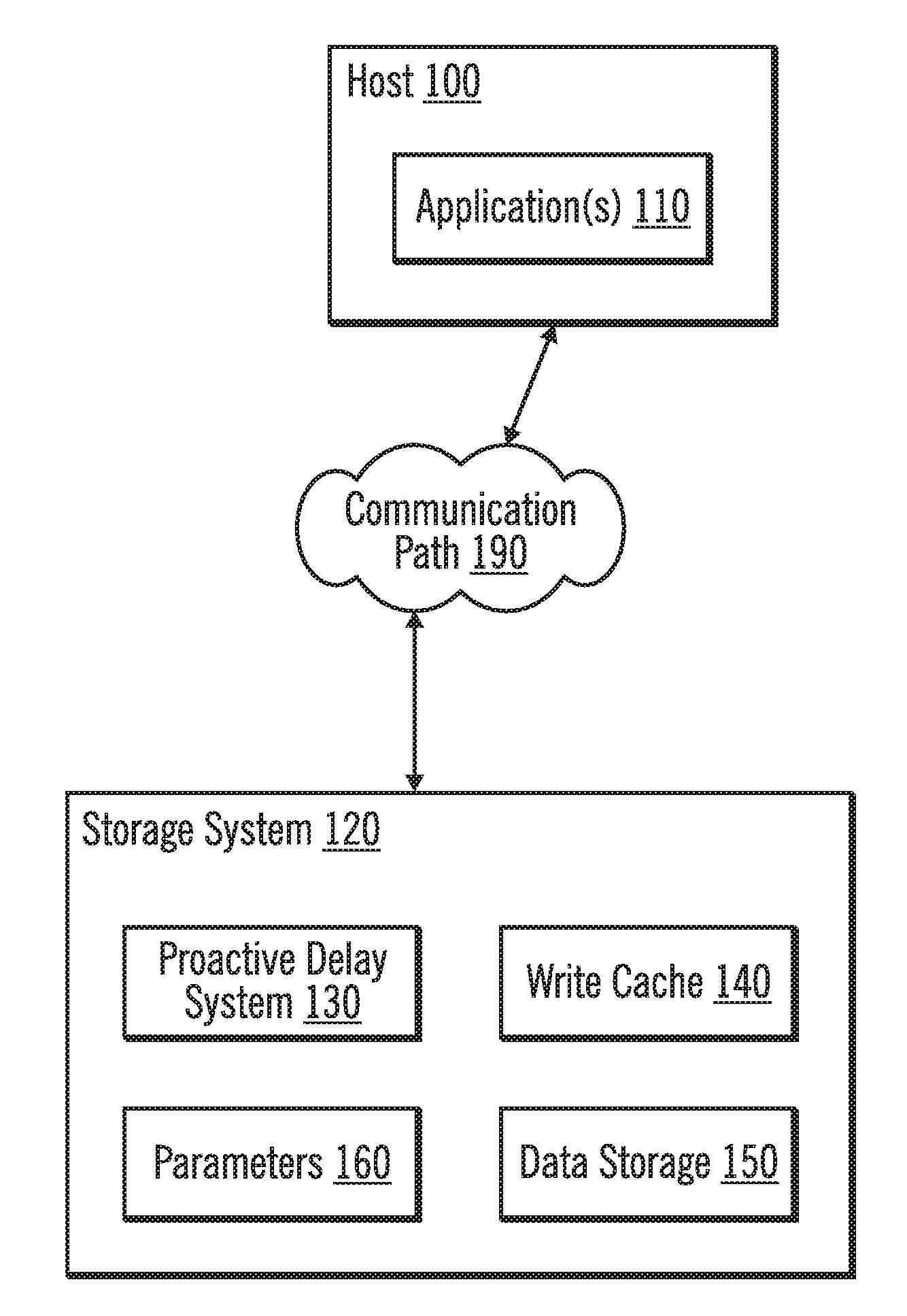

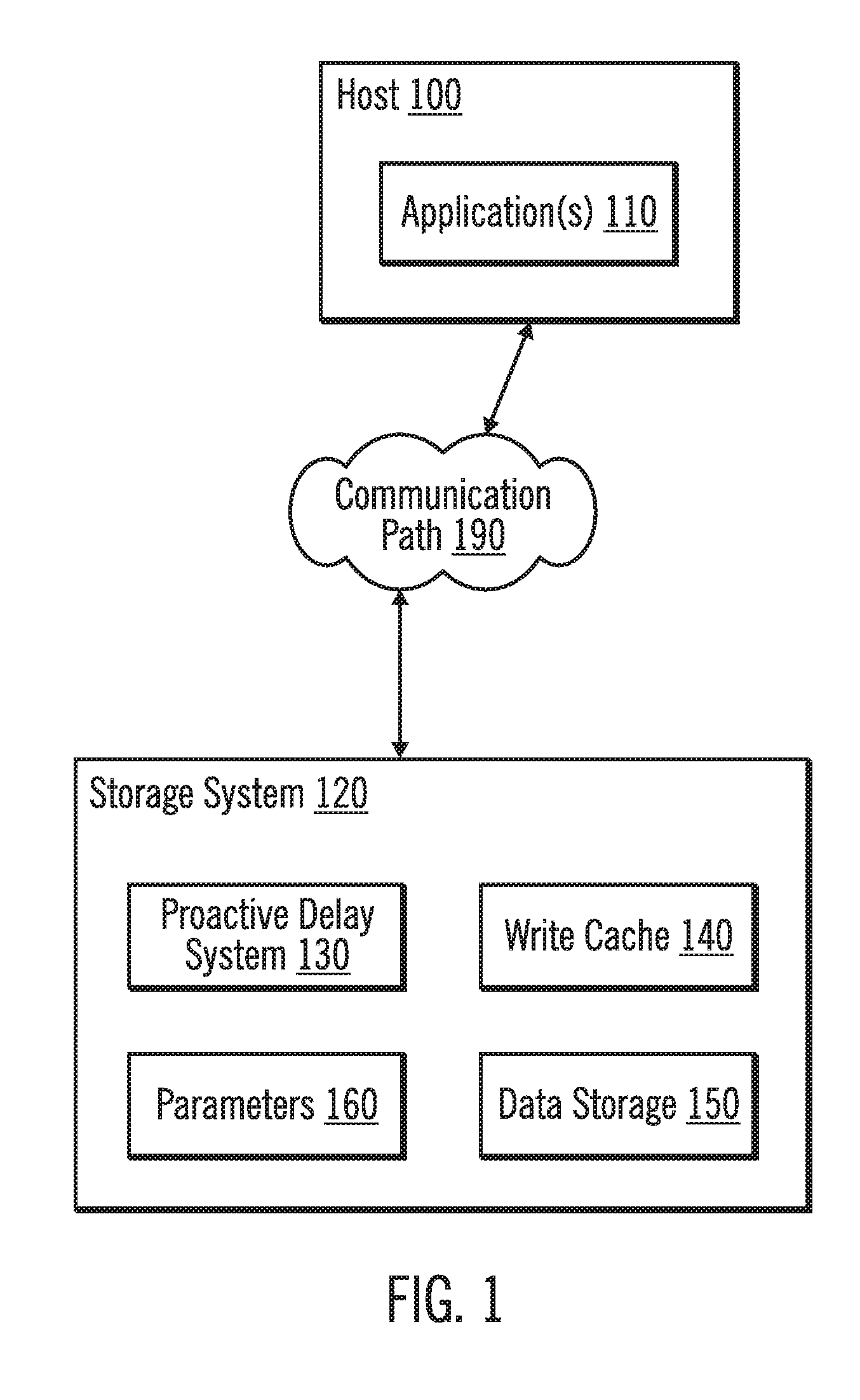

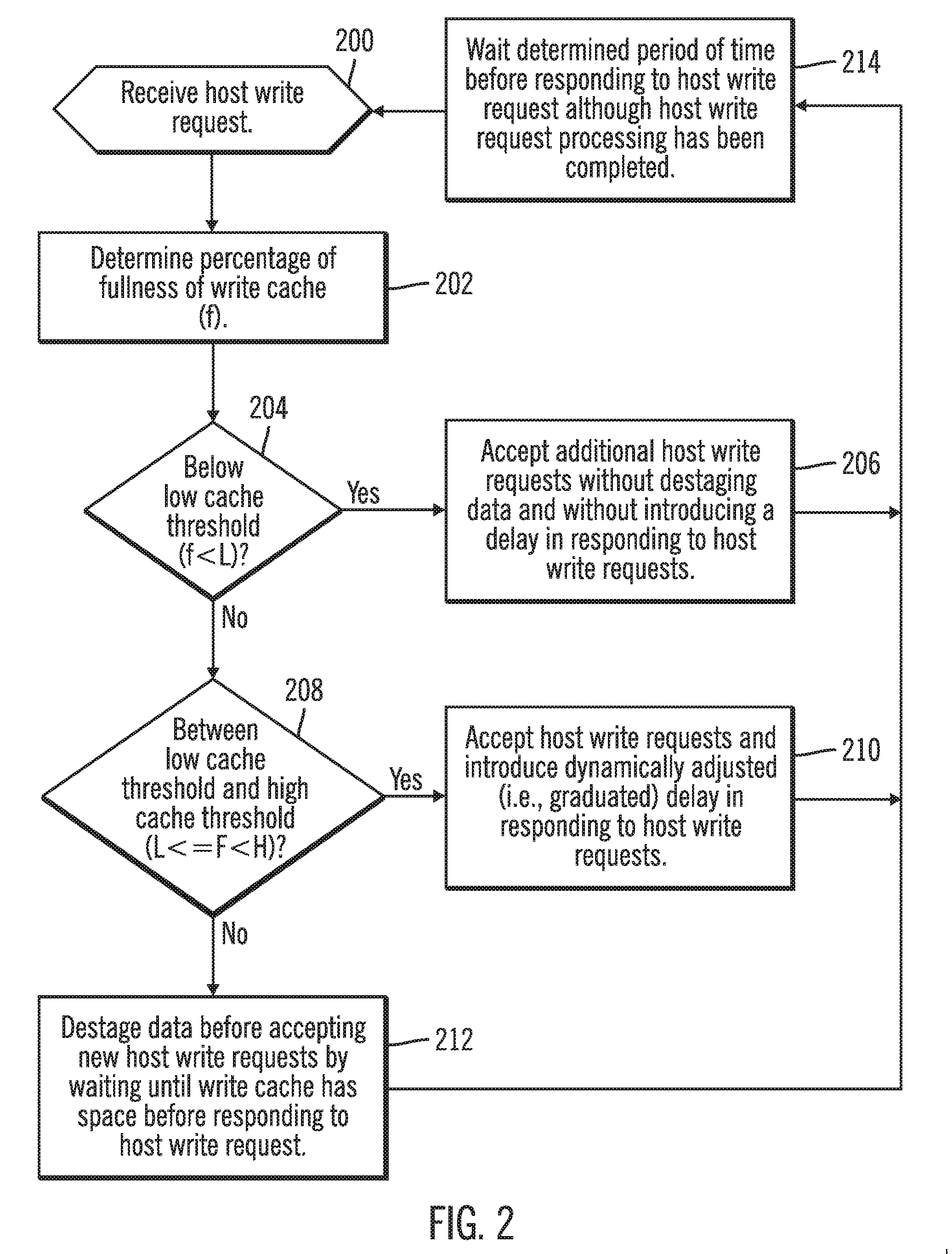

Proactive technique for reducing occurrence of long write service time for a storage device with a write cache

InactiveUS20100199050A1Significant delayMinimizes probabilityMemory architecture accessing/allocationMemory adressing/allocation/relocationGreek letter alphaService time

Provided are techniques for introducing a delay in responding to host write requests. A percentage of fullness of a write cache is determined. Based on the determined percentage of fullness of the write cache (f), a low cache threshold (L), alpha (α), and k, an amount of delay to introduce into responding to a host write request is determined. Techniques wait the amount of the delay before responding to the host write request although the host write request processing has completed.

Owner:IBM CORP

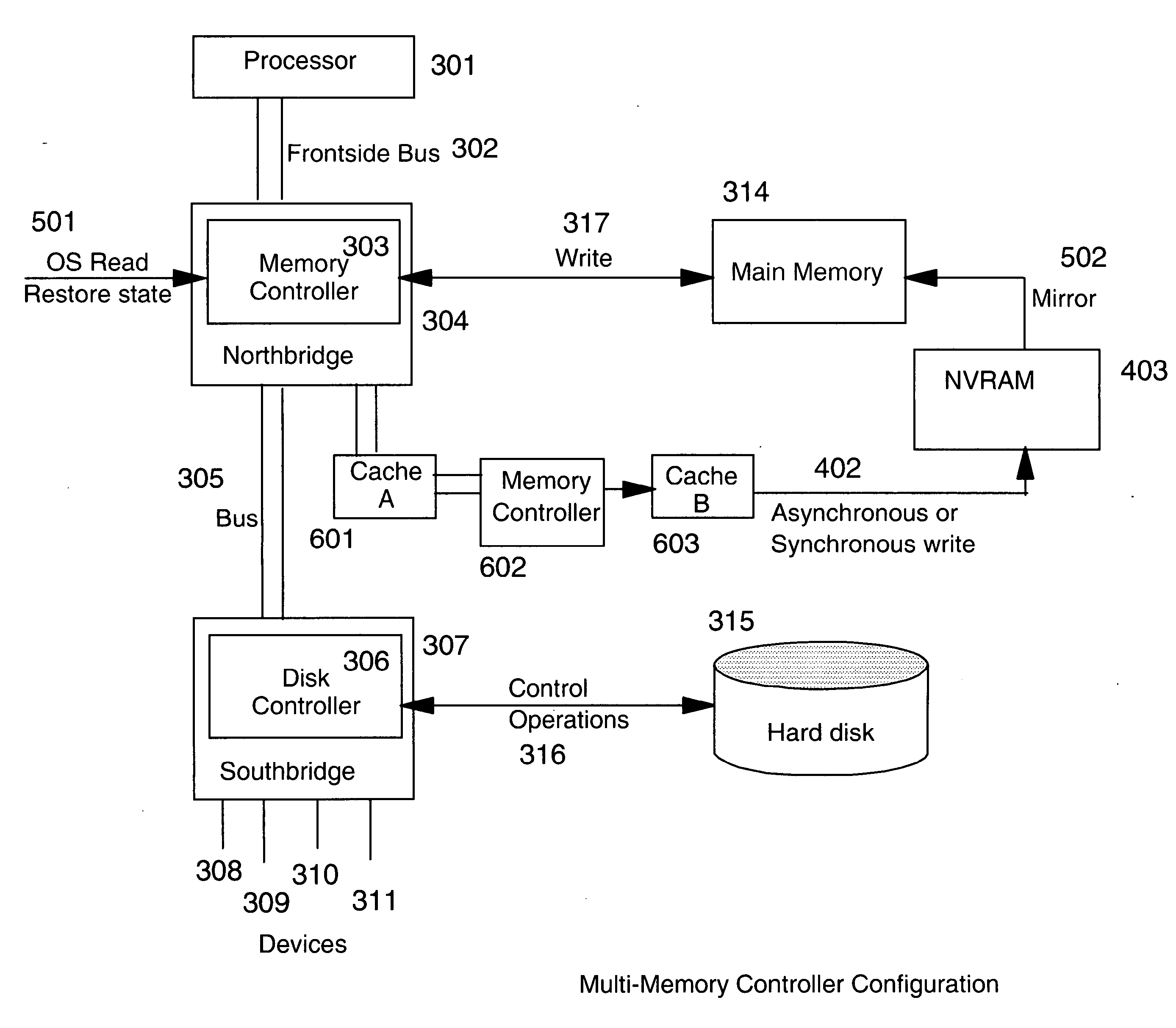

Mirroring System Memory In Non-Volatile Random Access Memory (NVRAM) For Fast Power On/Off Cycling

InactiveUS20080256316A1Average power consumptionSignificant delayMemory architecture accessing/allocationEnergy efficient ICTRandom access memoryTerm memory

A computer comprising a processor, a volatile main store, a non-volatile random access memory (NVRAM) mirror store, and optionally a cache for the non-volatile mirror store. While programs of the computer are operational, the contents of the volatile main store are mirrored in the non-volatile mirror store such that when a startup signal is received, the contents of the volatile main store are quickly restored from the contents of the non-volatile mirror store.

Owner:IBM CORP

Rapid identification of bacteria from positive blood cultures

InactiveUS7205111B2Increase profitFast approachMicrobiological testing/measurementBiological testingBacteroidesRapid identification

Disclosed is a method of detecting bacteria in a biological sample, especially a blood sample, without the need for extensive sub-culturing of the sample. Nucleic acid present within the sample is isolated and bacterial DNA specifically amplified using primers that uniquely prime the amplification of 16s rRNA-encoding nucleic acid. The amplicons are then digested with an endonuclease to yield a restriction fragment length profile for the biological sample. The restriction fragment length profile for the biological sample is then compare to a database of profiles made using cultures of known bacterial species. A match between the sample profile and the database identifies the bacteria present in the sample.

Owner:MARSHFIELD CLINIC

Optimizing integrated circuit design through use of sequential timing information

InactiveUS20080276210A1Increase flexibilityEasy to implementCAD circuit designSoftware simulation/interpretation/emulationProcessor registerCircuit design

A method is provided that includes: determining a minimum clock cycle that can be used to propagate a signal about the critical cycle in a circuit design; wherein the critical cycle is a cycle in the design that has a highest proportionality of delay to number of registers; determining for a circuit element in the circuit design, sequential slack associated with the circuit element; wherein the sequential slack represents a minimum delay from among respective maximum delays that can be added to respective structural cycles of which the circuit element is a constituent, based upon the determined limit upon clock cycle duration; using the sequential slack to ascertain sequential optimization based design flexibility throughout multiple stages of a design flow.

Owner:CADENCE DESIGN SYST INC

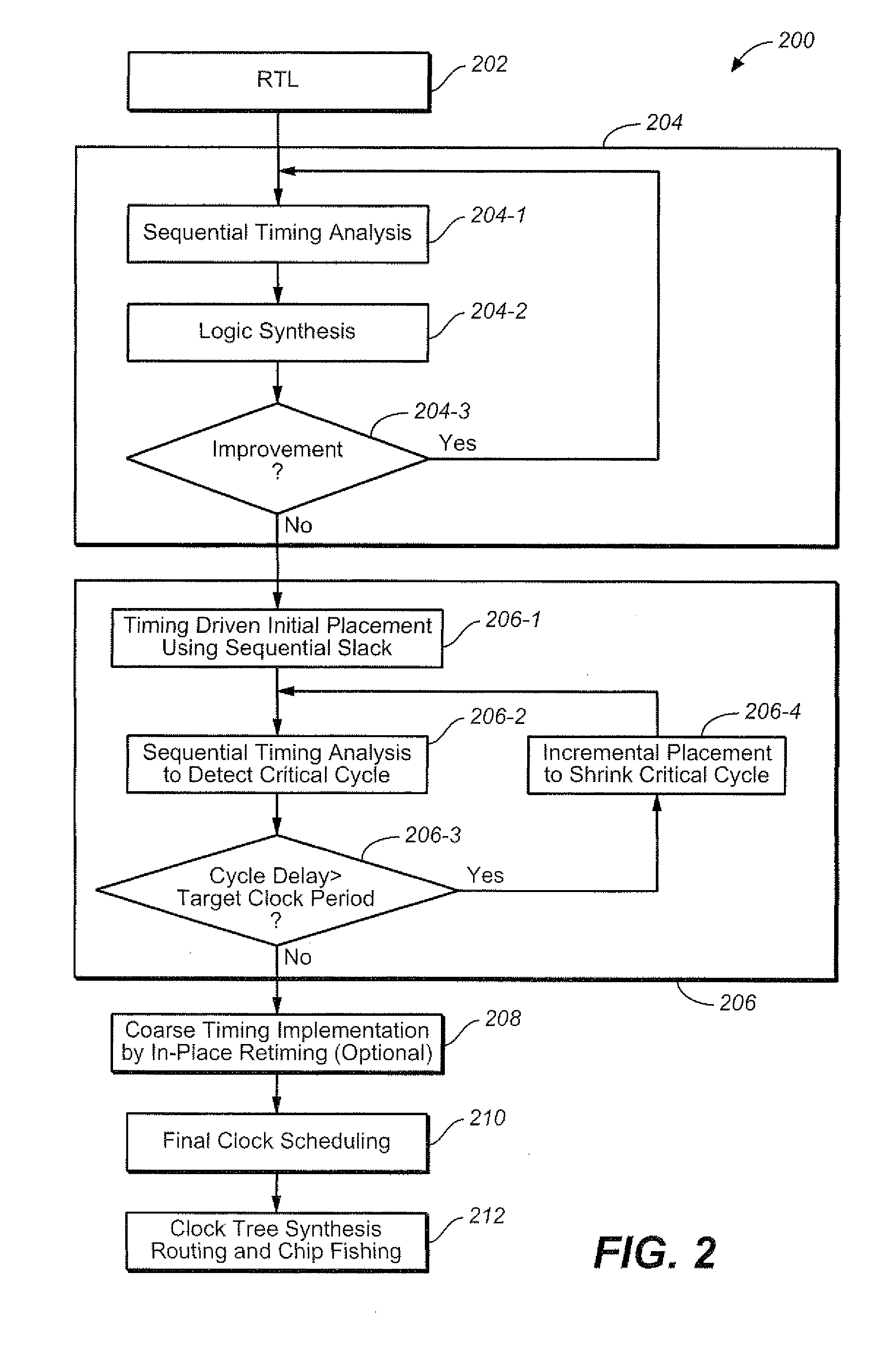

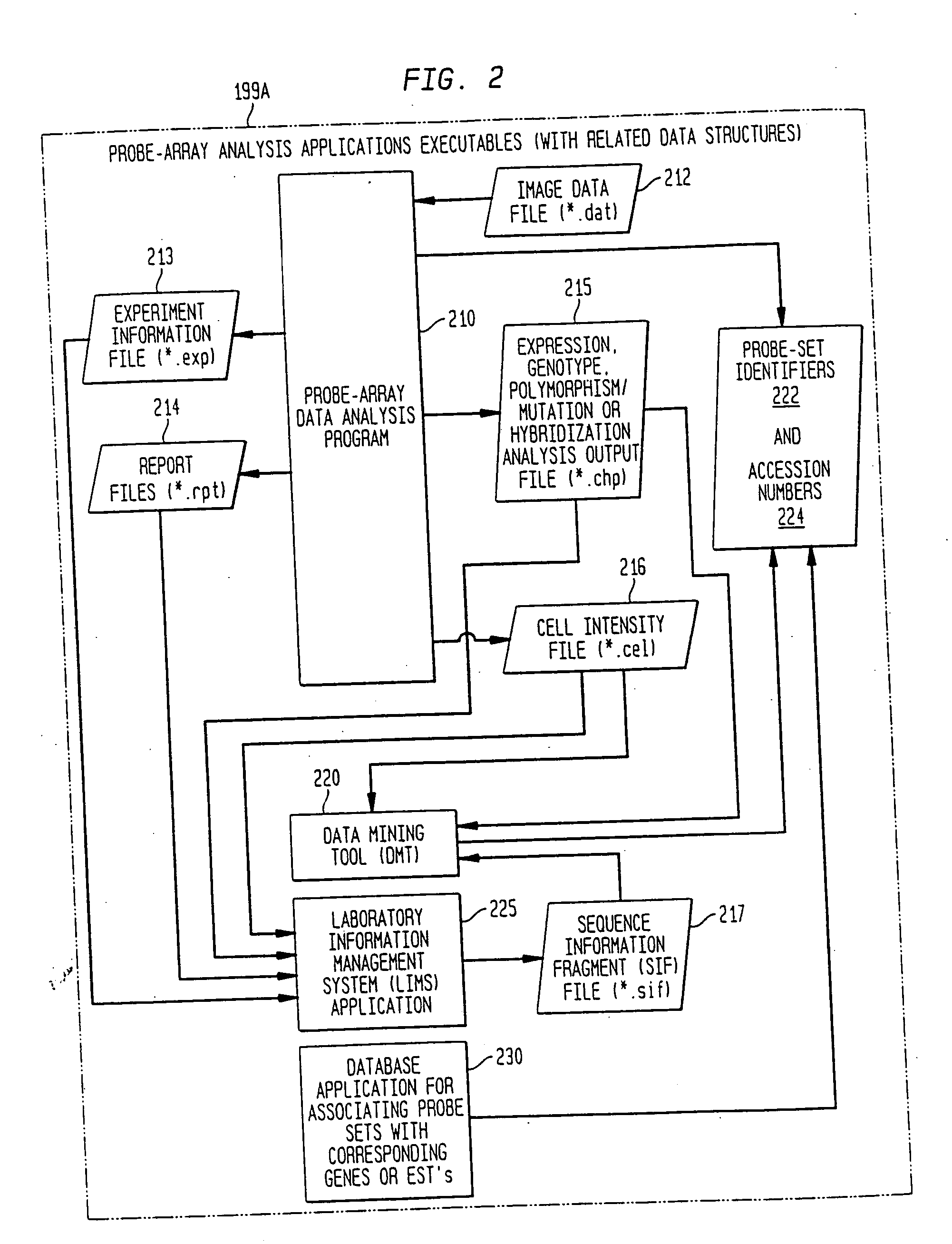

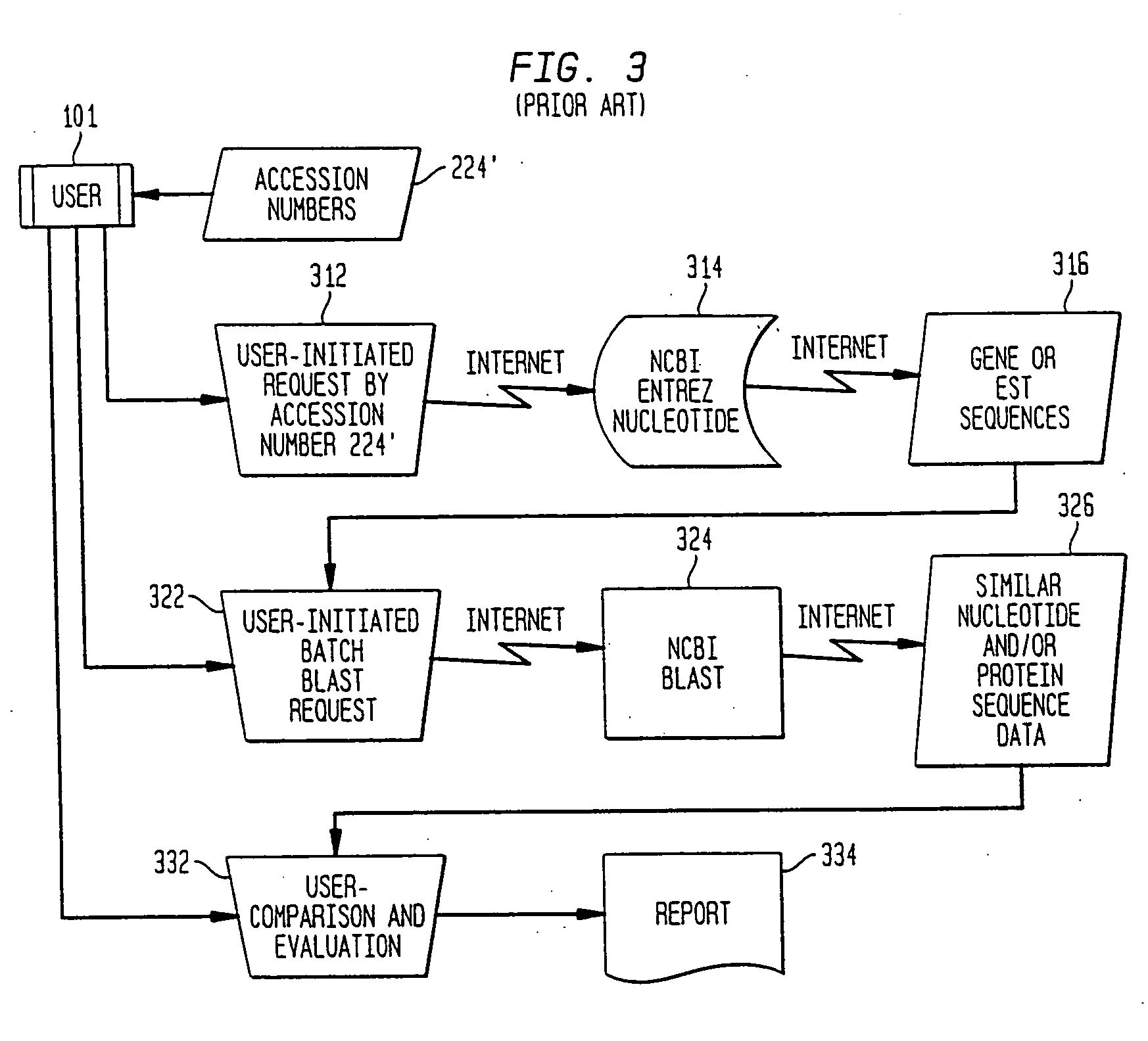

Method, system, and computer software for providing a genomic web portal

InactiveUS20050009078A1Significant delayMicrobiological testing/measurementBiological testingGenomic databasesComputer software

Systems, methods, and computer program products are described that process inquiries or orders regarding purchase of biological devices, substances, or related reagents. In some implementations, a user selects probe-set identifiers that identify microarray probe sets capable of enabling detection of biological molecules. Corresponding genes or EST's are identified and are correlated with related product data, which is provided to the user. Further, the user may select products for purchase based on the product data. If so, the user's account may be adjusted based on the purchase order. In the same or other implementations, a local genomic database is periodically updated. In response to a user selection of probe-set identifiers, data related to corresponding genes or EST's is provided to the user from the local genomic database.

Owner:AFFYMETRIX INC

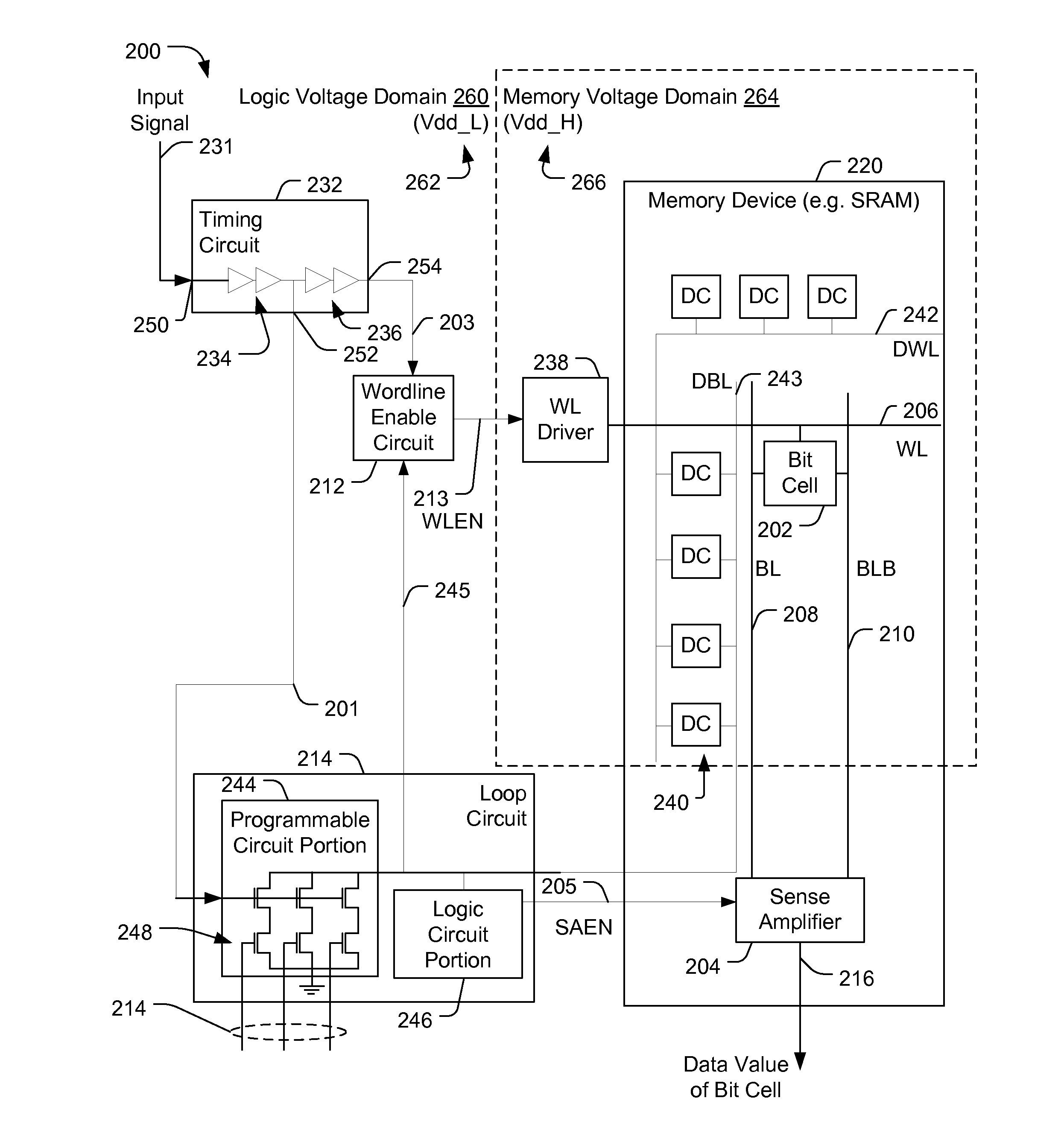

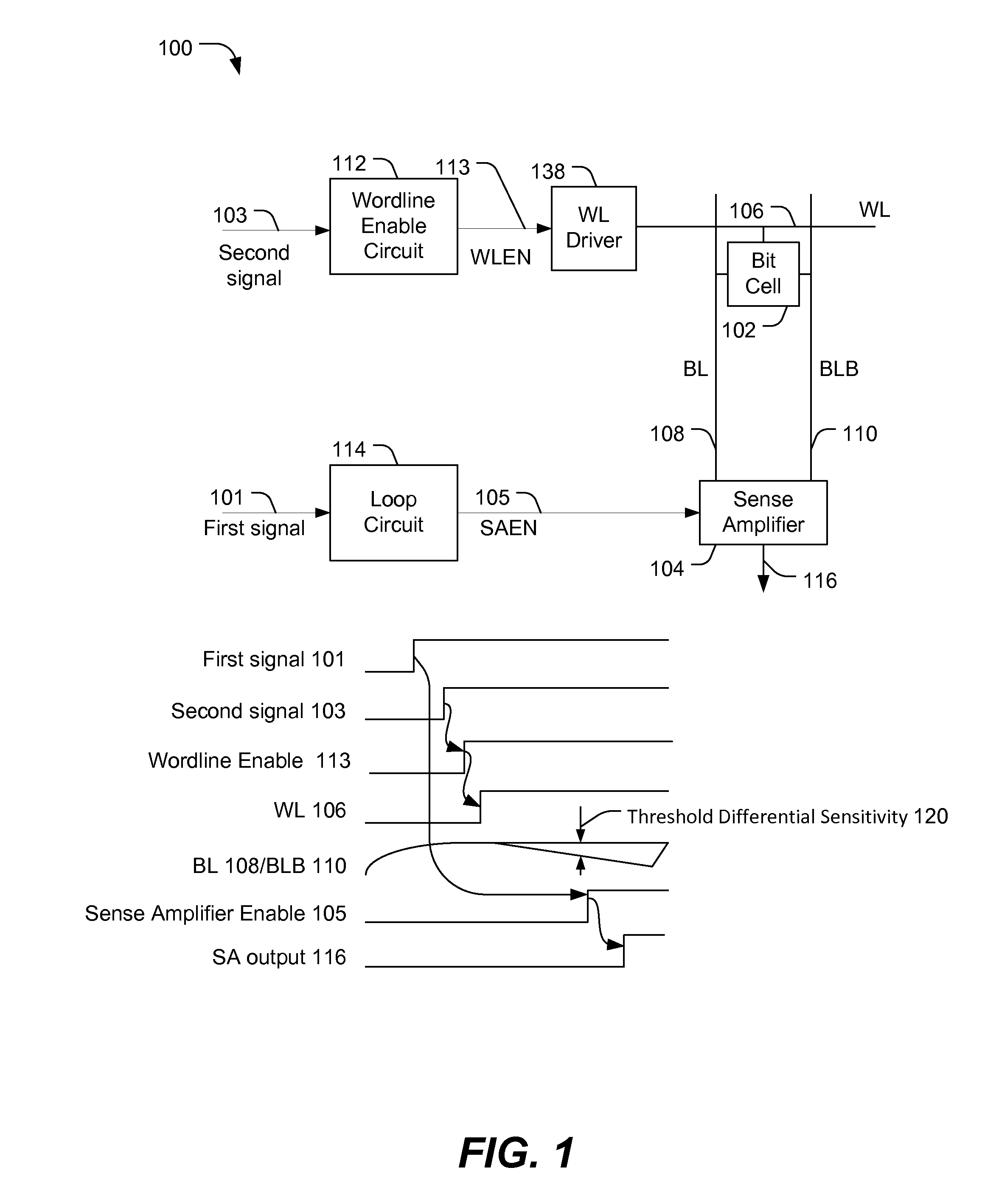

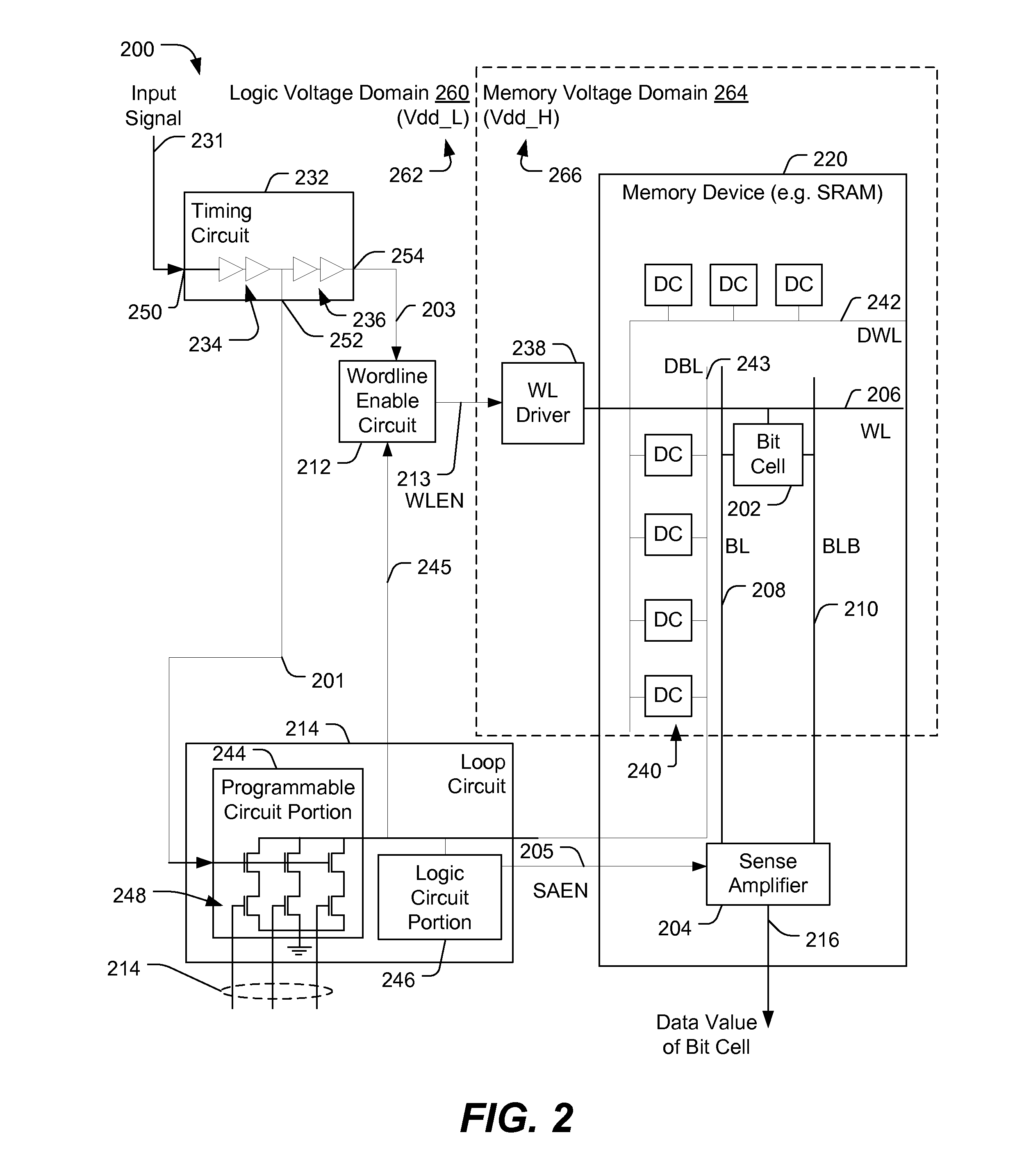

System and Method of Operating a Memory Device

A system and method of operating a memory device is disclosed. In a particular embodiment, an apparatus is disclosed that includes a bit cell coupled to a first bit line and to a second bit line. The apparatus also includes a sense amplifier coupled to the first bit line and to the second bit line. The apparatus includes a loop circuit configured to provide a sense amplifier enable signal to the sense amplifier in response to receiving a first signal. The apparatus also includes a wordline enable circuit configured to provide a wordline enable signal to a wordline driver in response to receiving a second signal. The loop circuit receives the first signal before the wordline enable circuit receives the second signal.

Owner:QUALCOMM INC

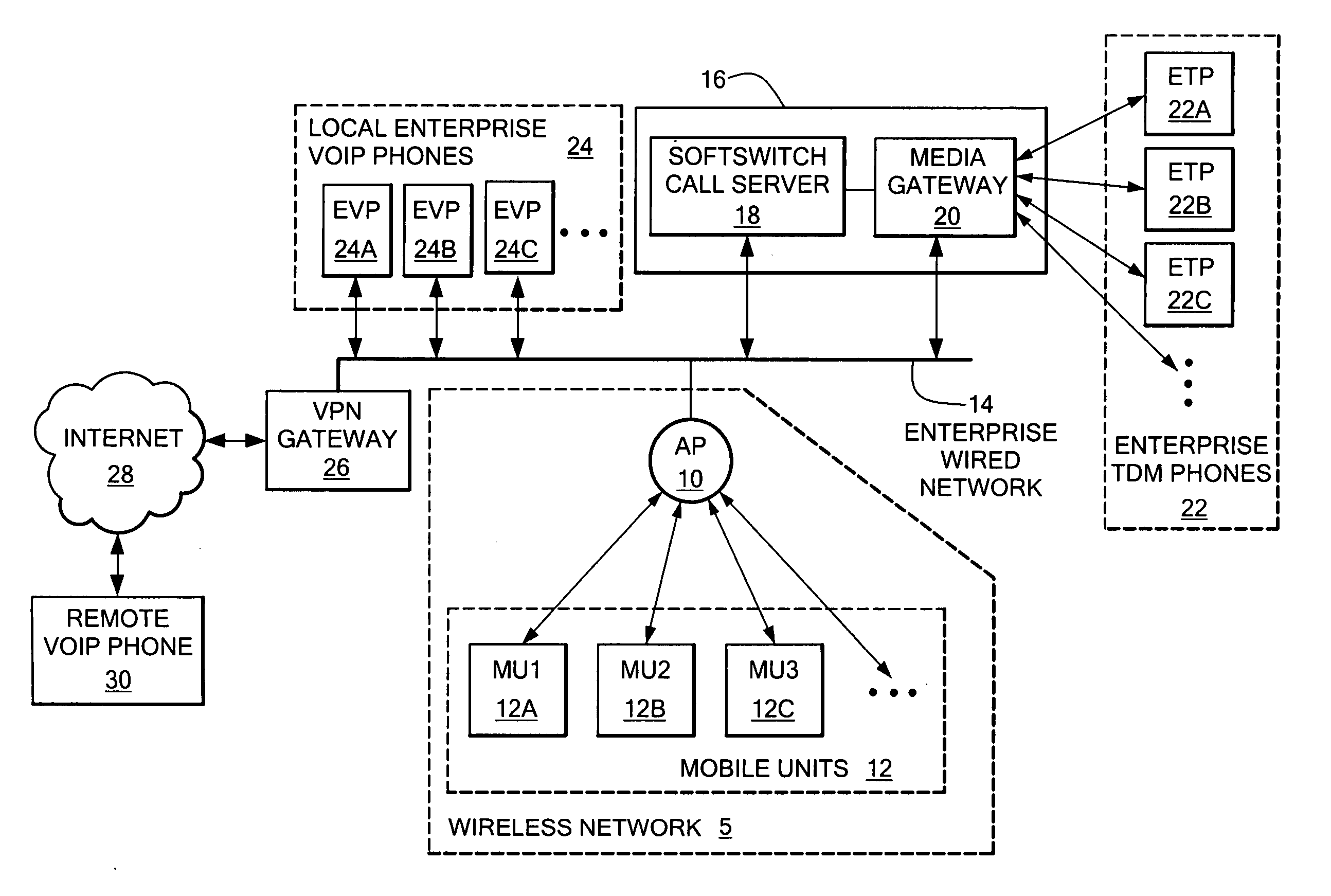

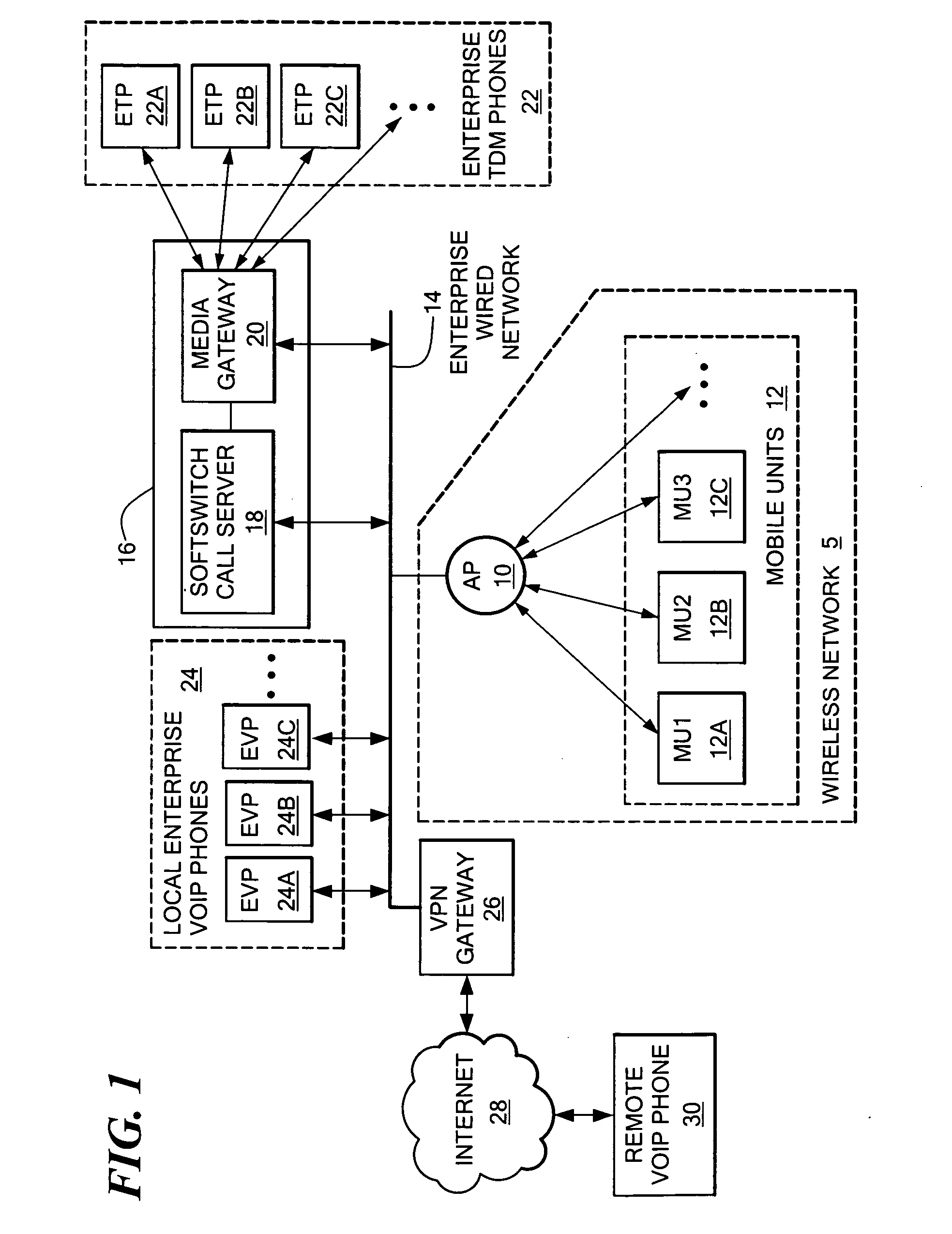

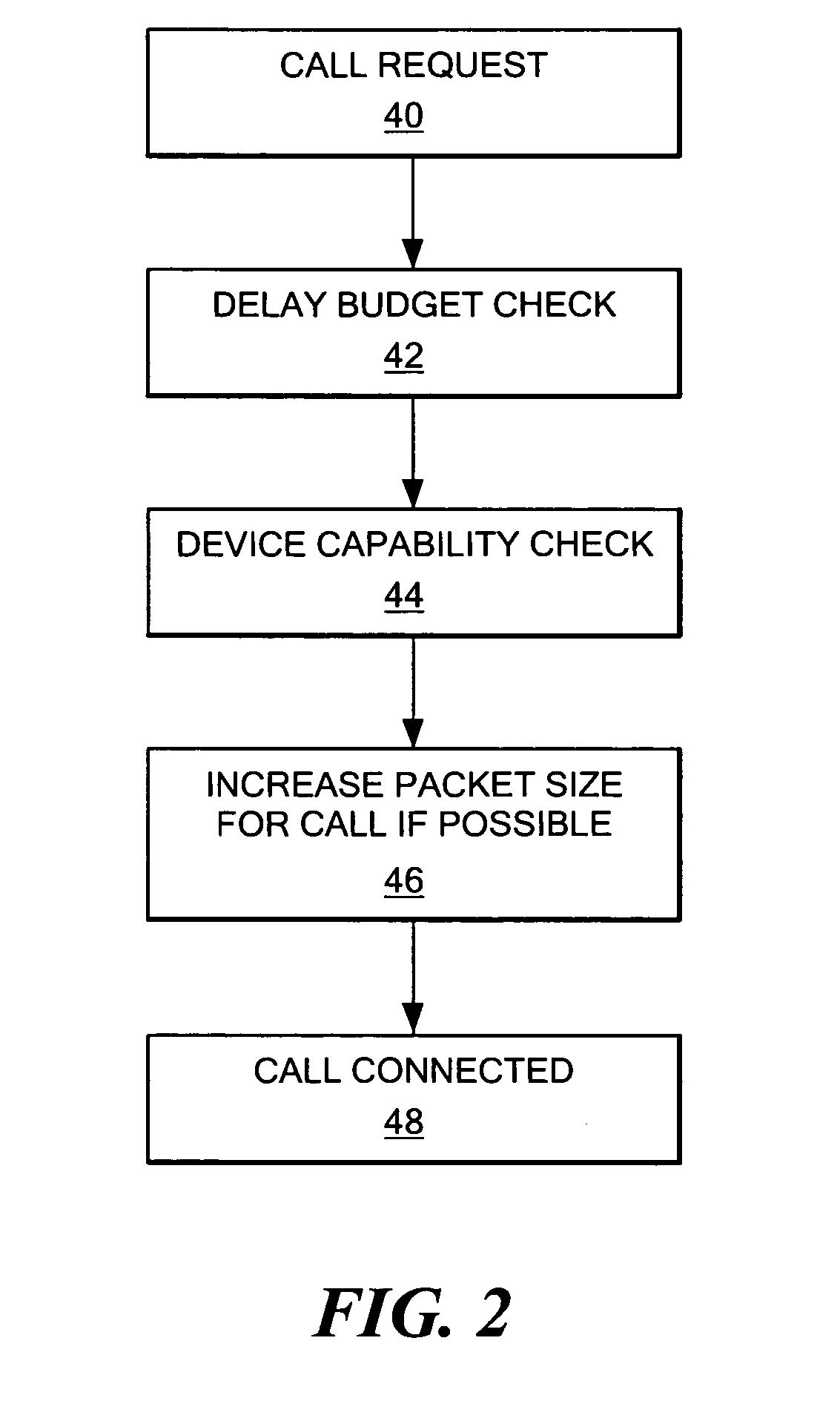

System and method for increasing call capacity for a wireless local area network

InactiveUS20050226219A1Increase access capacityIncrease delayInterconnection arrangementsNetwork traffic/resource managementTotal delayMaximum latency

A system for increasing the call capacity of an access point in a WLAN, allowing the number of WLAN phones that can be supported to be increased. The system determines whether a maximum total voice path delay would be exceeded if the packetization delay is increased for packets in a call. In the event that the packetization delay can be increased without the total delay exceeding the maximum delay, the disclosed system increases the size of packets used in the call, if all participating devices can process the increased packet size. The maximum delay may be predetermined, and reflect a maximum delay that cannot be exceeded without adversely impacting the voice quality of a call. If the two end points for a call are determined to be physically “local” to each other, packetization delay for the call may be increased based on the assumption that the increased packetization delay will not decrease the voice quality of the call.

Owner:AVAYA INC

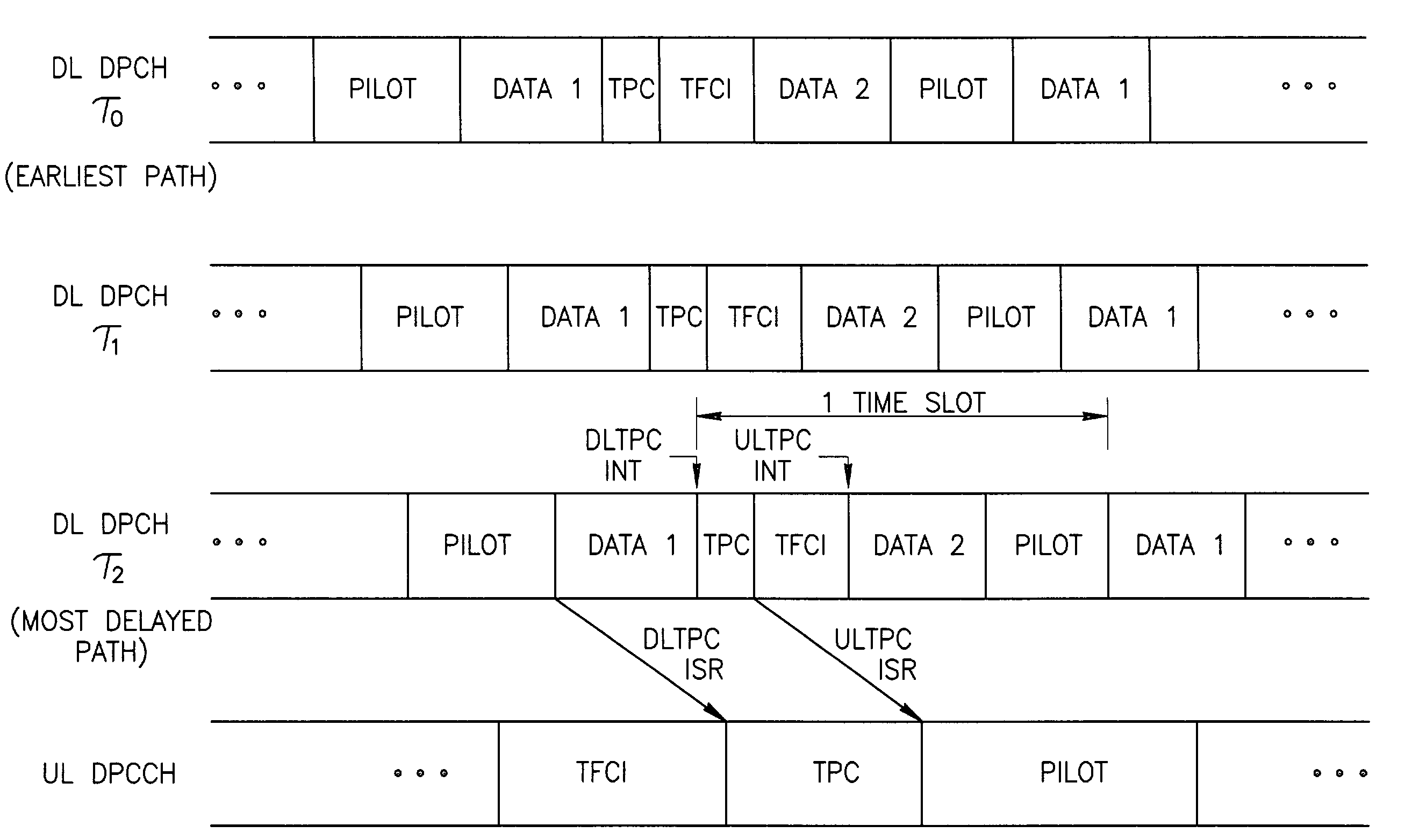

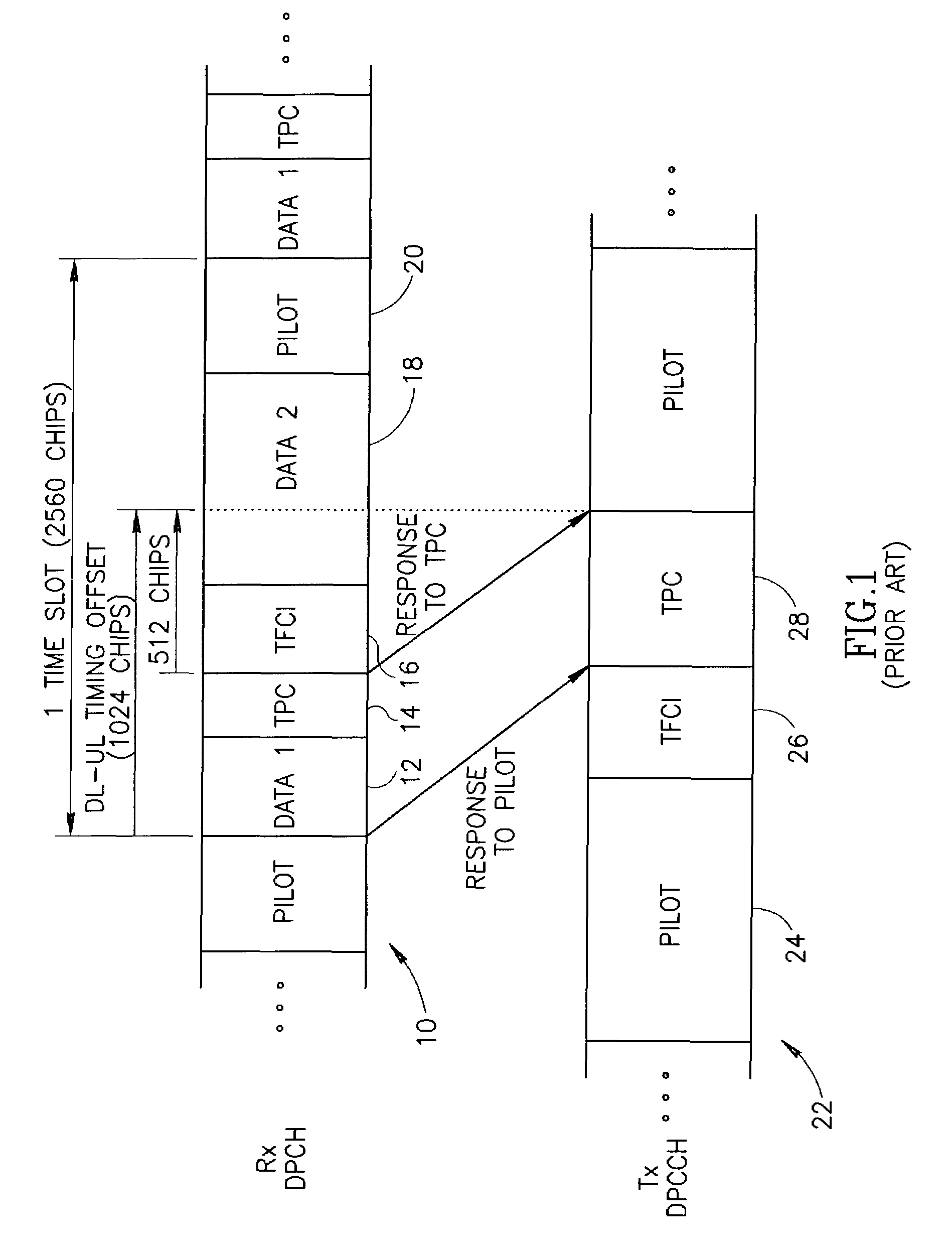

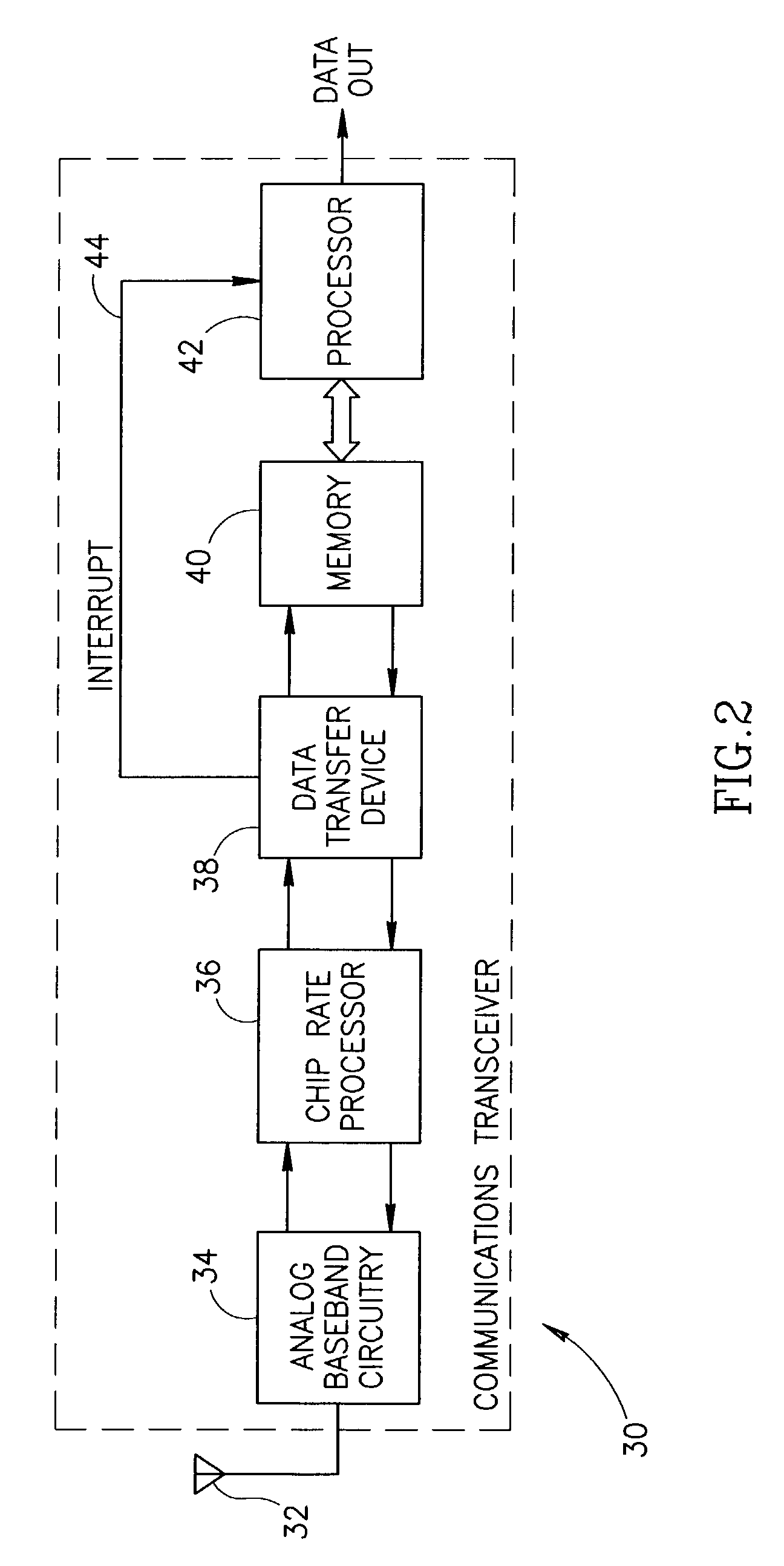

Information transfer and interrupt event scheduling scheme for a communications transceiver incorporating multiple processing elements

InactiveUS7307977B1Significant delayFast and efficient configurationPower managementCode division multiplexTransceiverProcessing element

A real-time optimizing information transfer and interrupt event scheduling scheme for a communications transceiver incorporating multiple processing elements. The scheme is particularly applicable for use in UMTS based communications transceivers, i.e. W-CDMA transceivers adapted for User Equipment (UE). The interrupt scheduling scheme of the present invention is operative to perform the scheduling of interrupts used to configure a data transfer device to effect the timely transfer of data from a hardware based chip rate processor to a memory buffer for subsequent processing by software running on a DSP or other processor platform.

Owner:COMSYS COMM & SIGNAL PROC