Structure and fabrication of self-aligned high-performance organic fets

a technology of organic transistors and structures, applied in the field of organic transistors, can solve the problems of significantly different actual mechanics giving rise to charge carriers in organic semiconductors, significantly different organic transistors, and significantly different inorganic transistors, and achieve the effects of low cost, low channel length devices, and high volum

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

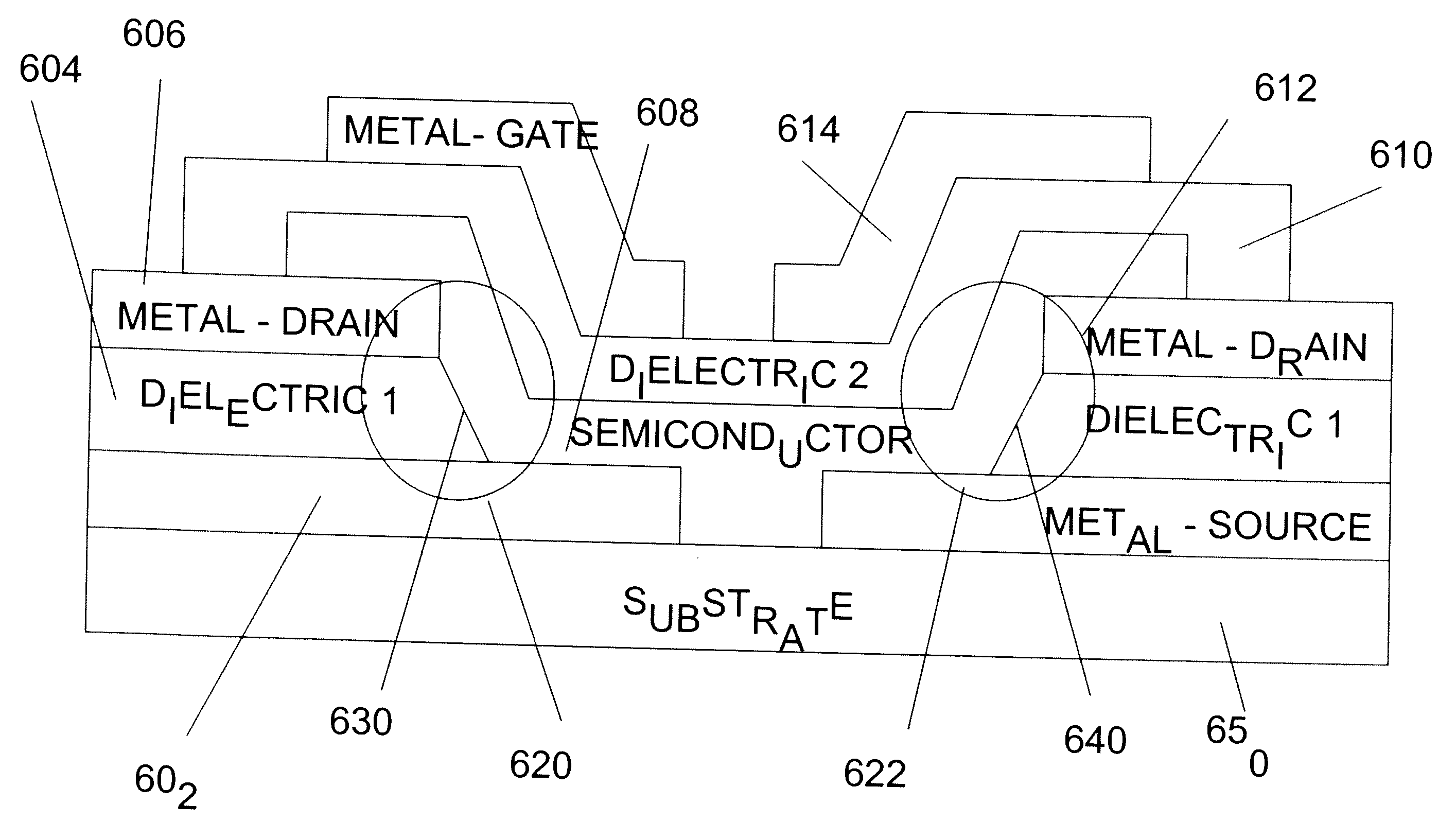

[0025] Referring now to FIG. 5, one embodiment of this invention is illustrated. The structure is formed by depositing successive patterned layers of a conductor metal—source 502, a first insulator dielectric 504, a conductor metal-drain 506, a semiconductor 508, a second insulator dielectric 510, a conductor metal-drain 512 and a conductor metal-gate 514 on substrate 550.

[0026] Referring to FIG. 5, region 520 signifies a transistor formed by this structure. The source of this device is formed by metal source 502, and the drain is formed by metal-drain 506. The vertical space between metal-drain 506 and metal-source 502 forms the channel region 530 of the device in region 520. The channel region 530 is overlapped by successive layers of a semiconductor 508, dielectric 2510, and metal gate 514. The gate terminal of the transistor in region 520 is metal-gate 514.

[0027] Referring to FIG. 5, region 522 signifies a second transistor formed by the same structure. The gap 540 is the chan...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thicknesses | aaaaa | aaaaa |

| dielectric thickness | aaaaa | aaaaa |

| thick | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More