Semiconductor device and method of forming the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

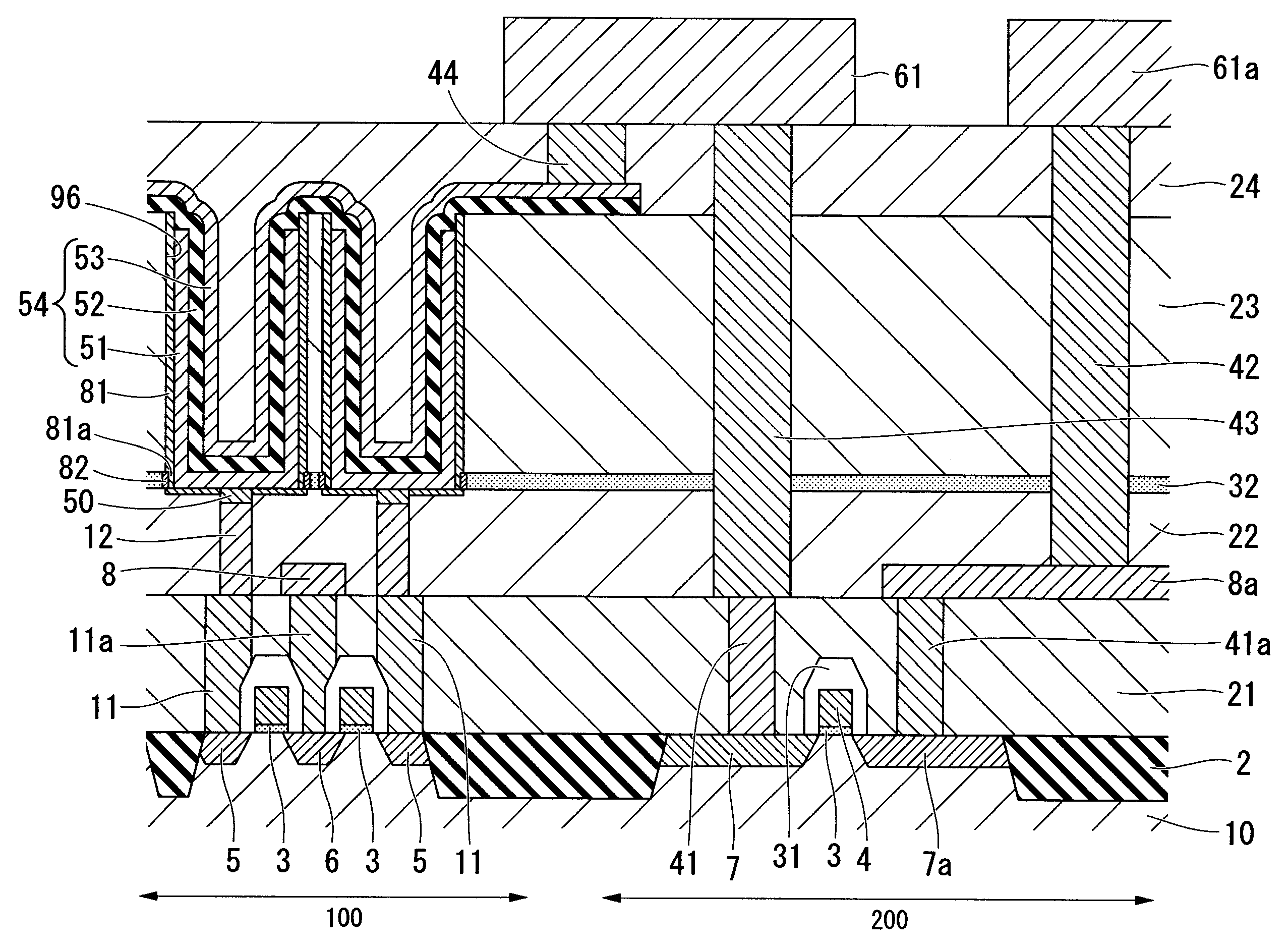

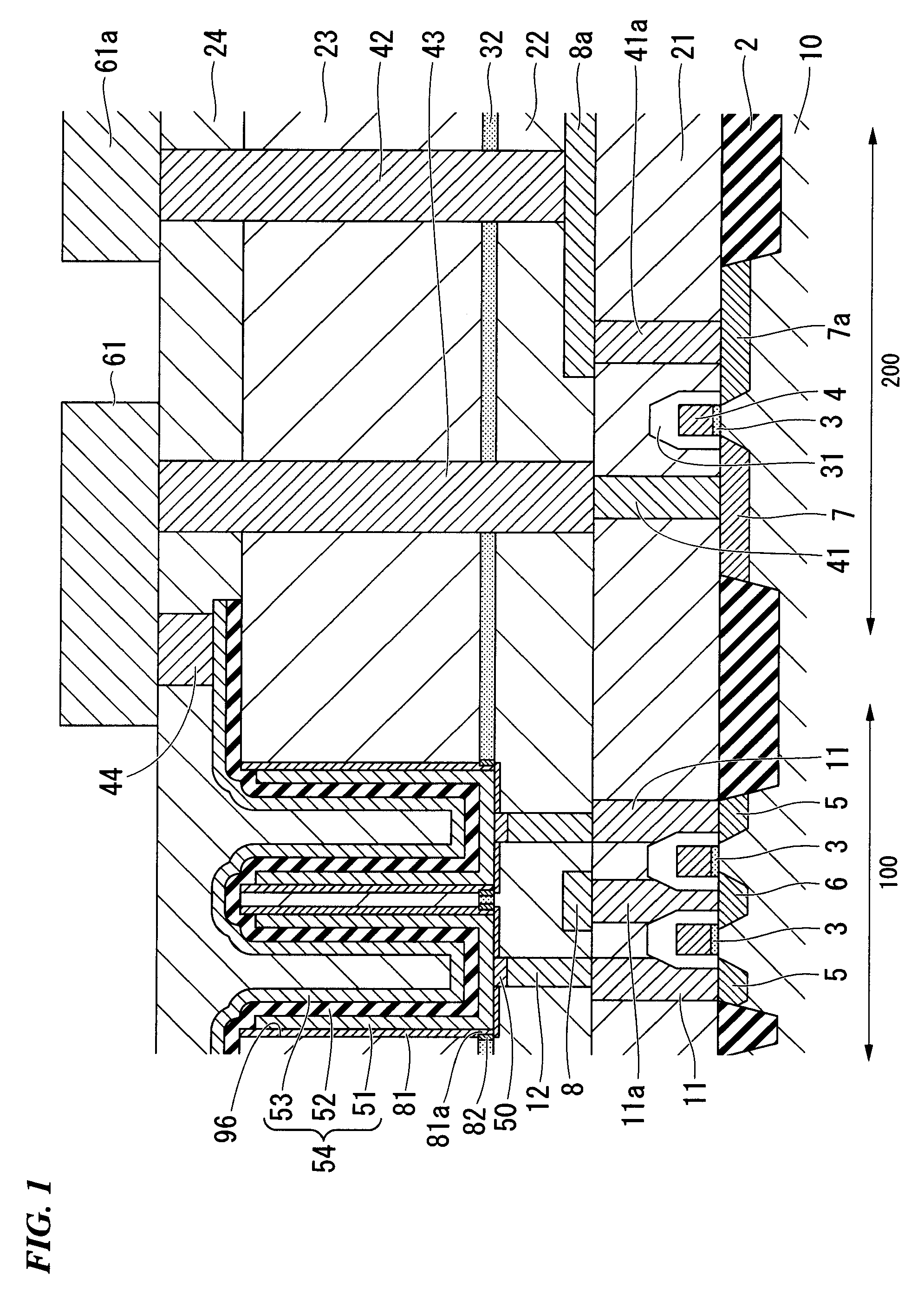

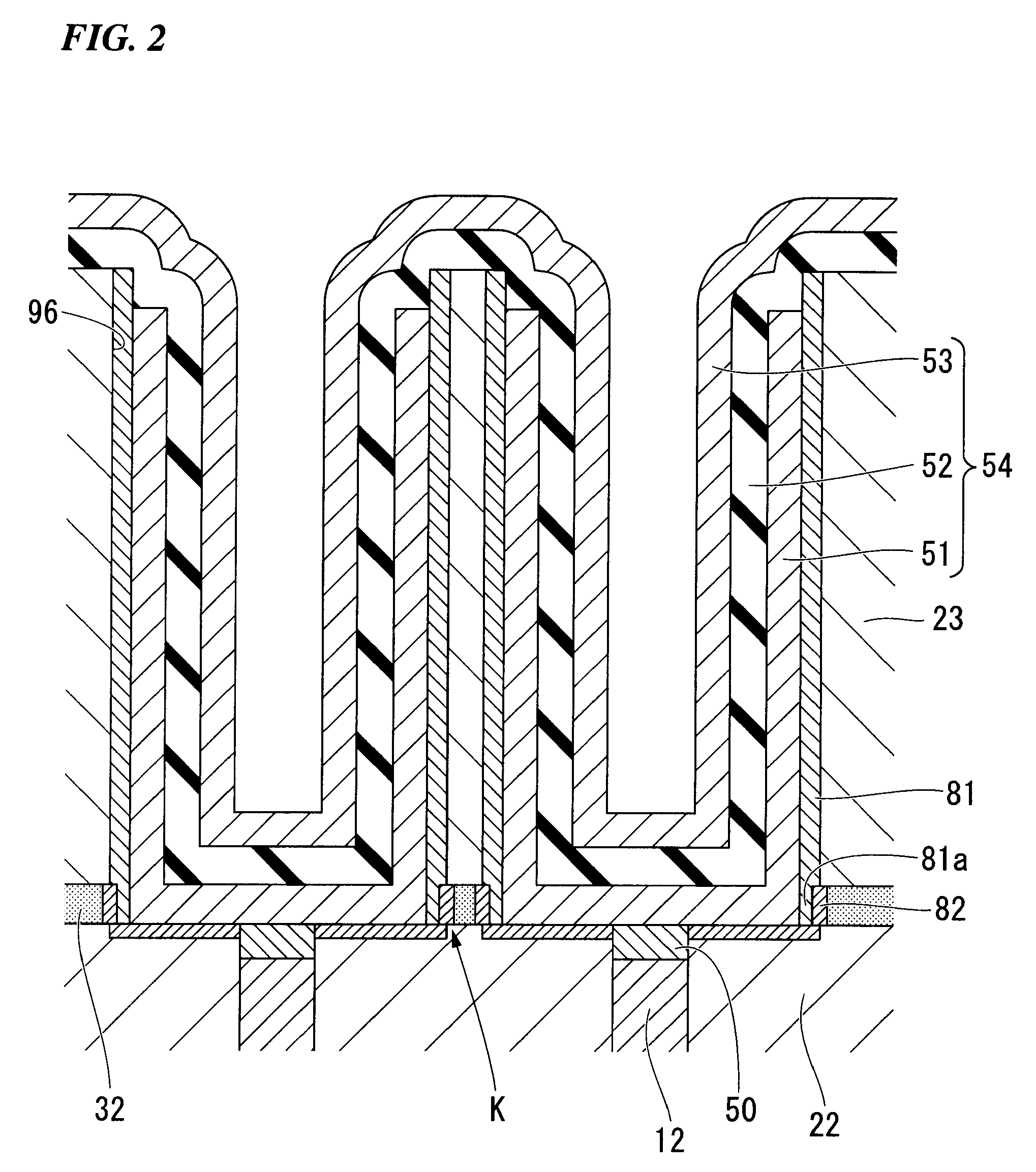

[0094]The first embodiment provides a semiconductor memory device including a metal-insulator-metal capacitor and a method of forming the same. The descriptions of the first embodiment will be made with reference to FIGS. 1-16.

(1) Semiconductor Memory Device and Capacitor Structure:

[0095]FIG. 1 is a fragmentary cross sectional elevation view illustrating a semiconductor memory device in accordance with a first preferred embodiment of the present invention. The semiconductor memory device includes a memory cell area 100 and a peripheral circuit area 200, which are adjacent to each other. The memory cell area 100 has a memory cell. The peripheral circuit area 200 has a peripheral circuit. The semiconductor memory device has a silicon substrate 10 that has a main face. An isolating film 2 such as a local oxidation of silicon film is disposed on the main face of the silicon substrate 10.

[0096]In the memory cell area 100, the isolation film 2 defines a first active region of the silicon ...

second embodiment

[0159]The second embodiment provides a semiconductor memory device including a metal-insulator-metal capacitor and a method of forming the same. The descriptions of the second embodiment will be made with reference to FIGS. 17-22.

(1) Semiconductor Memory Device and Capacitor Structure:

[0160]FIG. 17 is a fragmentary cross sectional elevation view illustrating a semiconductor memory device in accordance with a second preferred embodiment of the present invention. FIG. 18 is a fragmentary enlarged cross sectional view illustrating a capacitor structure included in a memory cell in the semiconductor device of FIG. 17.

[0161]Similarly to the first embodiment, the semiconductor memory device of the second embodiment includes the memory cell area 100 and the peripheral circuit area 200, which are adjacent to each other. The memory cell area 100 has the memory cell which includes the memory cell transistors and the capacitor 54. The peripheral circuit area 200 has the peripheral circuit.

[016...

third embodiment

[0188]The third embodiment provides a semiconductor memory device including a metal-insulator-metal capacitor including a pedestal bottom electrode and a method of forming the same. The descriptions of the third embodiment will be made with reference to FIGS. 23-29.

(1) Semiconductor Memory Device and Capacitor Structure:

[0189]FIG. 23 is a fragmentary cross sectional elevation view illustrating a semiconductor memory device in accordance with a third preferred embodiment of the present invention. FIG. 24 is a fragmentary enlarged cross sectional view illustrating a capacitor structure with a pedestal bottom electrode which is included in a memory cell in the semiconductor device of FIG. 23.

[0190]Similarly to the first embodiment, the semiconductor memory device of the second embodiment includes the memory cell area 100 and the peripheral circuit area 200, which are adjacent to each other. The memory cell area 100 has the memory cell which includes the memory cell transistors and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com