SEMICONDUCTOR DEVICE HAVING PARTIALLY INSULATED FIELD EFFECT TRANSISTOR (PiFET) AND METHOD OF FABRICATING THE SAME

a semiconductor device and field effect technology, applied in semiconductor devices, single crystal growth, chemistry apparatus and processes, etc., can solve the problems of increasing the cost of increasing the floating body effect, short channel, increasing the leakage current, etc., to prevent both short channel effect and floating body effect, and to prevent short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026]The invention will be described more fully hereinafter with reference to the accompanying drawings, in which several exemplary embodiments of the invention are shown.

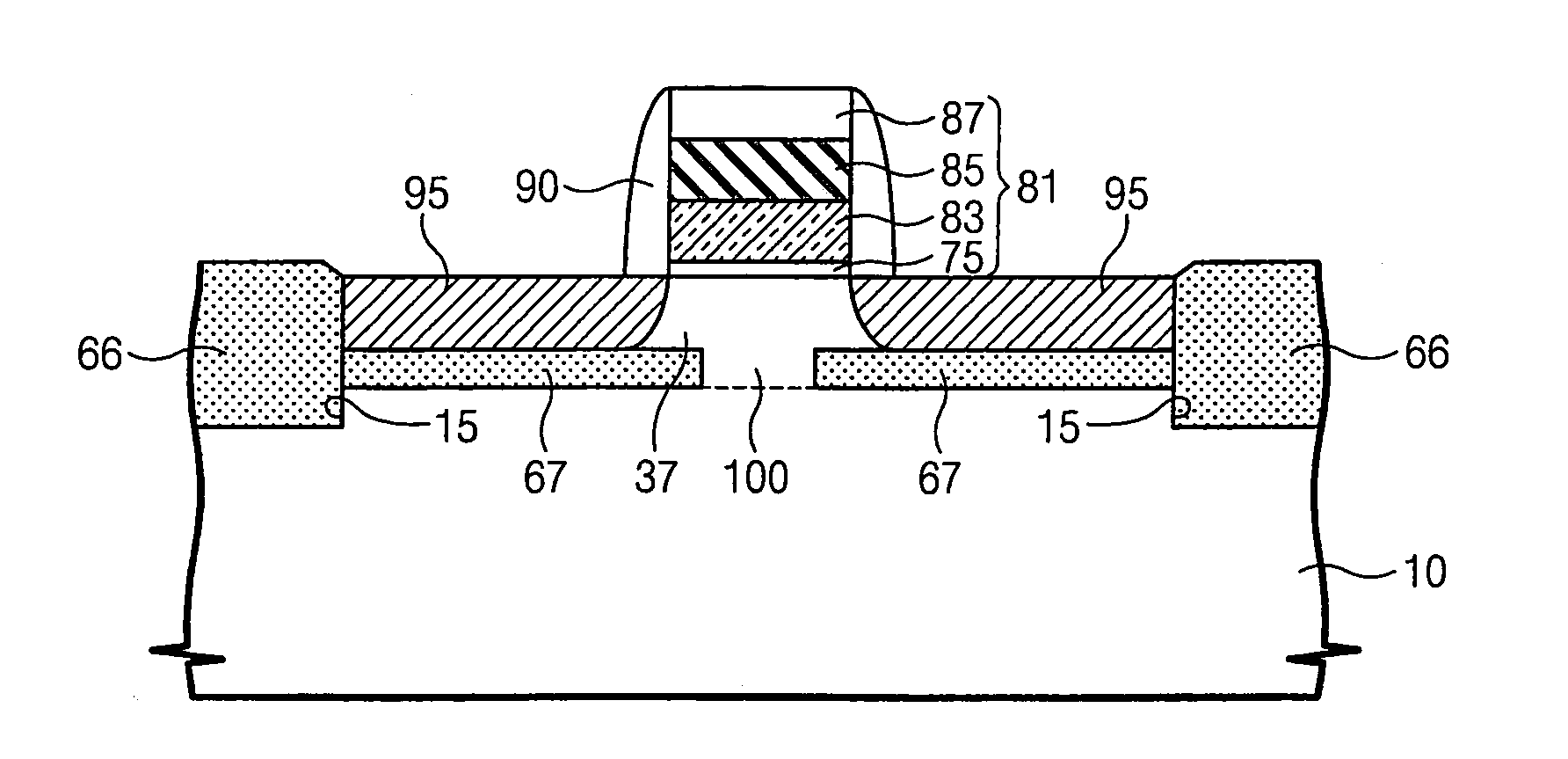

[0027]FIGS. 3A, 4A, 5A, 6A, 7A, and 8A are plan diagrams illustrating a method of fabricating a semiconductor device according to some embodiments of the invention. FIGS. 3B, 4B, 5B, 6B, 7B, and 8B are cross-sectional diagrams taken along the I-I′ lines of FIGS. 3A, 4A, 5A, 6A, 7A, and 8A, respectively. FIGS. 3C, 4C, 5C, 6C, 7C, and 8C are cross-sectional diagrams taken along the II-II′ lines of FIGS. 3A, 4A, 5A, 6A, 7A, and 8A, respectively.

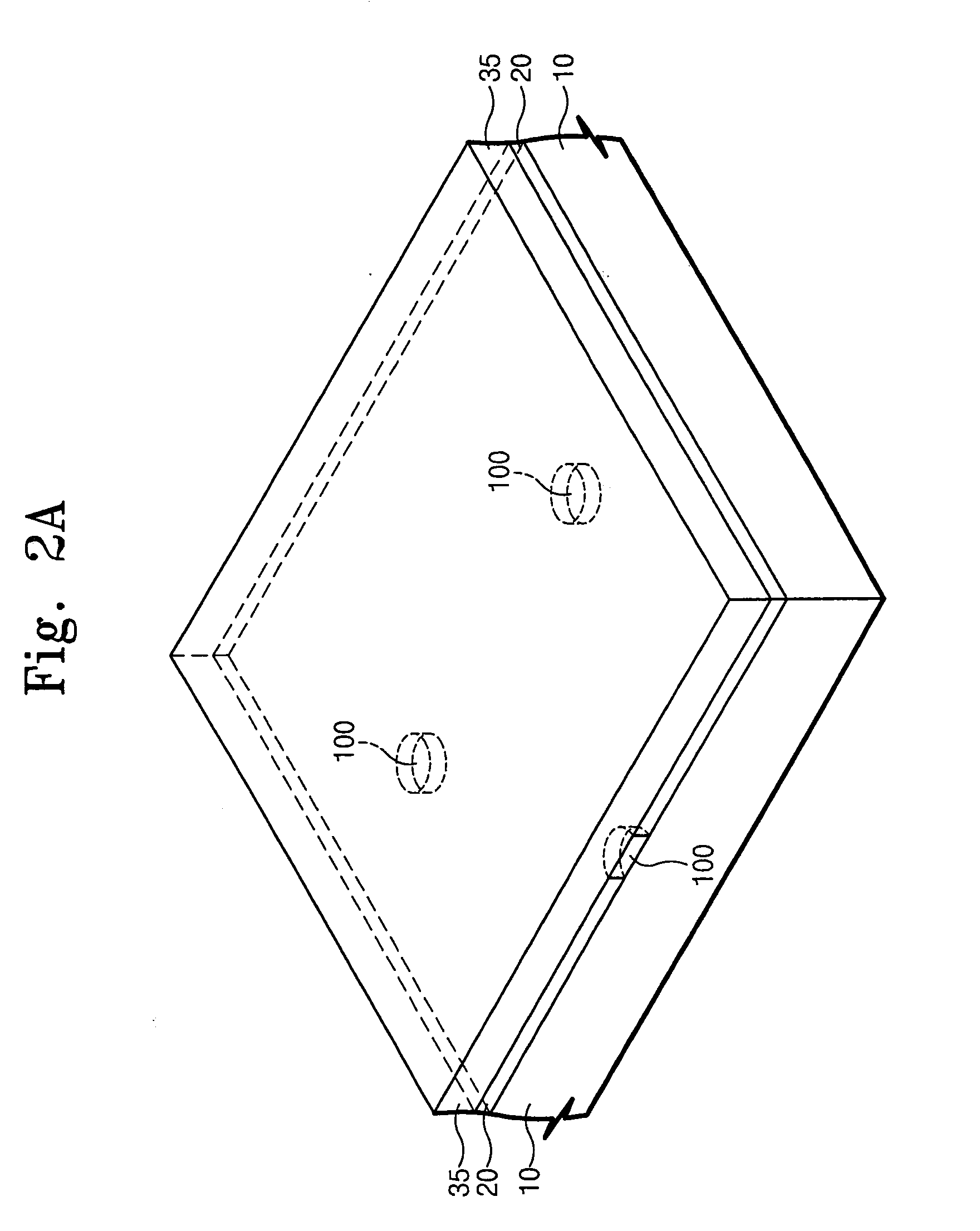

[0028]Referring to FIGS. 3A, 3B, and 3C, a sacrificial layer 20 and a seed semiconductor layer30 are sequentially formed on a bottom semiconductor layer 10. The seed semiconductor layer 30 and the sacrificial layer 20 are patterned to form at least one opening 99 exposing the bottom semiconductor layer 10 at a predetermined region. At this time, an opening mask pattern 40 may ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| stress | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More