Gate structure

a technology of gate structure and dielectric layer, which is applied in the direction of basic electric elements, electrical apparatus, and semiconductor devices, can solve the problems of high-k dielectric layer, rapid increase of leakage current, and drop in mobility and device reliability, and achieve the effect of increasing device performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027]Reference will now be made in detail to the present preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used in the drawings and the description to refer to the same or like parts.

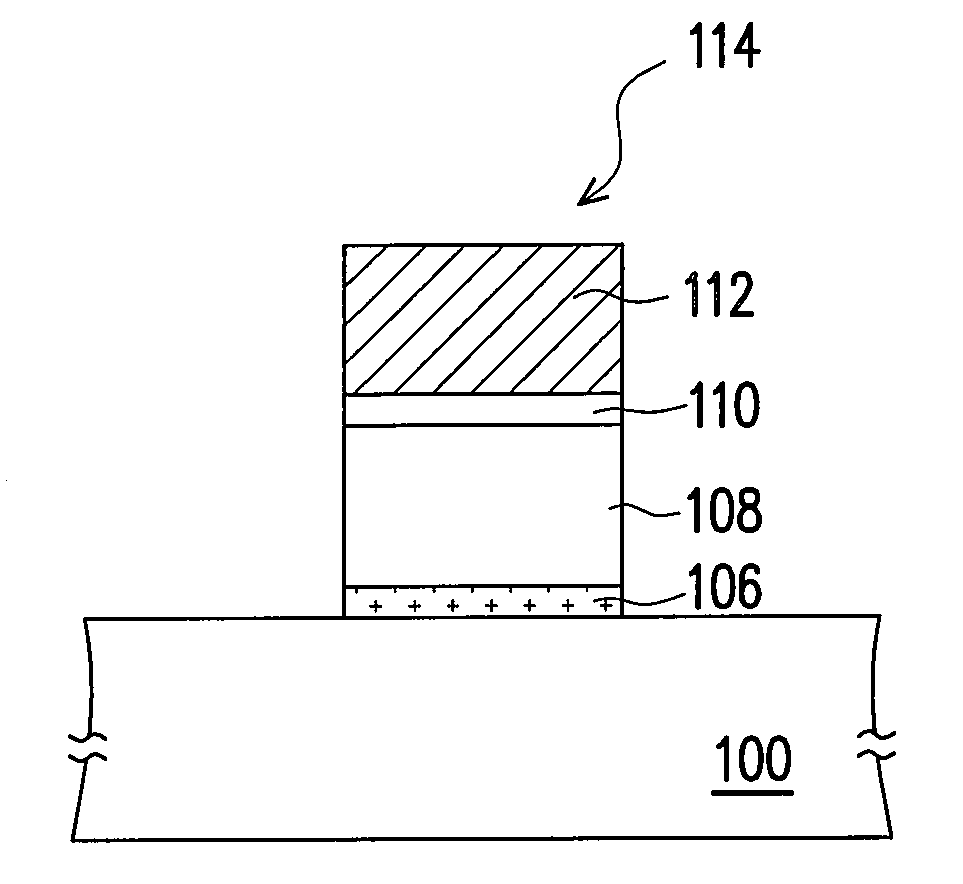

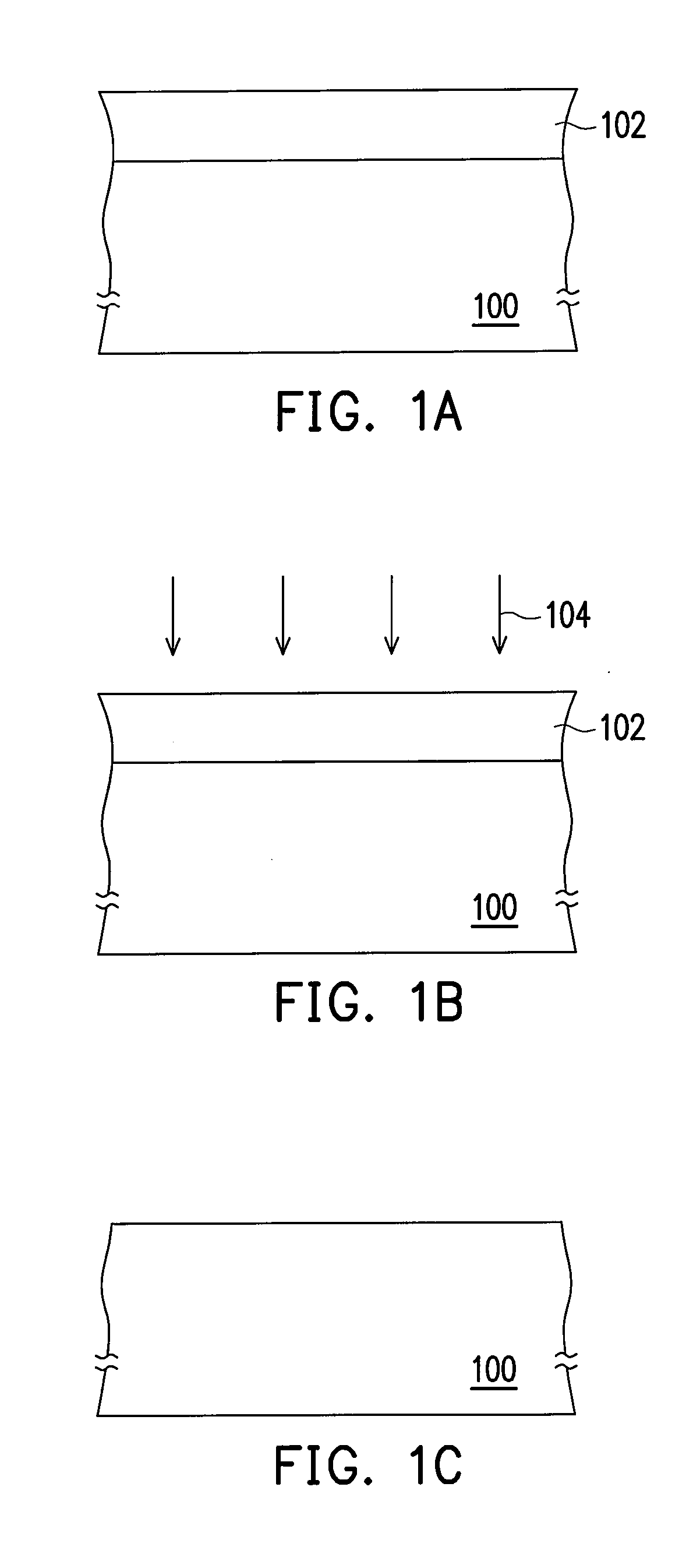

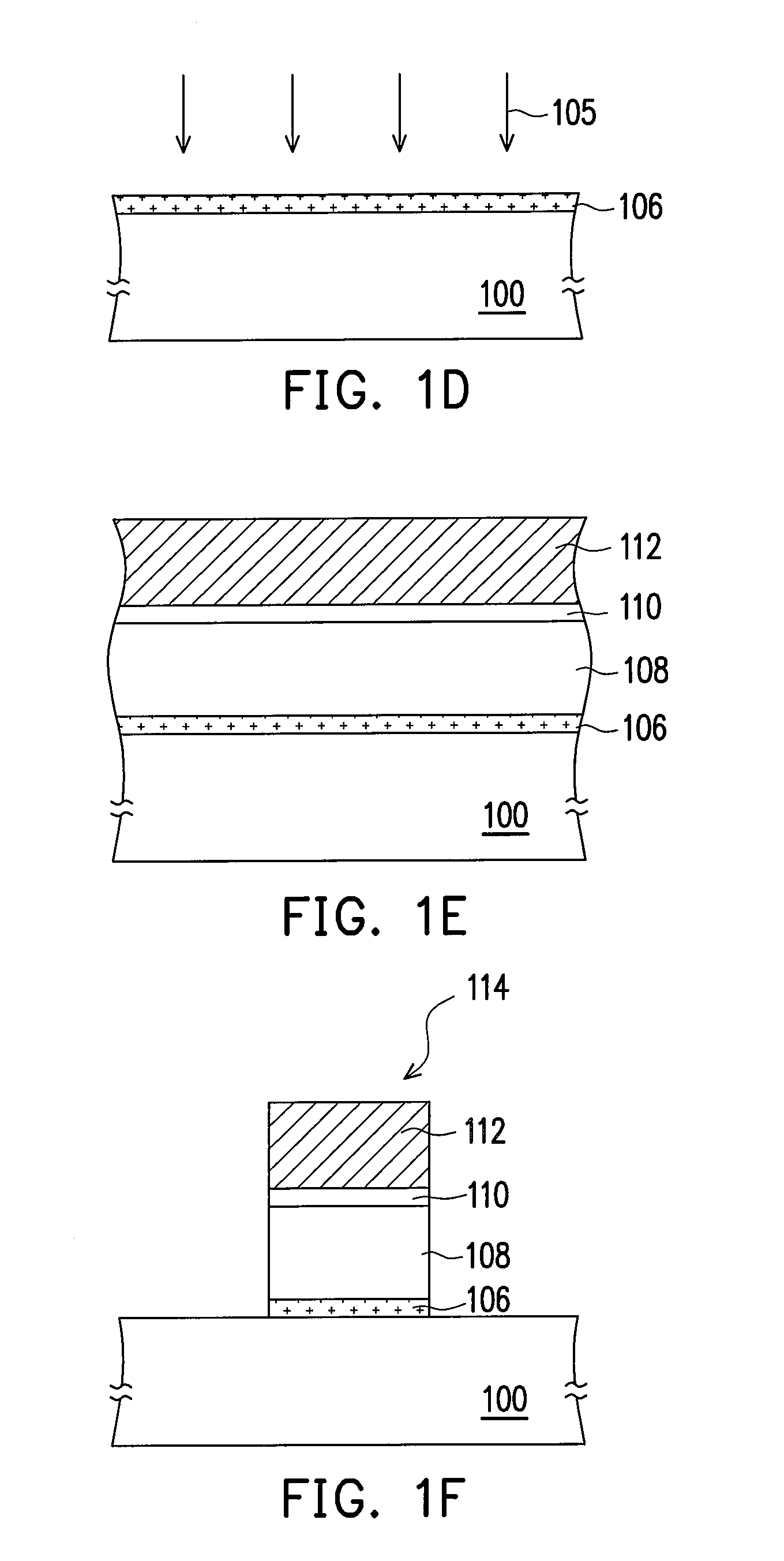

[0028]The method of fabricating a gate structure in the present invention includes forming an interface layer between a high dielectric constant (high-K) dielectric layer and a silicon substrate so that the problem of having inferior properties at the interface between a high-K dielectric layer and a silicon substrate is resolved. The conventional method includes forming an oxide layer over the silicon substrate and performing a plasma process to form the interface layer. As a result, the plasma may damage the surface of the interface layer and the oxide layer may re-grow. In another conventional method, a plasma nitridation process is performed before performing a re-oxidation process to form the af...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More