Vertical Type Nanotube Semiconductor Device

a semiconductor device, vertical type technology, applied in the direction of solid-state devices, transistors, nanoinformatics, etc., can solve problems such as electrical connection cutoff, and achieve the effect of improving adhesion and electrical connection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

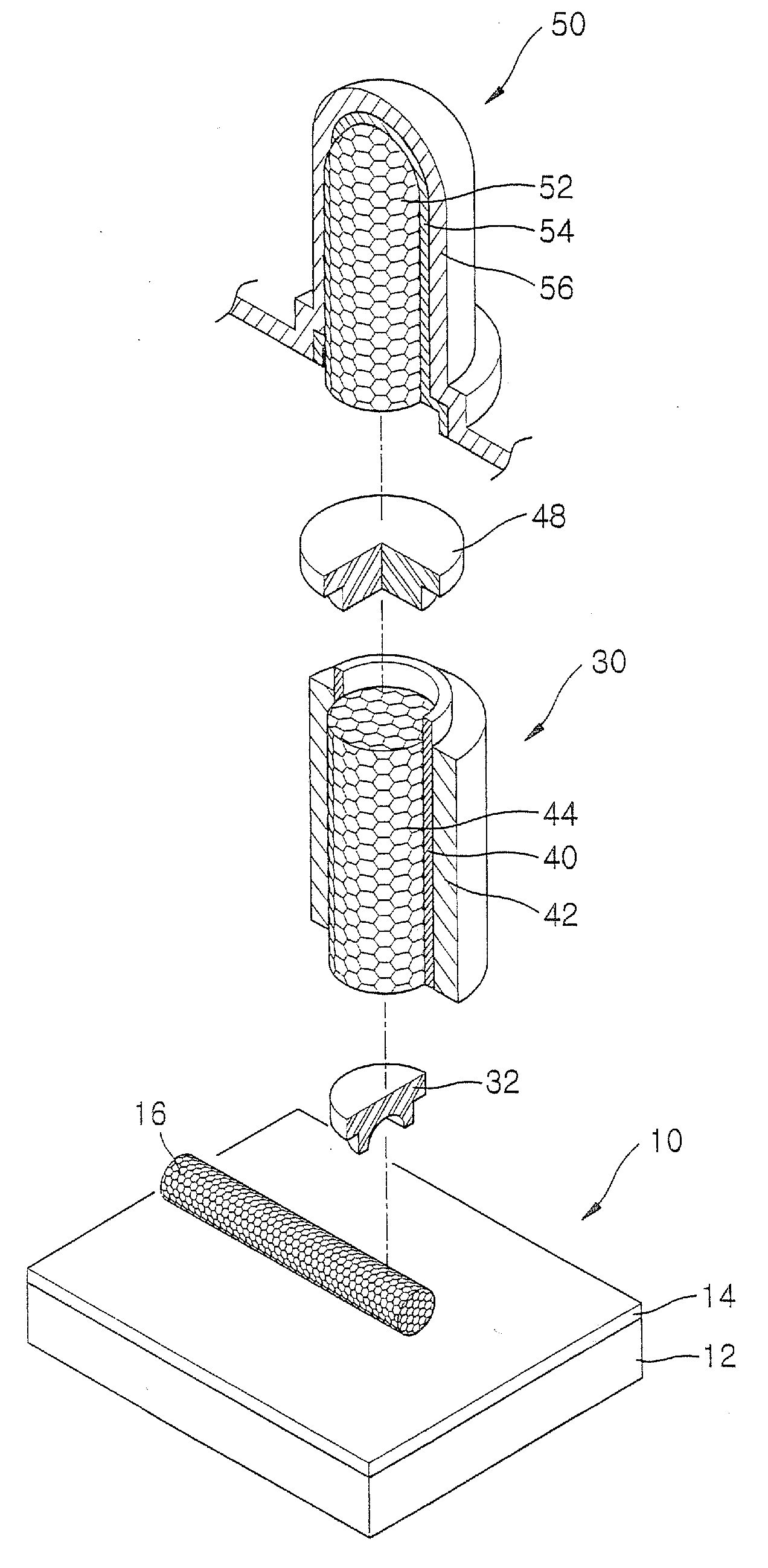

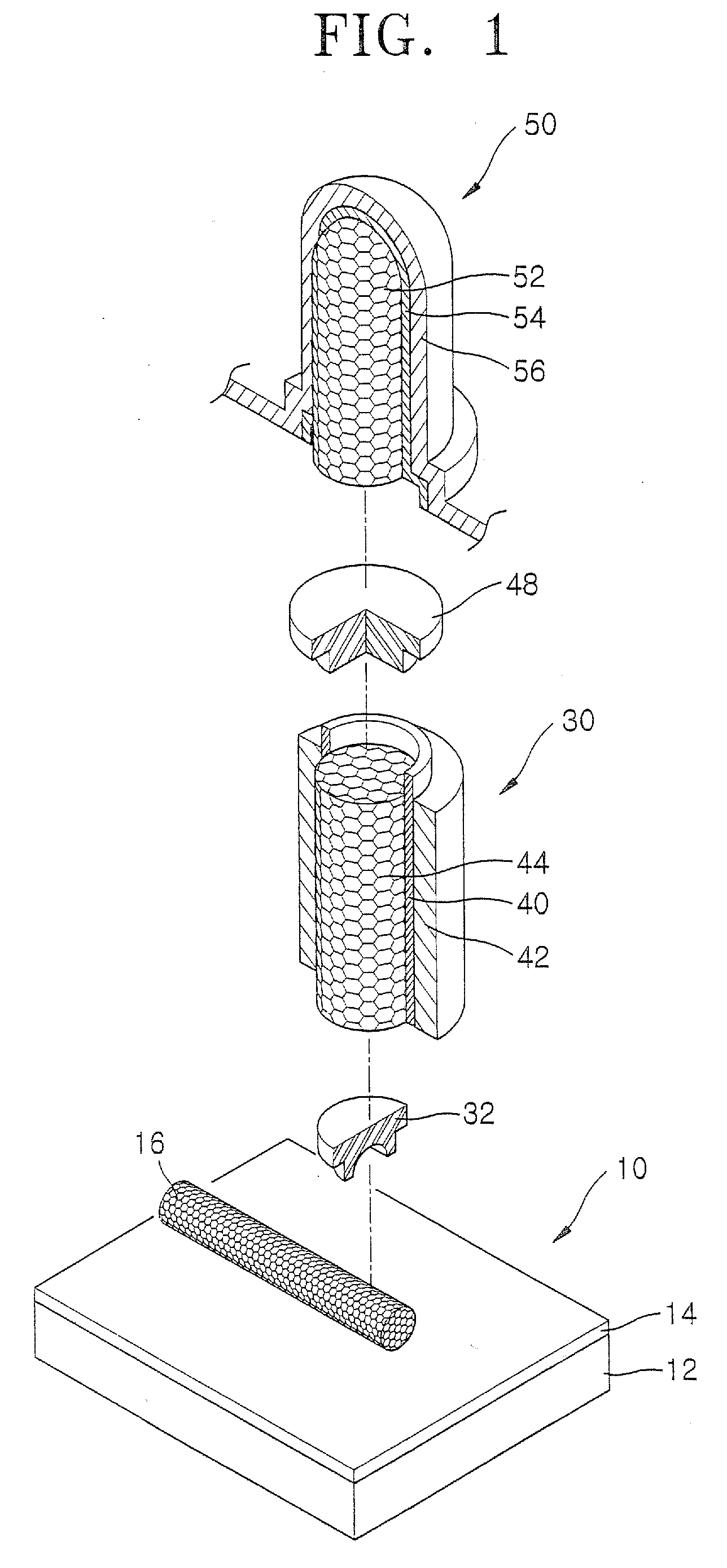

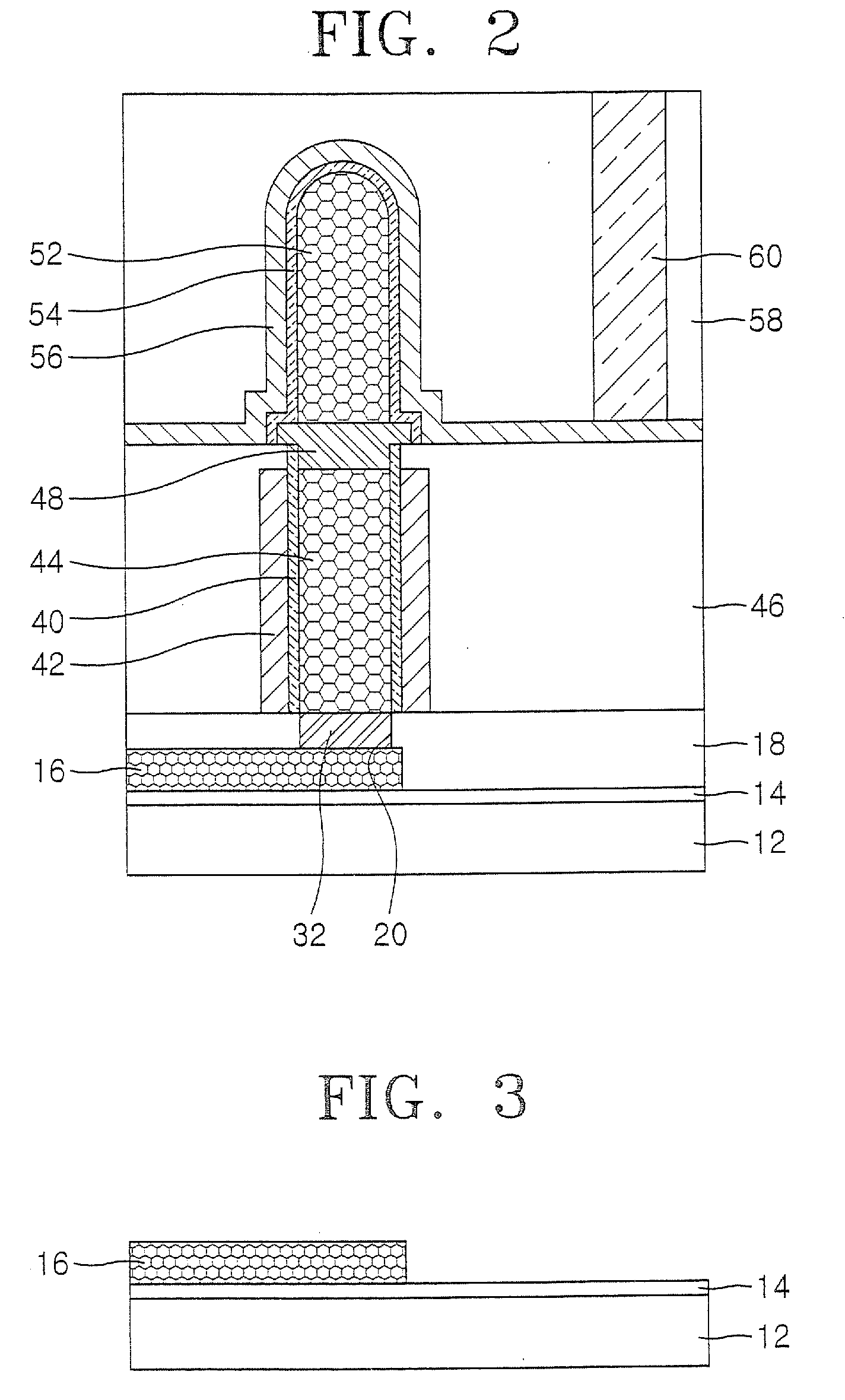

[0028]A nanotube semiconductor device according to the present invention has a vertical type structure. That is, a bit line formed on a substrate and an active region formed with a channel are arranged in the vertical direction with respect to the substrate. FIG. 1 is a perspective view of respective parts of a vertical type nanotube semiconductor device according to the present invention. FIG. 2 is a cross-sectional view showing major portions of FIG. 1. Referring to FIGS. 1 and 2, the vertical type nanotube semiconductor device includes a bit line part 10, a transistor part 30 and a capacitor part 50. The bit line part 10 includes a bit line 16 consisting of a nanotube with a conductive property disposed on a substrate 12 in parallel with the substrate 12. A first insulating layer 14 for electrical insulation may be disposed between the substrate 12 and the bit line 16. One end of the bit line 16 is connected to a recessed nanotube pole 44 extending vertically to the substrate 12....

second embodiment

[0046]FIG. 11 is an exploded perspective view of a vertical type nanotube semiconductor device according to the present invention. FIG. 12 is a cross-sectional view showing major portions of the device of FIG. 11. Referring to FIGS. 11 and 12, the vertical type nanotube semiconductor device is largely comprised of the bit line part 10, the transistor part 30, and the capacitor part 50. The bit line part 10 includes the bit line 16 consisting of the nanotube with the conductive property, and is disposed on the substrate 12 in parallel with the substrate 12. A first insulating layer 14 may be formed for electrical insulation between the substrate 12 and the bit line 16. The nanotube bit line 16 can be formed to have a nanometer dimension, and hardly has a grain boundary in the nanometer dimension, so that an electrical cutoff does not occur.

[0047]One end of the bit line 16 is connected to the recessed nanotube pole 44 extending in the vertical direction to the substrate 12. The recess...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com