Multiplier device with suppression of higher-order distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

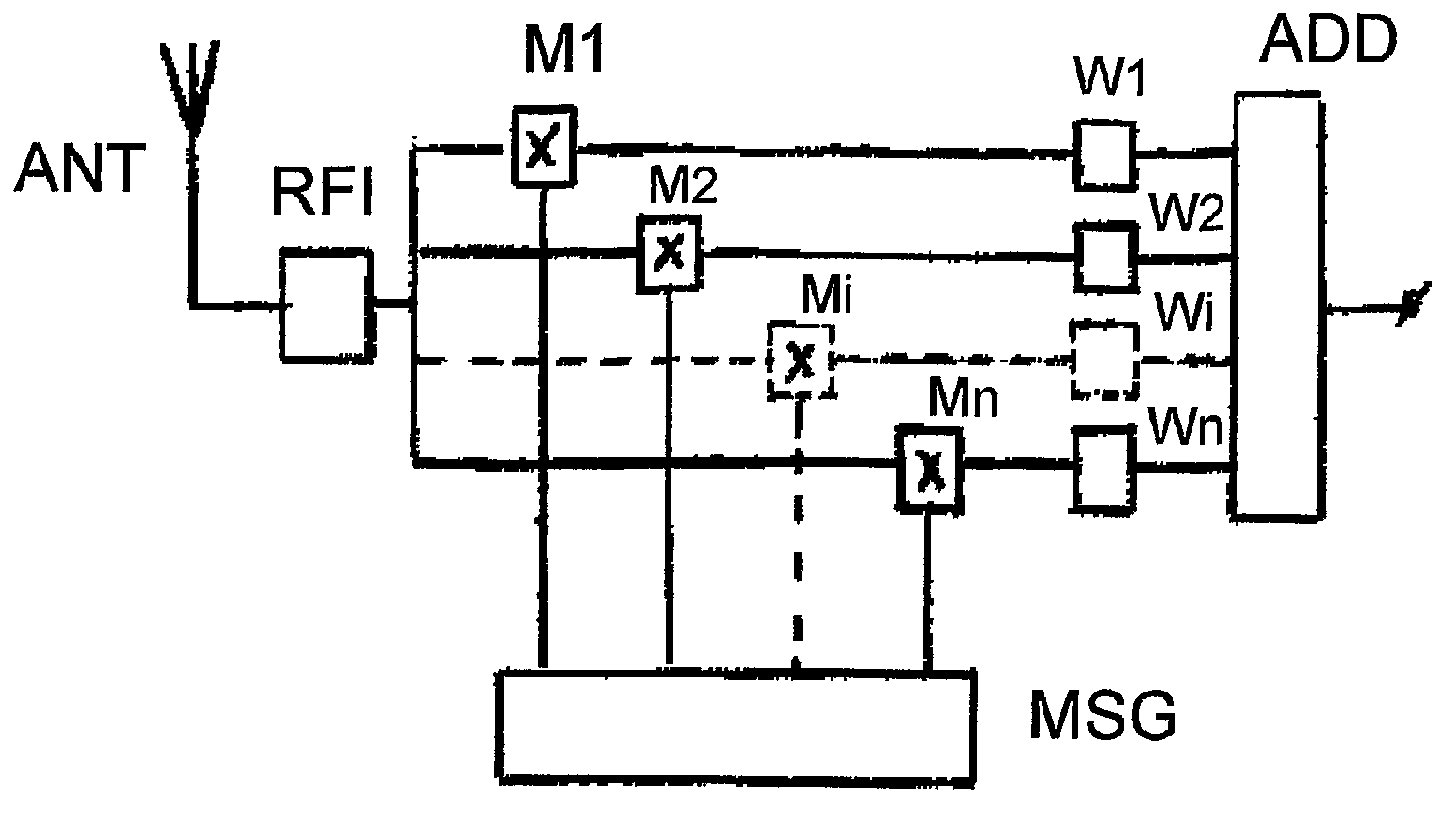

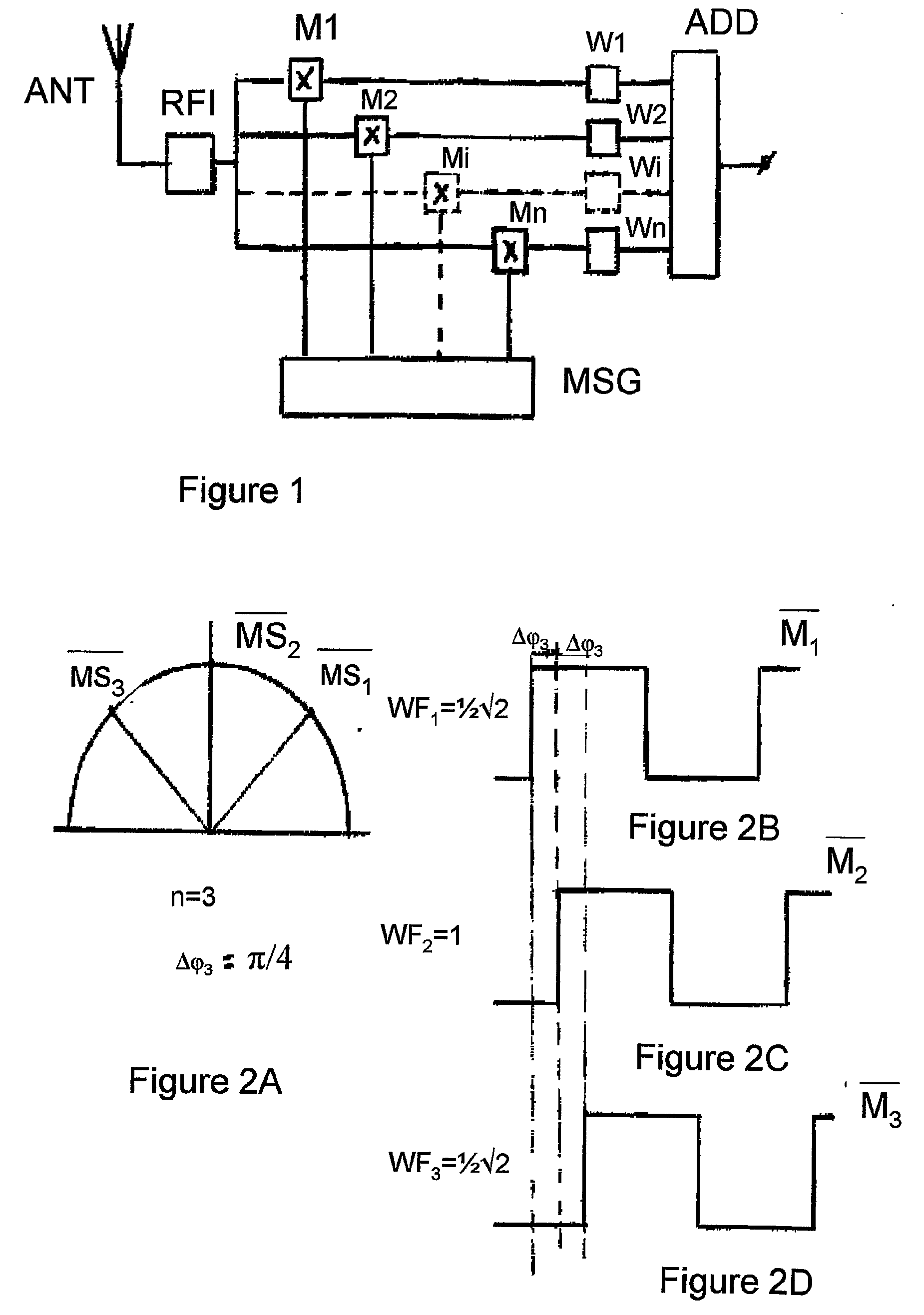

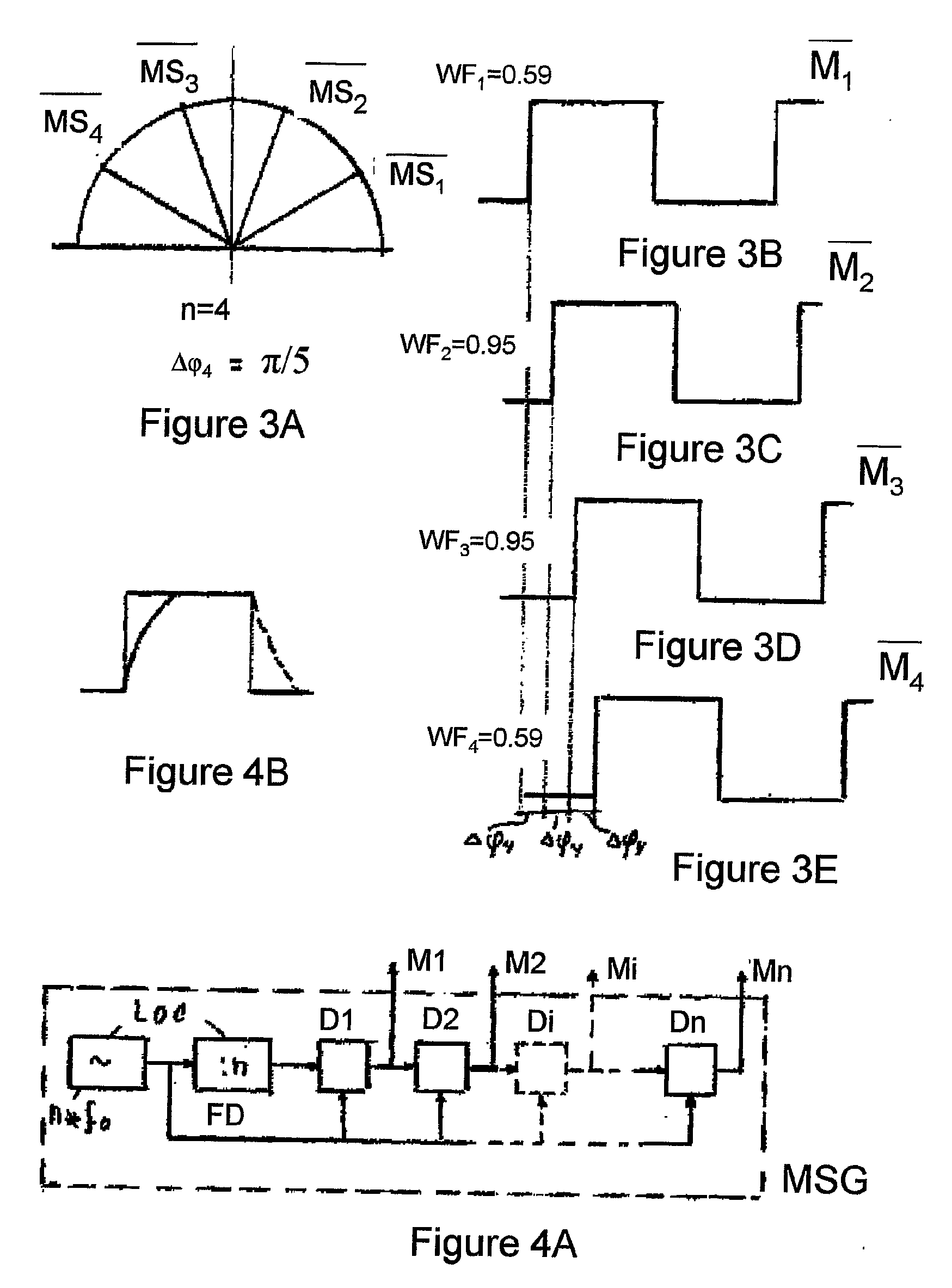

[0024]FIG. 1 shows an embodiment of a multiplier device (M1-Mn, W1-Wn, ADD) according to the invention used in a receiver front end. The receiver front end comprises an RF antenna ANT being coupled to an RF input unit RFI supplying an RF antenna input signal with an RF carrier frequency fRF in common to first to nth multipliers M1 to Mn, n being 3 or more. The RF antenna input signal is being demodulated therein into an intermediate frequency (IF) signal with an IF carrier frequency fIF. The first to nth multipliers M1 to Mn receive from a mixing signal generator MSG respectively first to nth mutually phase shifted and identical, substantially square wave mixing signals MS1 to MSn with 50% duty cycle. Outputs of the first to nth multipliers M1 to Mn are respectively coupled through weighting circuits W1 to Wn with respective fixed weighting factors WF1 to WFn to an adder circuit ADD. The adder circuit ADD provides at its output the IF signal without harmonic interferences up to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More