Gen3 pci-express riser

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

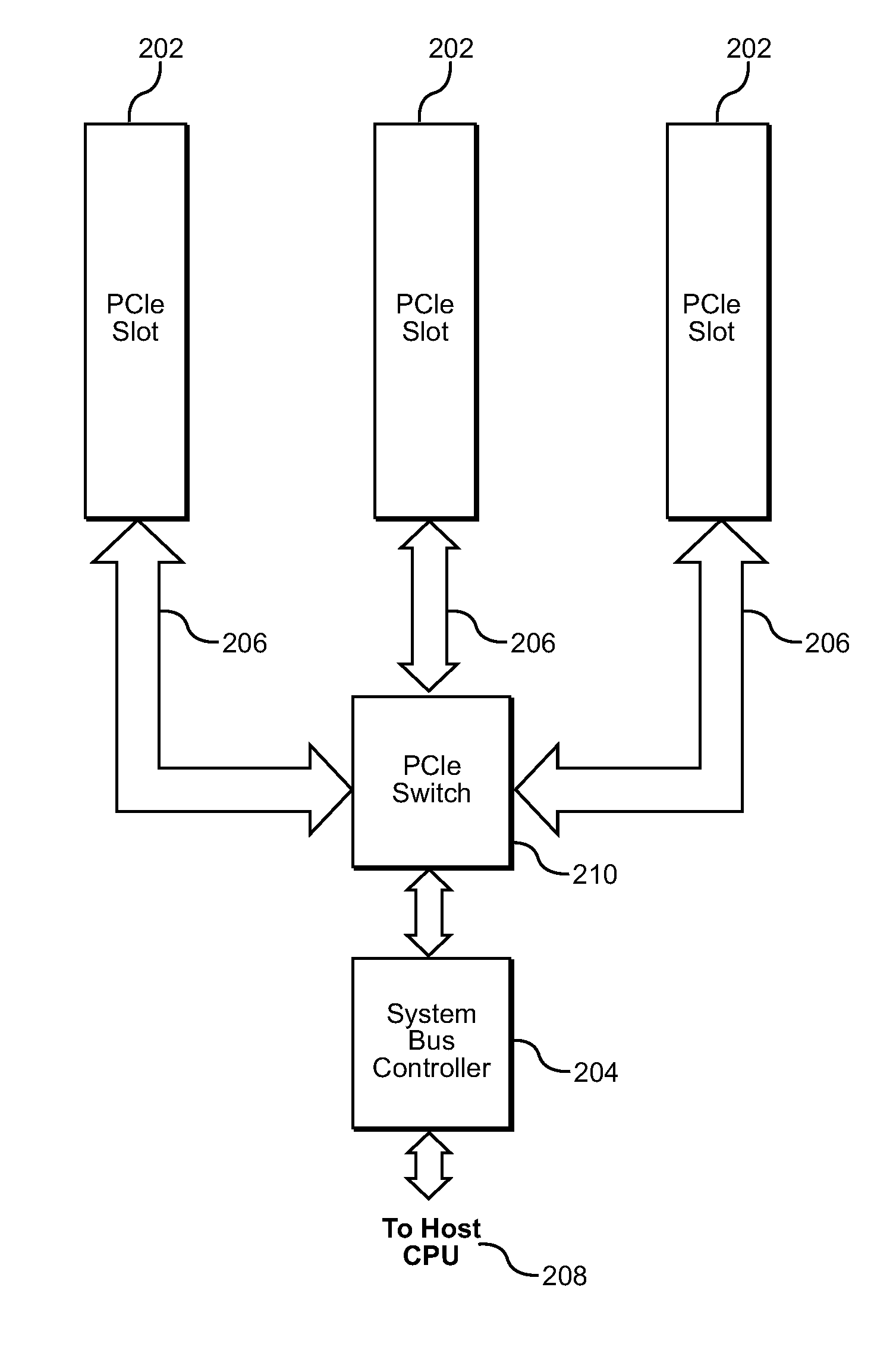

[0040]Referring to FIG. 1, a diagram of a traditional PCI interface is shown. PCI slots 102 are connected to Bus Controller 104 by way of PCI bus 106. The PCI bus 106 can be either 32-bits or 64-bits wide. Bus Controller 104 is also connected to a host CPU 108. PCI slots 102 are connected in parallel manner. More specifically, PCI Slots 102 share the same PCI bus 106. Only one PCI Slot 102 may communicate with the Bus Controller at a time or there will be contention on the PCI bus 106. If there is contention, meaning more than one PCI slot 102 is attempting to communicate with the Bus Controller 104 at the same time, the data being placed on the PCI bus will be corrupt. To prevent data corruption, bus controller 104 controls which PCI slot 102 is allowed to place data on the PCI bus 106. When that data transfer is complete, bus controller 106 then allows another data transfer from a different PCI slot 102 or the same PCI slot 102 that originally transferred data, again allowing only...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap