Overlay marks and semiconductor process using the overlay marks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

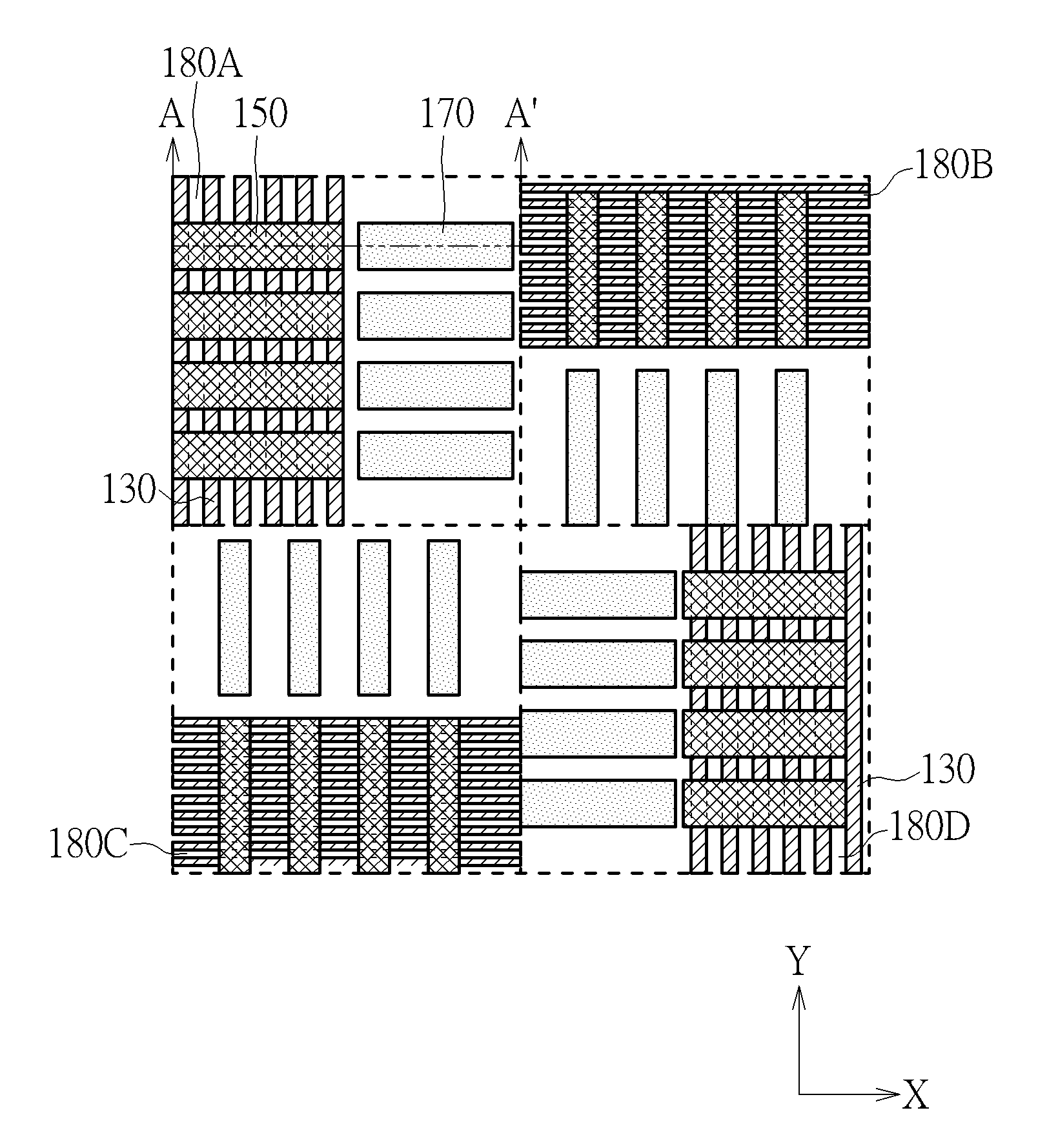

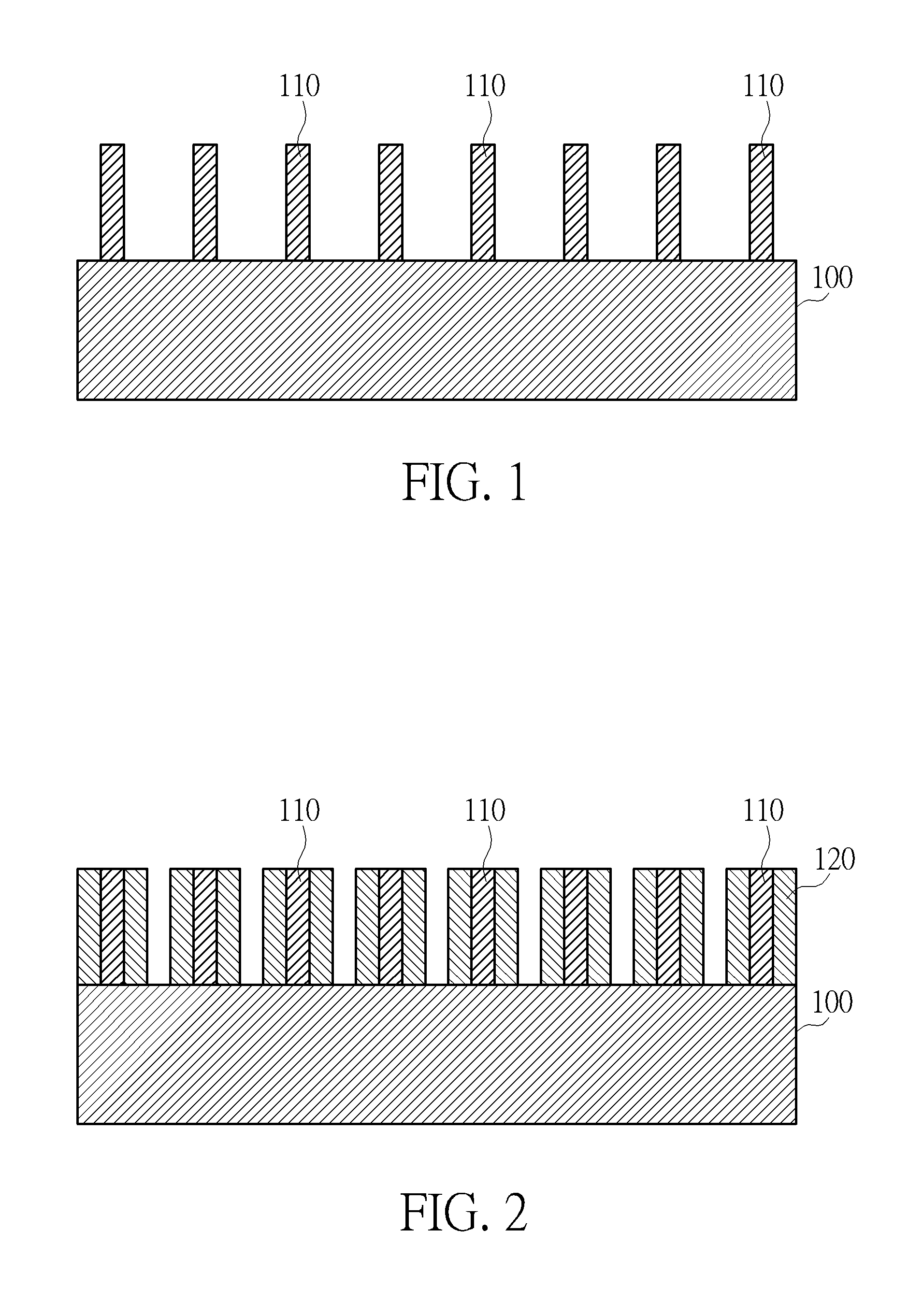

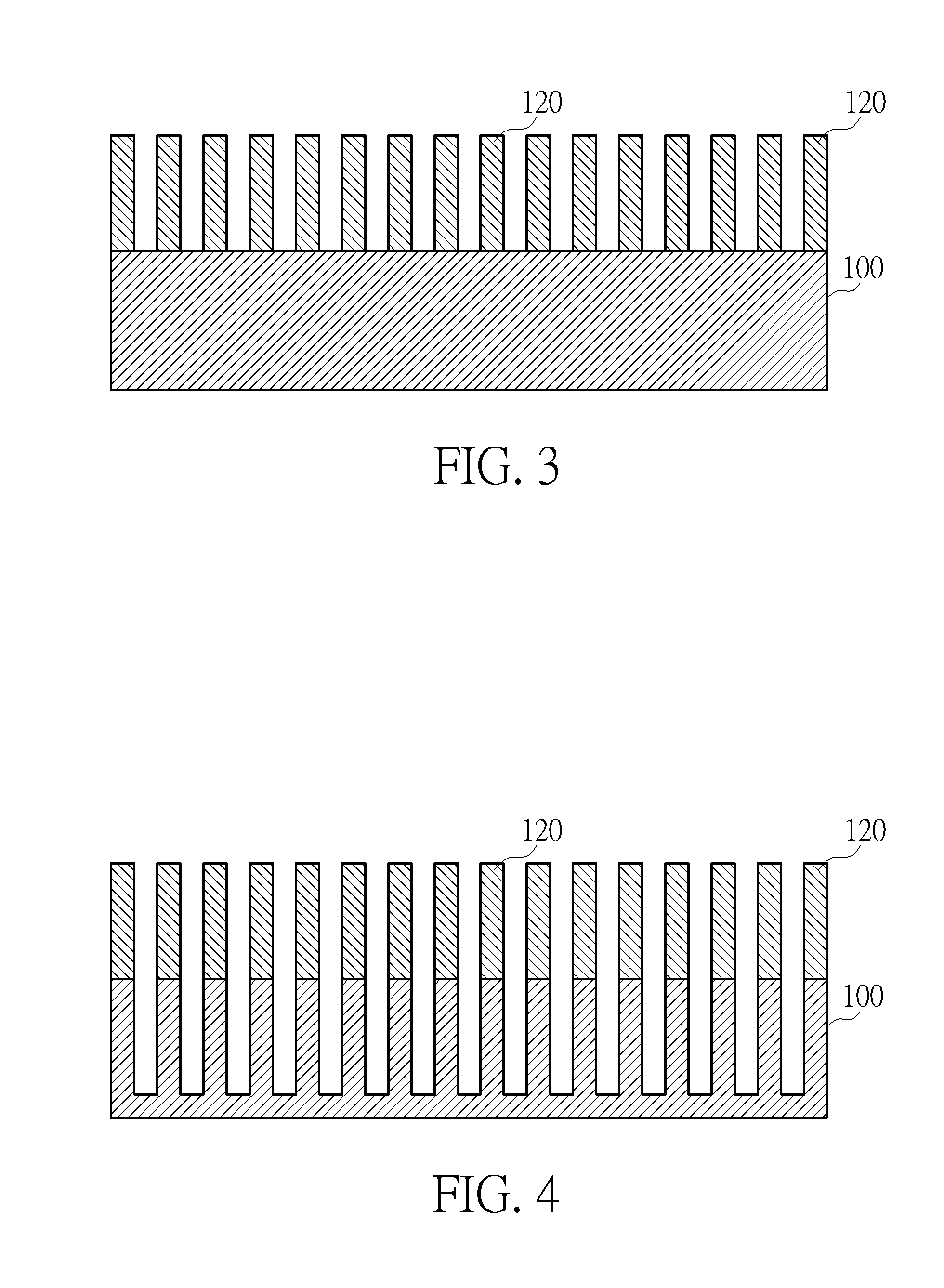

[0018]The present invention, in each of the various embodiments, uses overlay marks that are composed of periodic structures formed on each of two layers of a semiconductor wafer to provide overlay information between those two layers of the semiconductor device. The overlay marks are formed in specific locations on each wafer layer such that the periodic structures on one layer will be aligned with the periodic structures on the other layer when the two layers are properly aligned. Conversely, the periodic structures on each layer will be offset from each other when the two layers are not properly aligned. Alternatively, the present invention may use overlay marks that are composed of periodic structures formed on a single layer by two or more separate processes to provide alignment information between two different patterns on the same layer. Each of the periodic structures is composed of a plurality of structures, which increases the amount of information that may be used to meas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com