Memory device, memory system including the same, and operation method thereof

a memory device and memory technology, applied in the field of memory systems, can solve the problems of reducing the initial amount of charge stored in the capacitor of the memory cell, and reducing the interval between adjacent word lines in the memory devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

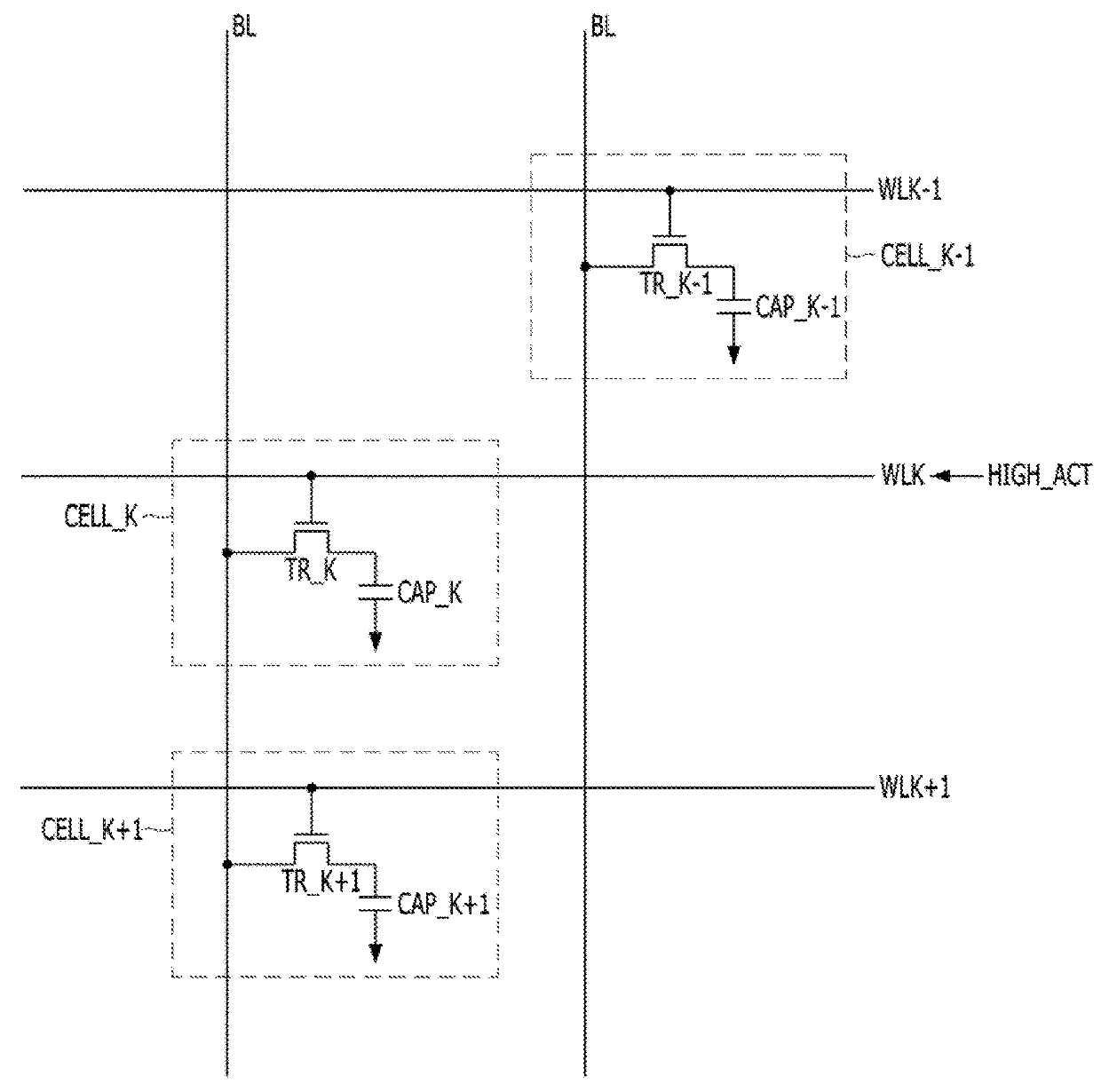

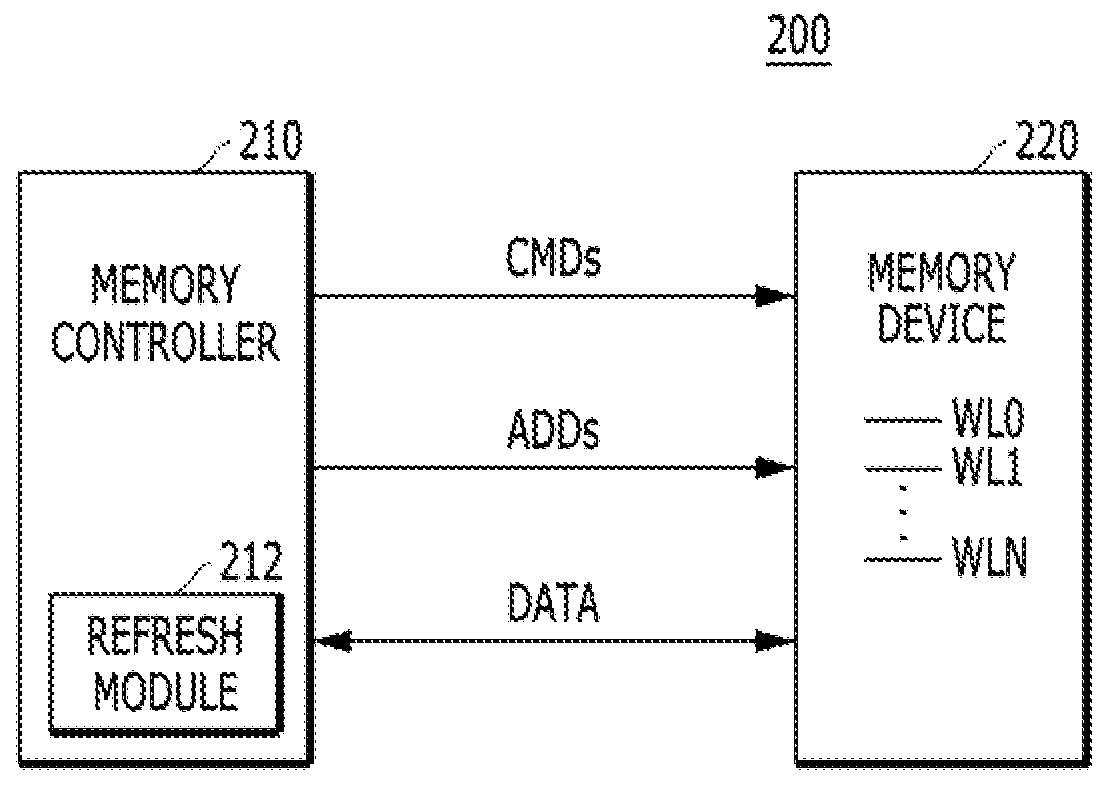

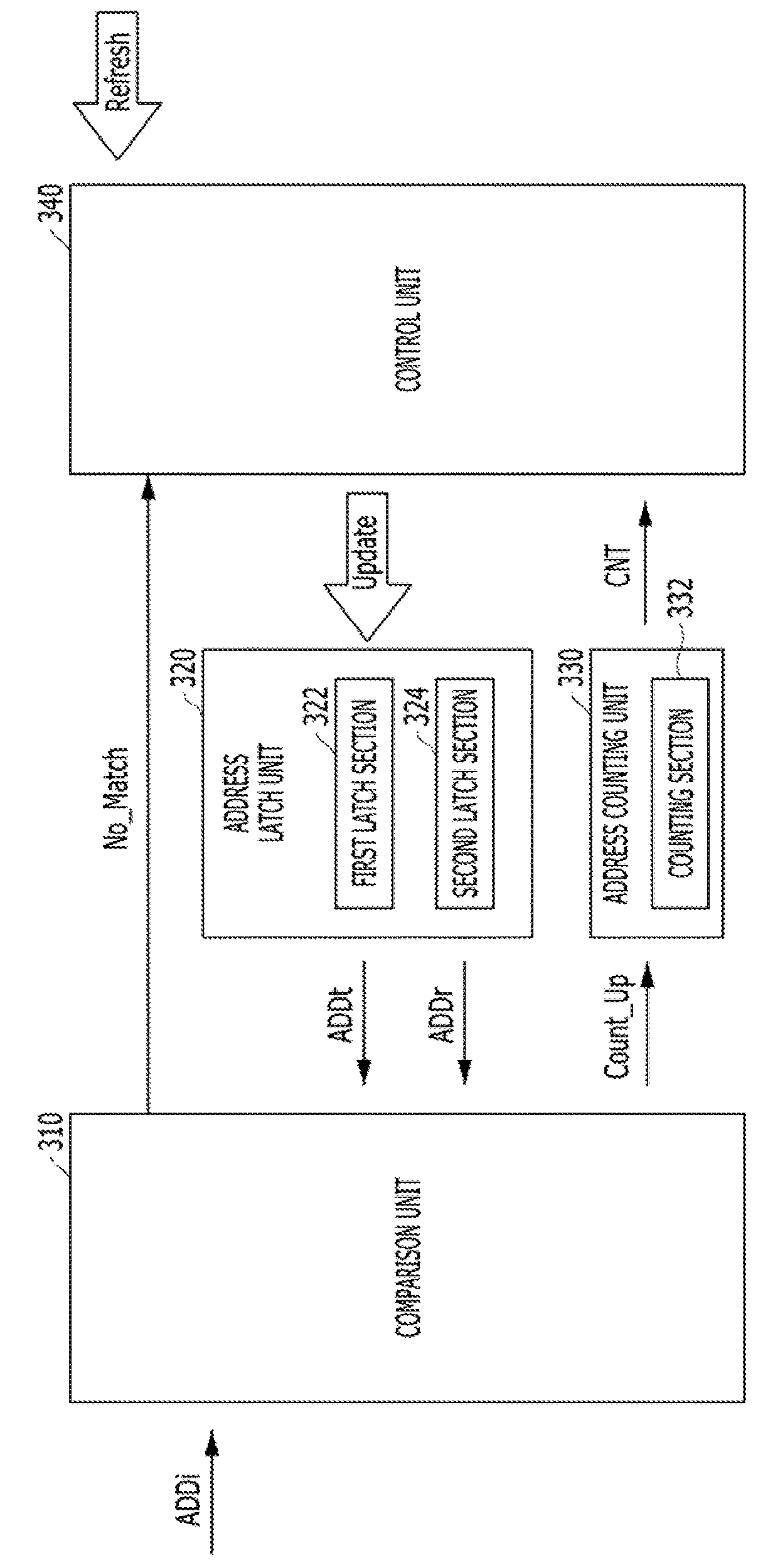

[0020]Various embodiments will be described below in more detail with reference to the accompanying drawings. The present invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the present invention to those skilled in the art. Throughout the disclosure, like reference numerals refer to like parts throughout the various figures and embodiments of the present invention.

[0021]It is noted that the drawings are simplified schematics and as such are not necessarily drawn to scale. In some instances, various parts of the drawings may have been exaggerated in order to more clearly illustrate certain features of the illustrated embodiments.

[0022]It is further noted that in the following description, specific details are set forth for facilitating the understanding of the present invention,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More