Verification-processing device, logic-generating device, and verification-processing method

a logic-generating device and verification-processing technology, applied in the direction of short-circuit testing, computer aided design, instruments, etc., can solve problems such as difficulty in verification, and achieve the effect of verifying safety

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

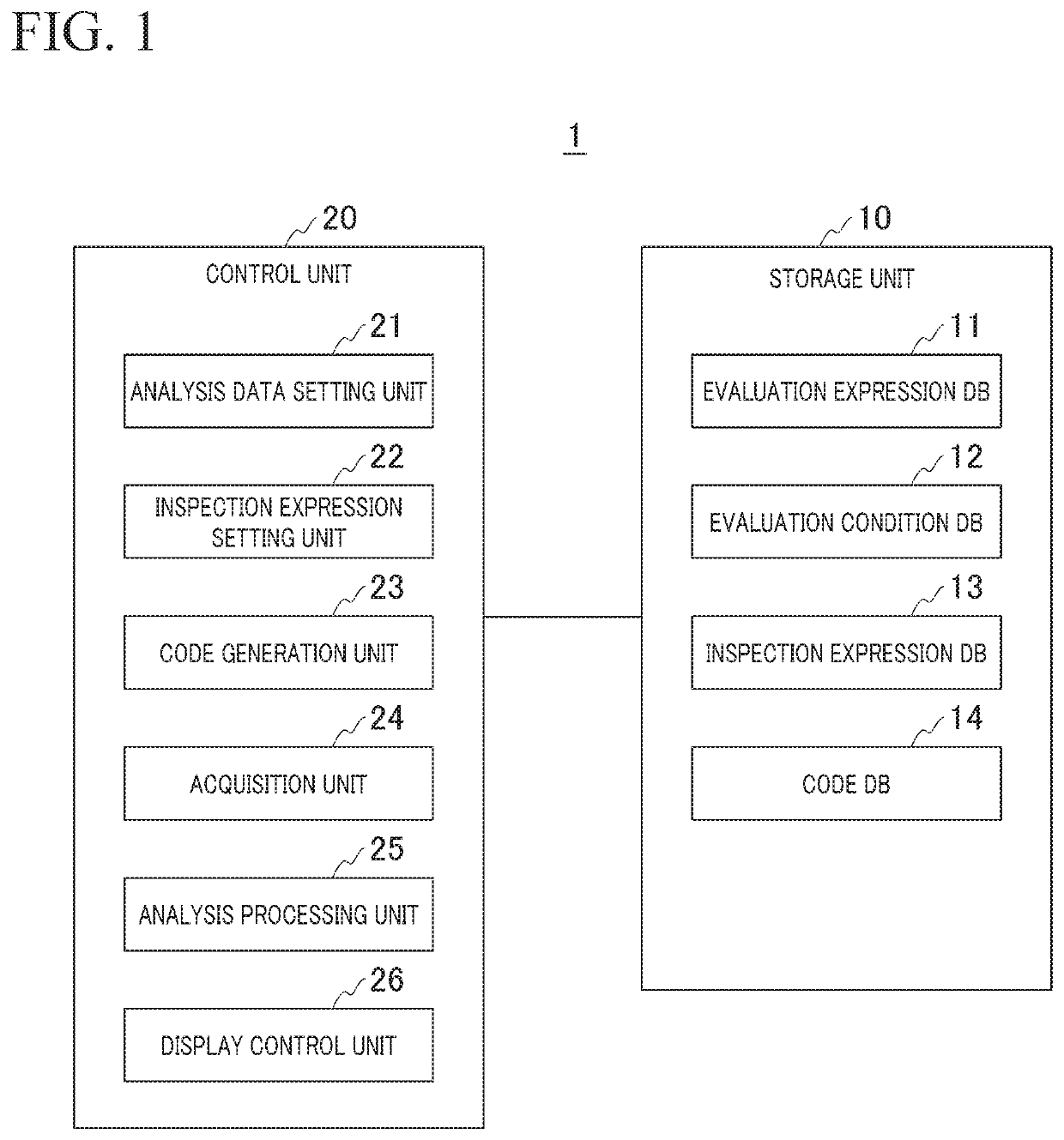

[0045]FIG. 1 is a configuration diagram showing a schematic configuration of a verification-processing device of the present embodiment.

[0046]As illustrated in FIG. 1, the verification-processing device 1 according to the present embodiment includes a storage unit 10 and a control unit 20.

[0047]The storage unit 10 stores data regarding the evaluation expression DB 11, the evaluation condition DB 12, the inspection expression DB 13, and the code DB 14.

[0048]The evaluation expression DB 11 includes data regarding the evaluation expression for the relay logic circuit to be evaluated. The evaluation expression is formed as a logical expression in which the relay, the element, and the connection line forming the relay logic circuit to be verified are variables. This evaluation expression includes at least a logical expression when a failure event occurs in the relay logic circuit. For example, the logical expression is generated for each relay whose operation is to be analyzed.

[0049]The ...

second embodiment

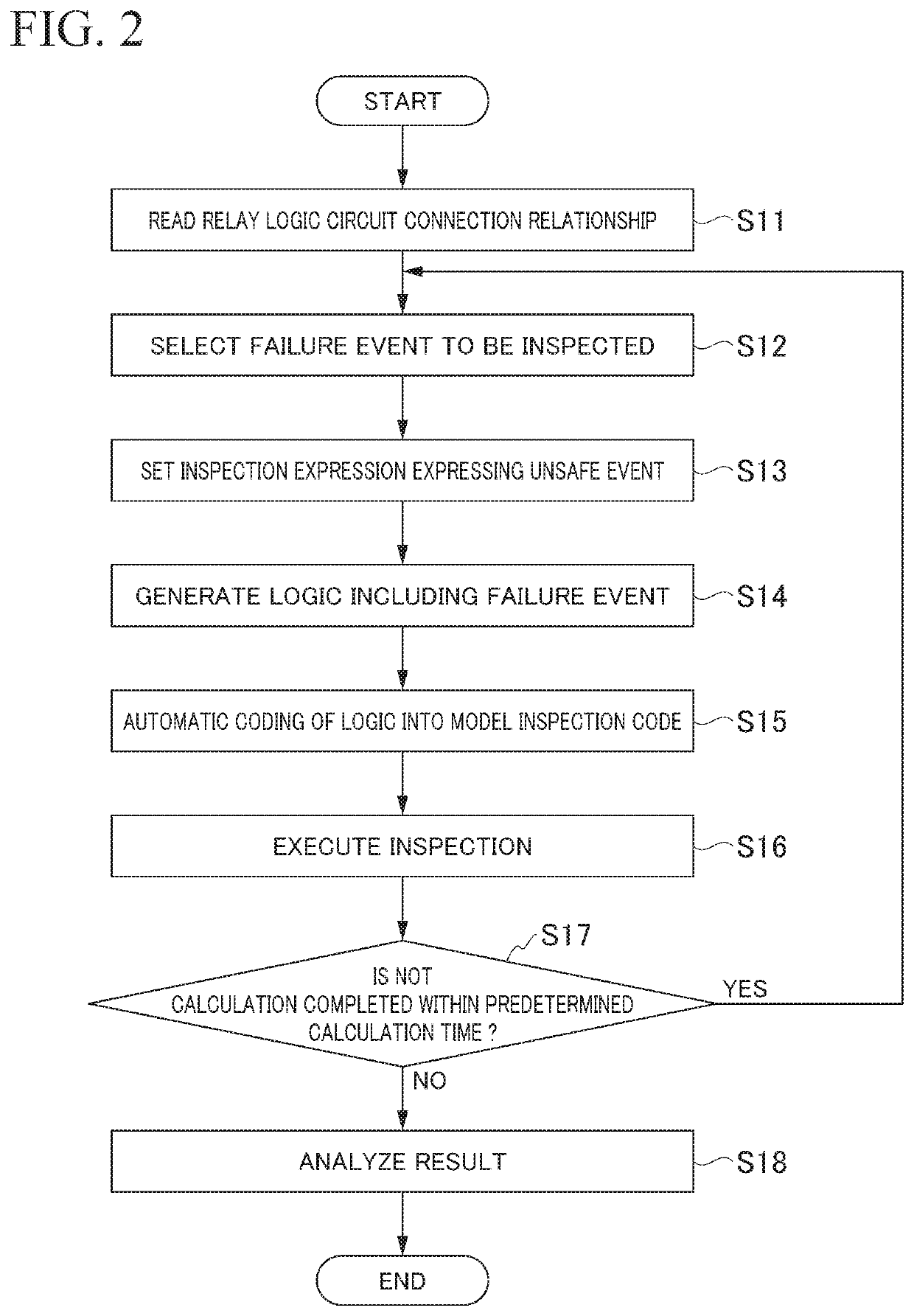

[0124]Subsequently, a second embodiment will be described with reference to drawings of FIG. 2 and FIGS. 6 to 15. Although the logic verification code as the model for logic verification is generated by the user in the first embodiment, the logic verification code of the present embodiment is generated by the verification-processing device.

[0125]FIG. 6 is a configuration diagram showing a schematic configuration of a verification-processing device of the present embodiment.

[0126]As illustrated in FIG. 6, the verification-processing device 1A according to the present embodiment includes a storage unit 10A and a control unit 20A.

[0127]The storage unit 10A includes an evaluation expression DB 11, an evaluation condition DB 12, an inspection expression DB 13, a code DB 14, an element information DB 15, and a signal information DB 16.

[0128]The element information DB 15 (Dev table) includes data of configuration information regarding the elements included in the relay logic circuit subjec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More