System and method for correcting connectivity errors in a mask layout file

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

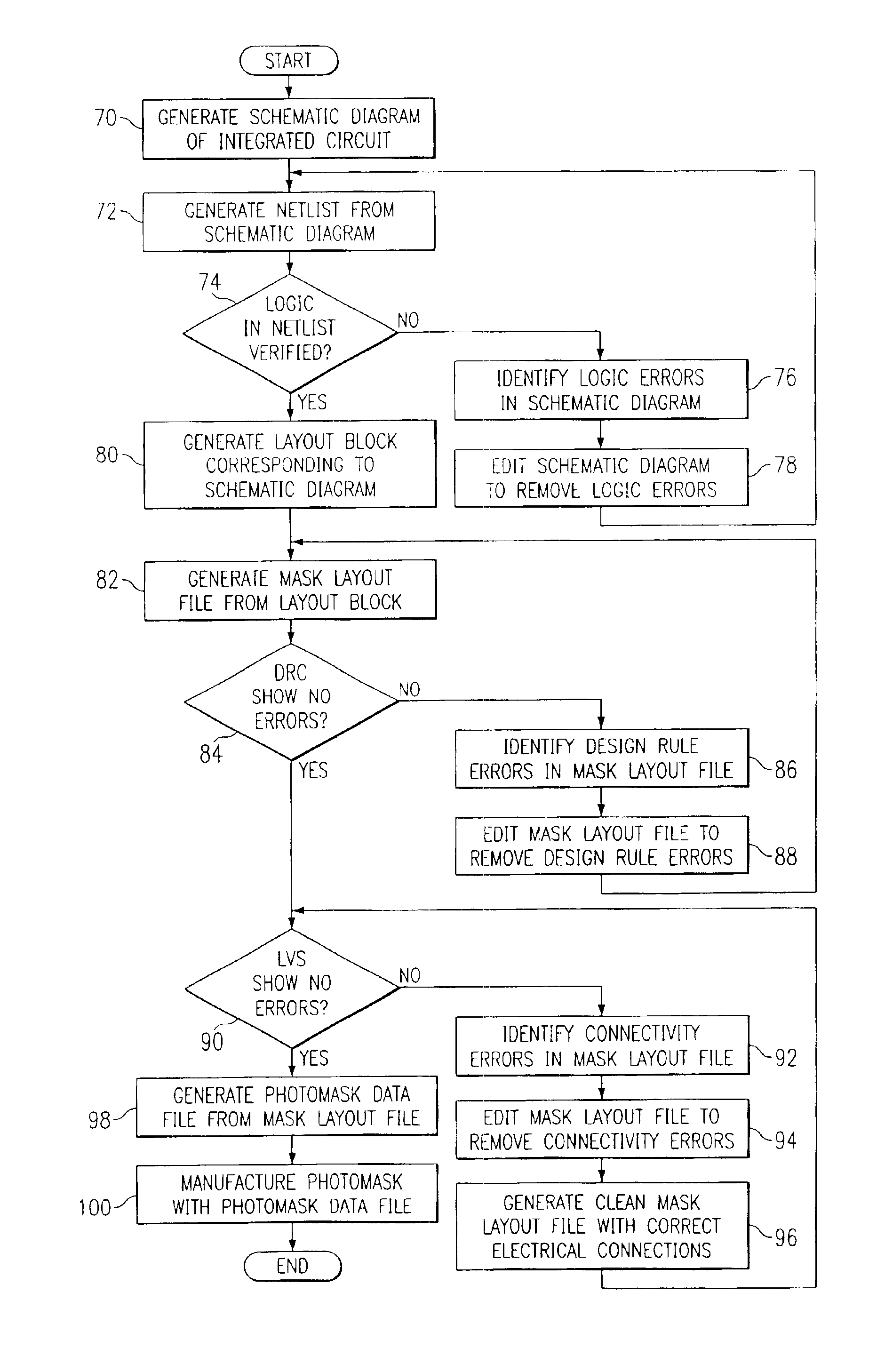

[0019]Preferred embodiments of the invention and its advantages are best understood by reference to FIGS. 1 through 5 of the drawings, like numerals being used for like and corresponding parts of the various drawings.

[0020]FIG. 1 illustrates a block diagram of computer system 10 that may be used to correct connectivity errors in a mask layout file. In the illustrated embodiment, computer system 10 includes processing resource 12, memory 14 and display device 16. Processing resource 12 may be a microprocessor, a microcontroller, a digital signal processor (DSP) or any other digital or analog circuitry configured to execute processing instructions stored in memory 14. Memory 14 may be random access memory (RAM), electrically erasable programmable read-only memory (EEPROM), a PCMCIA card, flash memory, or any suitable selection and / or array of volatile or nonvolatile memory that retains data after the power to computer system 10 is turned off. Display device 16 may be a liquid crystal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More