Semiconductor memory device

a memory device and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical apparatus, etc., can solve the problems of unsuitable structure for large capacity and concern about short circui

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

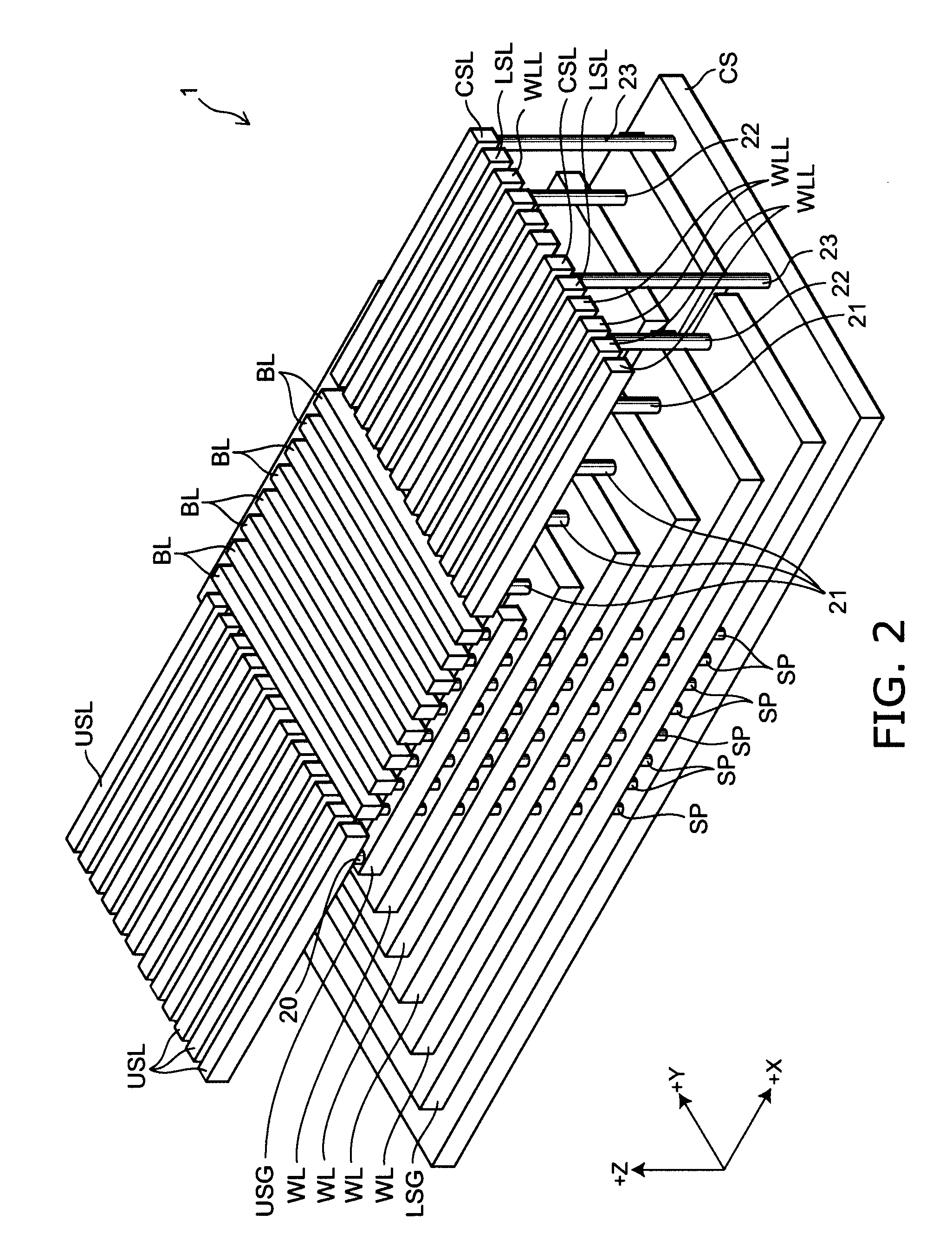

[0023]An embodiment of the invention will now be described with reference to the drawings.

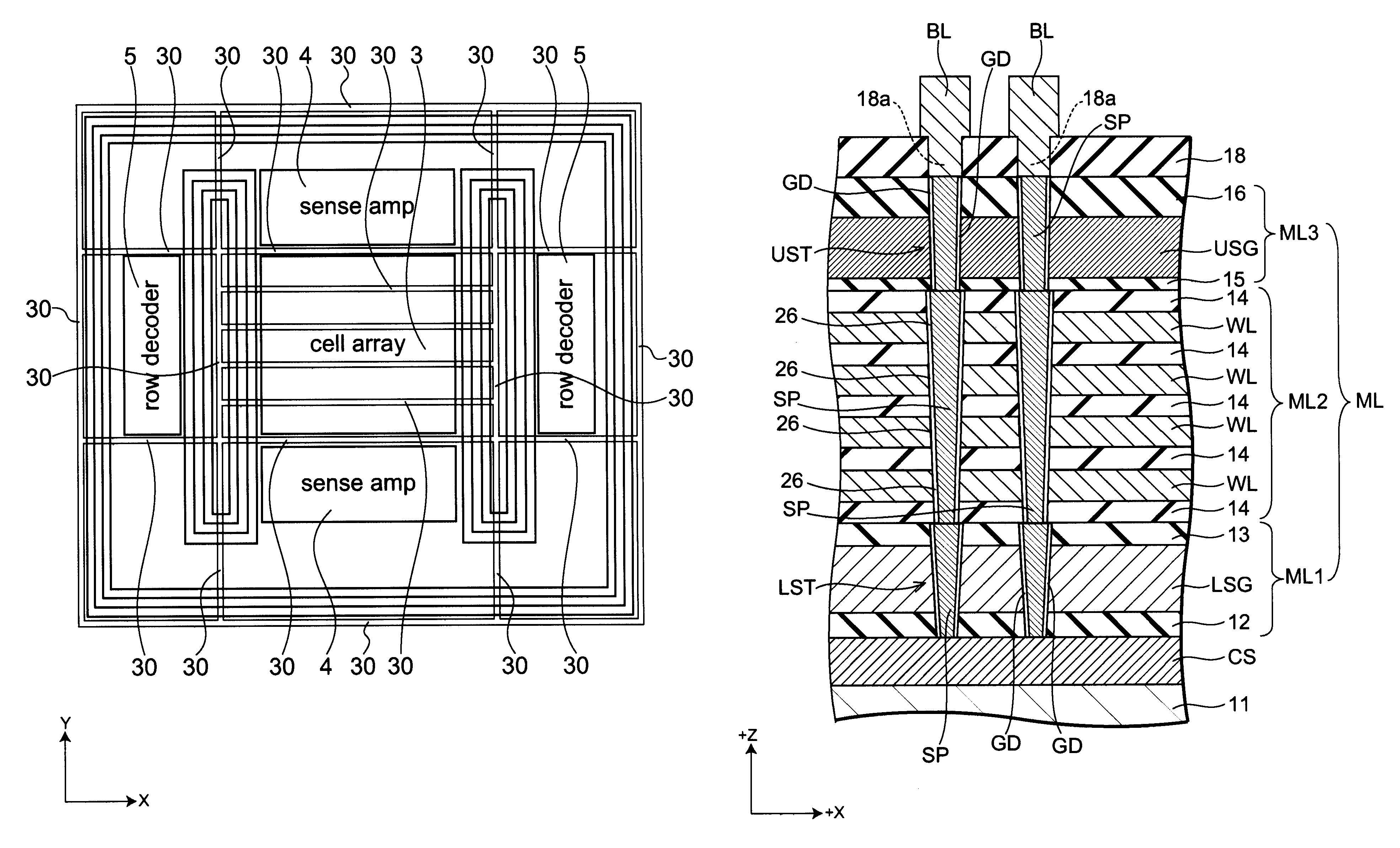

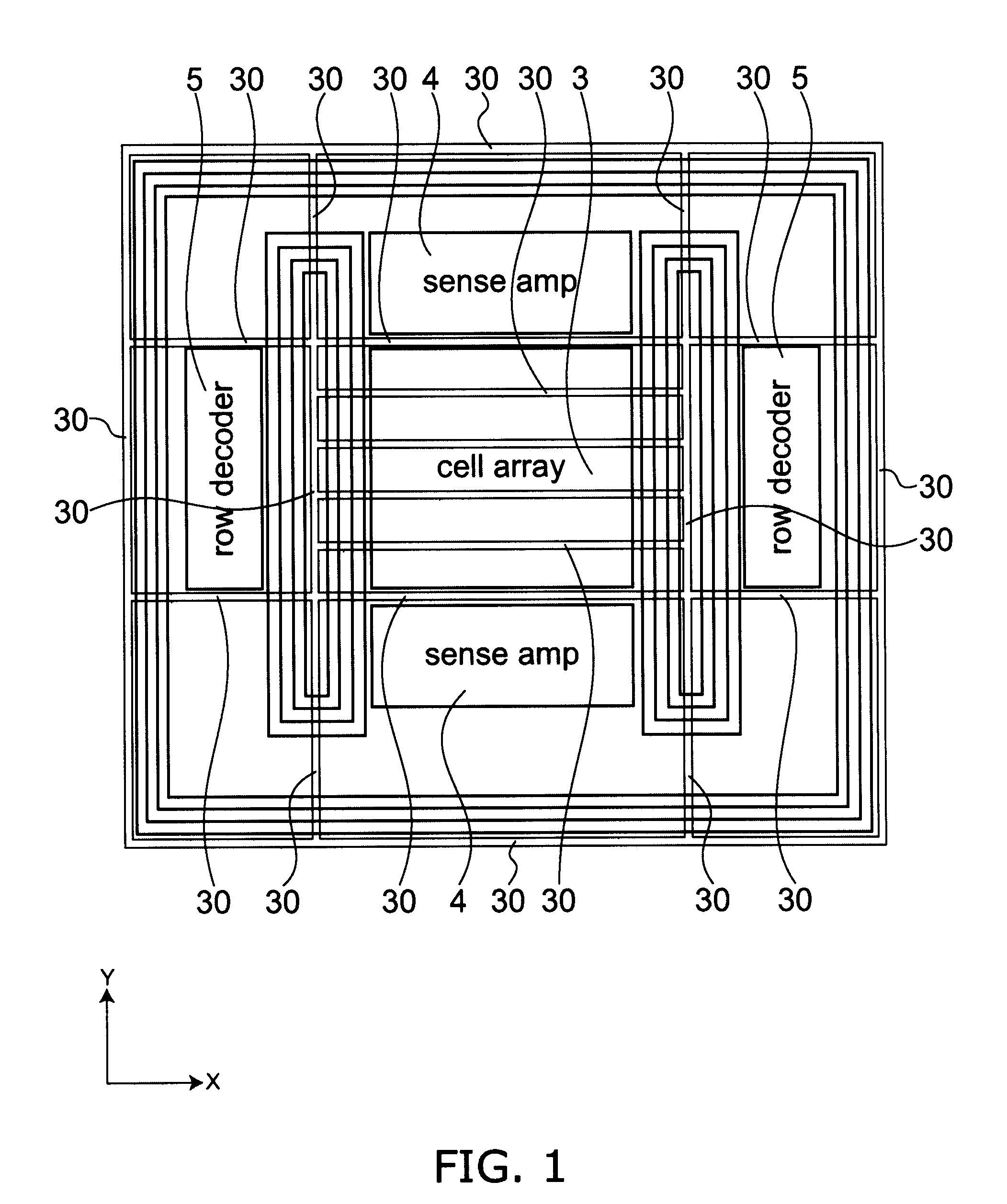

[0024]FIG. 1 is a schematic view illustrating the planar layout of major components in a semiconductor memory device according to the embodiment of the invention.

[0025]FIG. 1 shows one chip region, which is broadly divided into a memory cell array region and a peripheral circuit region. The memory cell array region is formed at the center of the chip and includes memory cells 3. The peripheral circuit region is formed around the memory cell array region and includes a sense amplifier 4, row decoder 5, and other circuits.

[0026]A stacked body with a plurality of conductive layers and a plurality of dielectric layers alternately stacked, described later, is provided throughout the chip including the memory cell array region and the peripheral circuit region. The stacked body is divided by slits 30 into a plurality of blocks. An interlayer dielectric film is buried in the slit 30 as described later...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More