System for specifying addresses by creating a multi-bit ranked ordered anchor pattern and creating next address by shifting in the direction of the superior position

a technology of anchor pattern and anchor pattern, which is applied in the direction of memory address/allocation/relocation, testing/monitoring control system, instruments, etc., can solve the problems of prone to both software and signaling errors, human error in initial configuration of the system, etc., and achieves high compatibility, simple and inexpensive implementation, and high reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

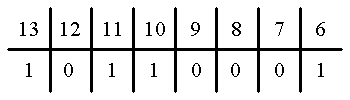

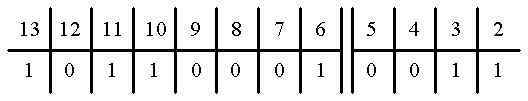

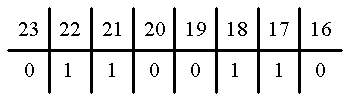

Turning now to the drawings, FIG. 1 is a schematic diagram illustrating the invention as implemented in conjunction with a Small Computer Systems Interface (SCSI) bus system. The SCSI bus standards are defined in ANSI document X3.131, the disclosure of which is hereby incorporated by reference. As seen in this figure, a SCSI bus generally designated with reference numeral 10 has a conventional terminator 12 coupled to each end thereof, and a plurality of computer devices coupled together in a serial or daisy-chain configuration. The first such device is an initiator 14, typically a computer. The remaining seven devices are target devices, usually storage devices (such as disc drives or tape drives) 15-21.

The SCSI bus 10 is supplemented by a multi-bit address bus generally designated with reference numeral 25 which conveys physical device addresses. Bus 25 is coupled to a host device (not illustrated) which generates a multi-bit character termed an anchor pattern, which is applied to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More