Semiconductor wafer having a bottom surface protective coating

a technology of silicon wafers and protective coatings, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of large loss of devices, chipping along the dicing edges of individual ic devices, and the number of lost ic devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]Methods and apparatus for protecting IC devices of a wafer during and after a dicing operation are described below. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be understood, however, to one skilled in the art, that the present invention may be practiced without some or all of these specific details. In other instances, well known process operations have not been described in detail in order not to unnecessarily obscure the present invention.

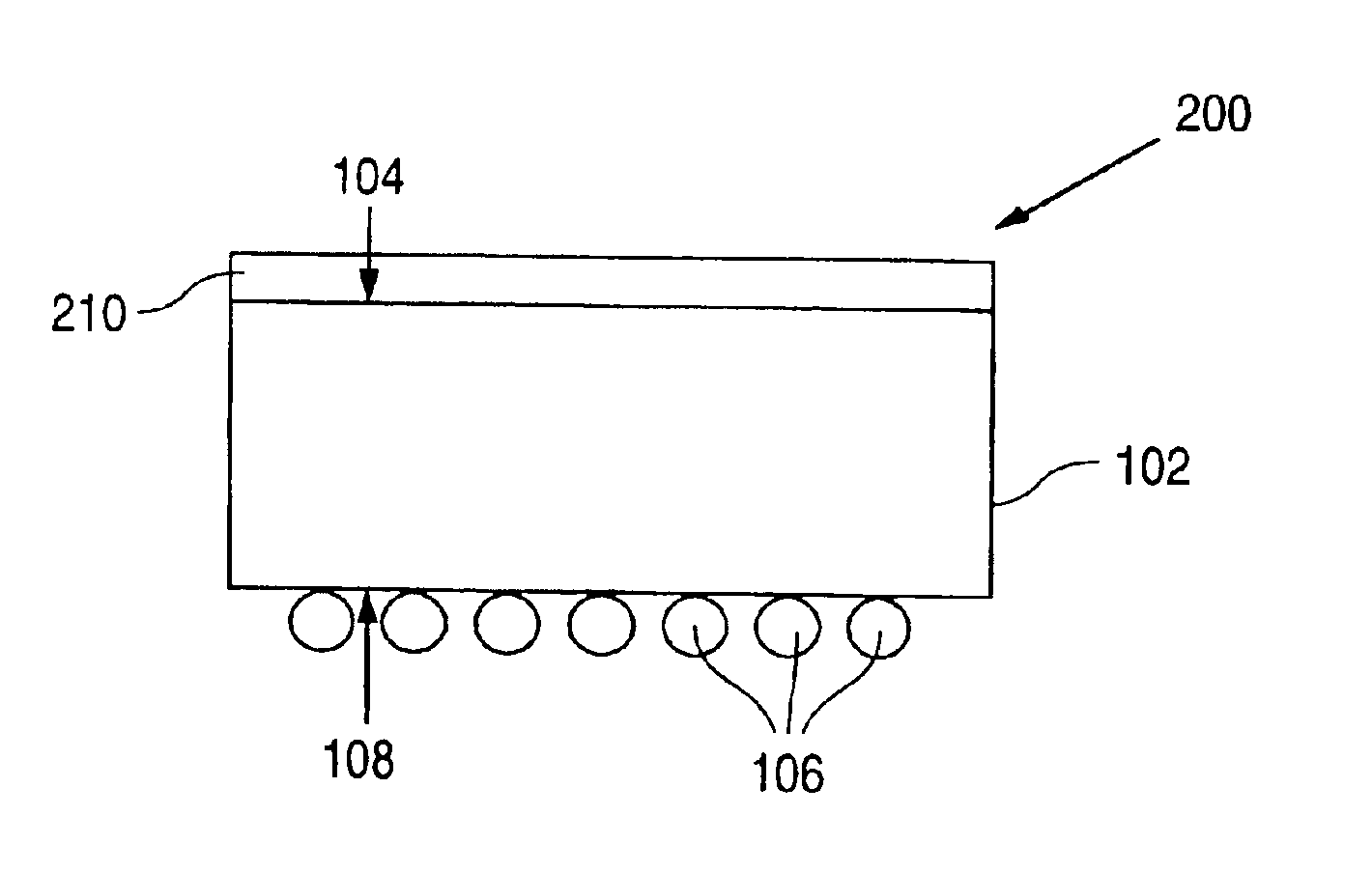

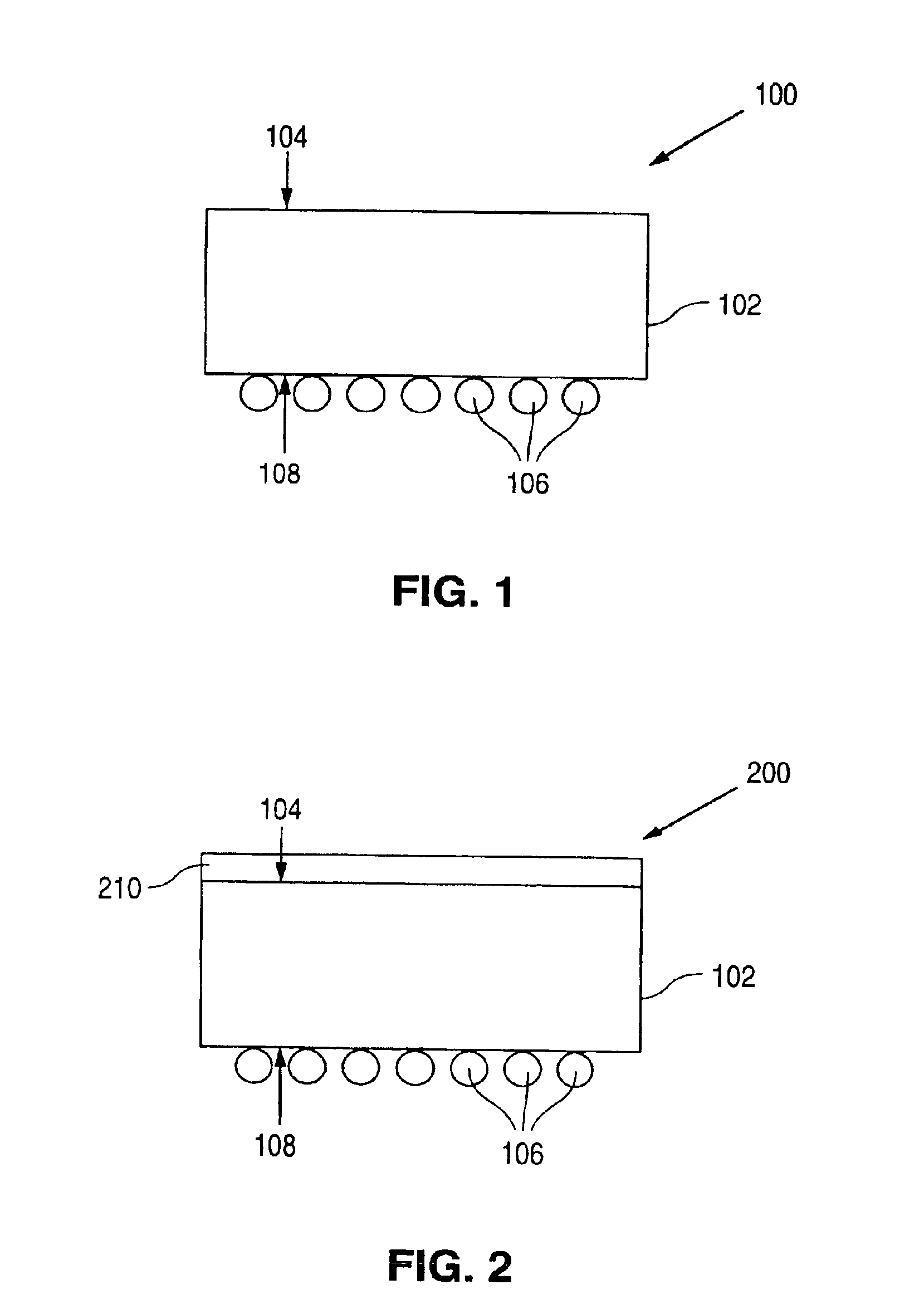

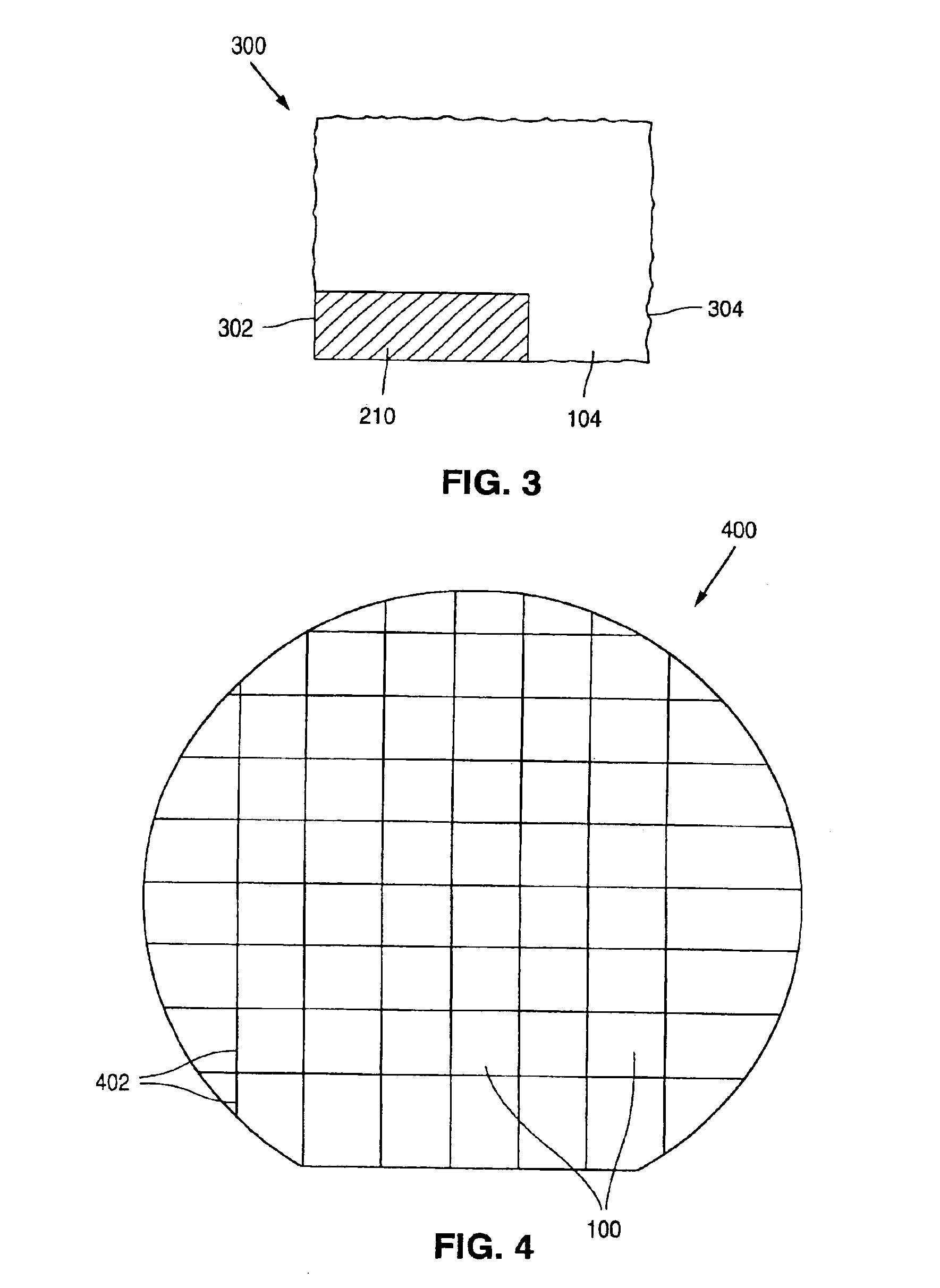

[0020]In general, the present invention includes a wafer having a protective film for substantially preventing damage to the dies of the wafer during and after the dicing process. For example, the protective film substantially prevents chipping along the dicing edges of the dies. Although the following description is in reference to flip chip devices, of course, it should be well understood to those skilled in the art that the present i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More