Leadframe semiconductor integrated circuit device using the same, and method of and process for fabricating the two

a semiconductor integrated circuit and leadframe technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve problems such as difficult to prevent effective package body cracking, wire bonding defect, and considerable restriction on the size of the chip to be mounted on the die pad. , to achieve the effect of suppressing package body cracking and widening the size rang

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

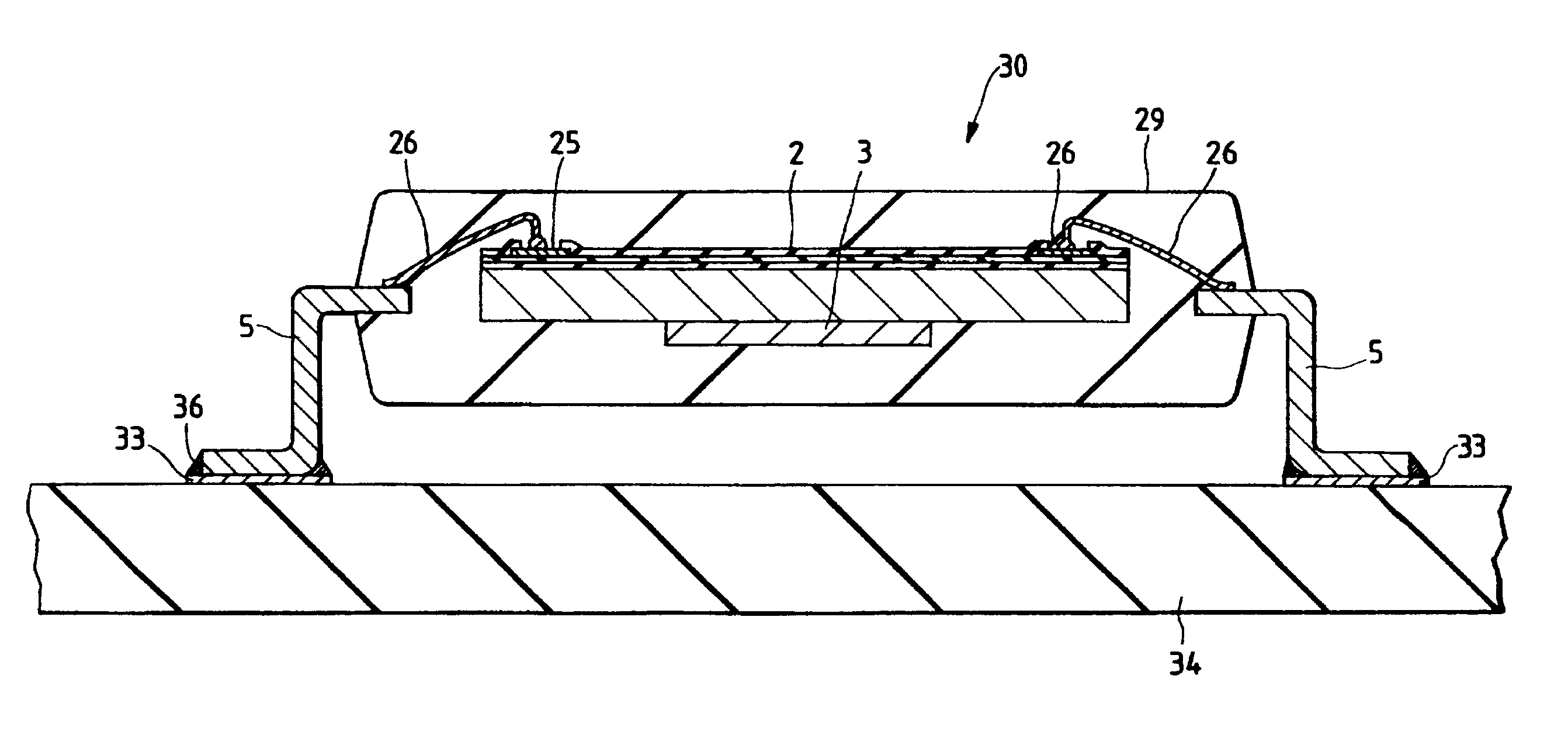

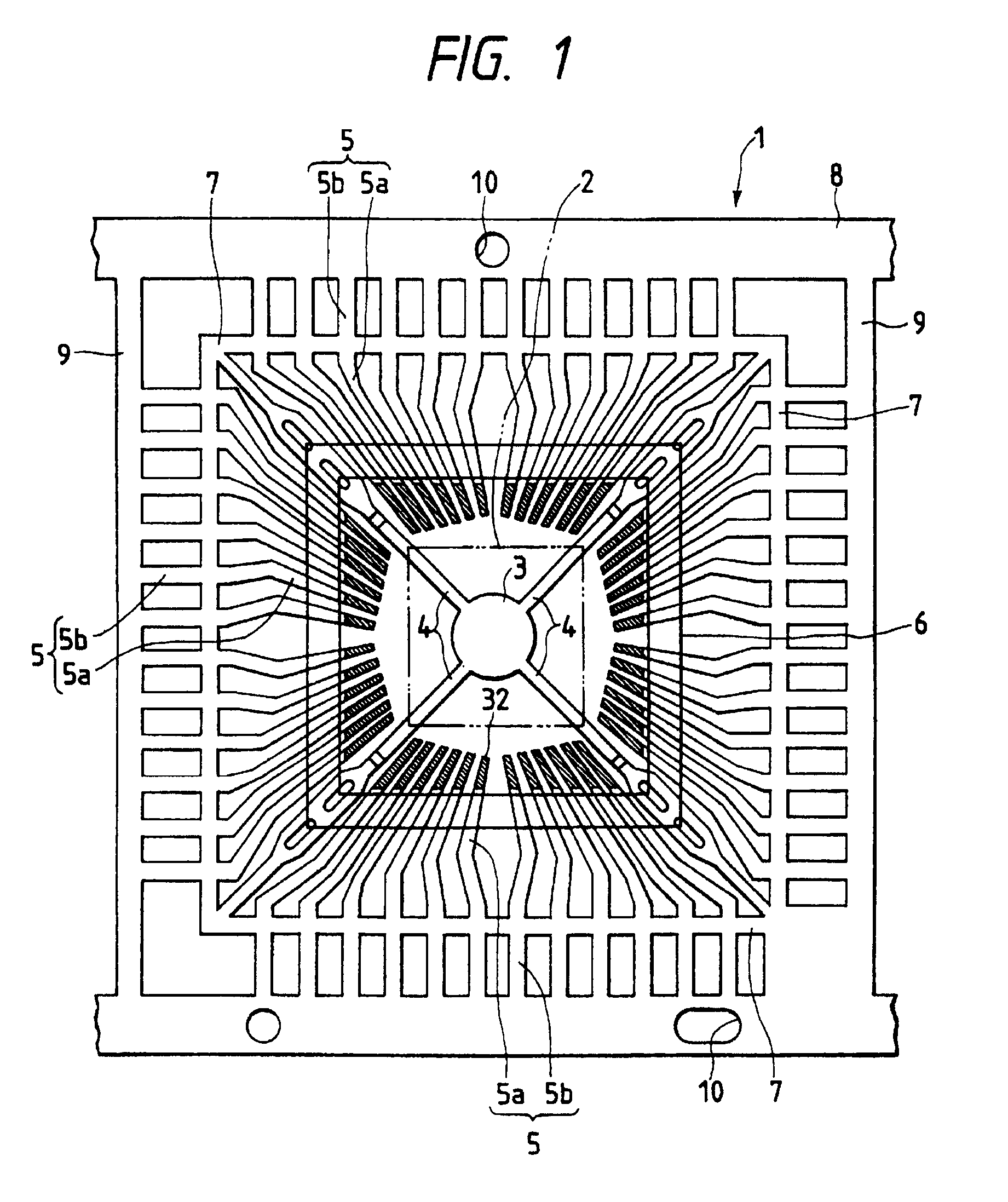

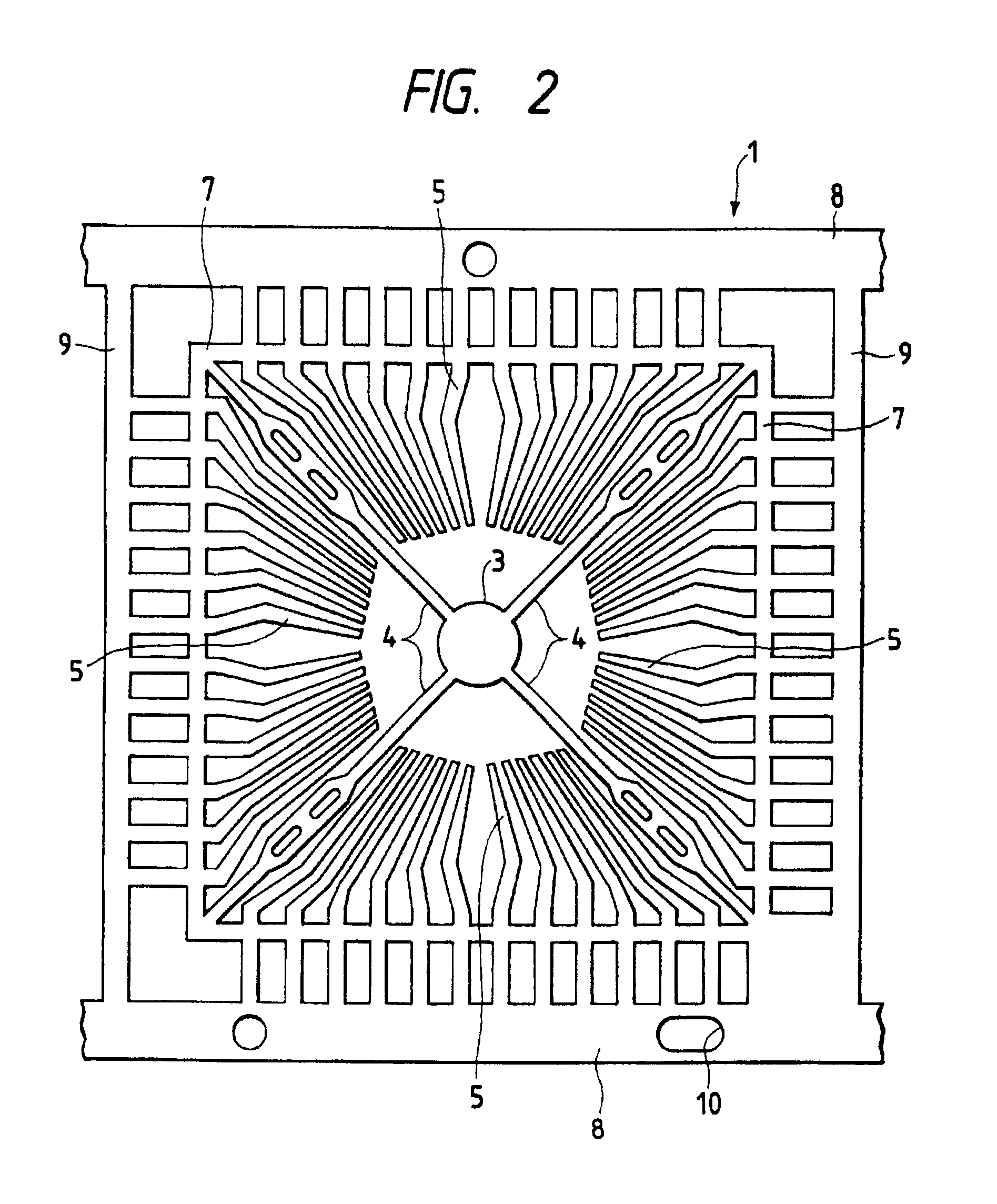

[0072]FIG. 1 is a top plan view showing a leadframe to be used for fabricating a QFP package according to one embodiment of the present invention.

[0073]A leadframe 1 is formed at its central portion with a circular die pad for mounting a semiconductor chip 2 which is formed with a semiconductor circuit and bonding pads on its principal face. The die pad 3 is supported by four suspension leads 4. The die pad 3 has its chip mounting face characterized to have a smaller area than that of the principal face of the semiconductor chip 2 mounted thereon.

[0074]The die pad 3 is arranged therearound with a plurality of leads 5. To the wider portions of the suspension leads 4 and the middle portions of the leads 5, there is adhered a quadrangular frame-shaped tape 6 which is made of an insulating, thin synthetic resin film. Outside of the tape 6, there is formed a dam bar 7 for supporting the leads 5 and preventing the resin from overflowing at a molding time. The dam bar 7 is formed into a fr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Volume | aaaaa | aaaaa |

| Volume | aaaaa | aaaaa |

| Volume | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More