Barrier for capacitor over plug structures

A technology of capacitors and barrier layers, applied in capacitors, electric solid devices, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

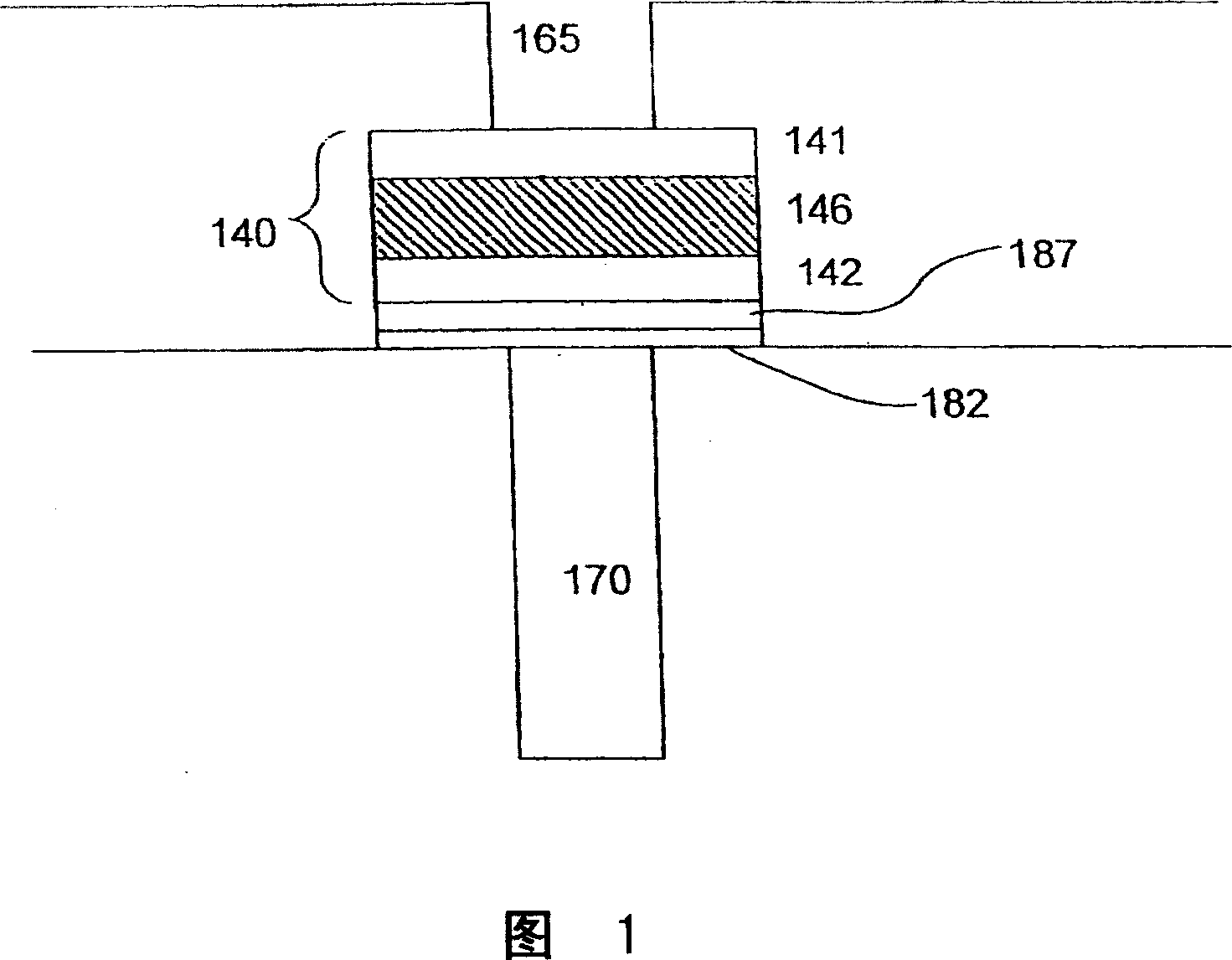

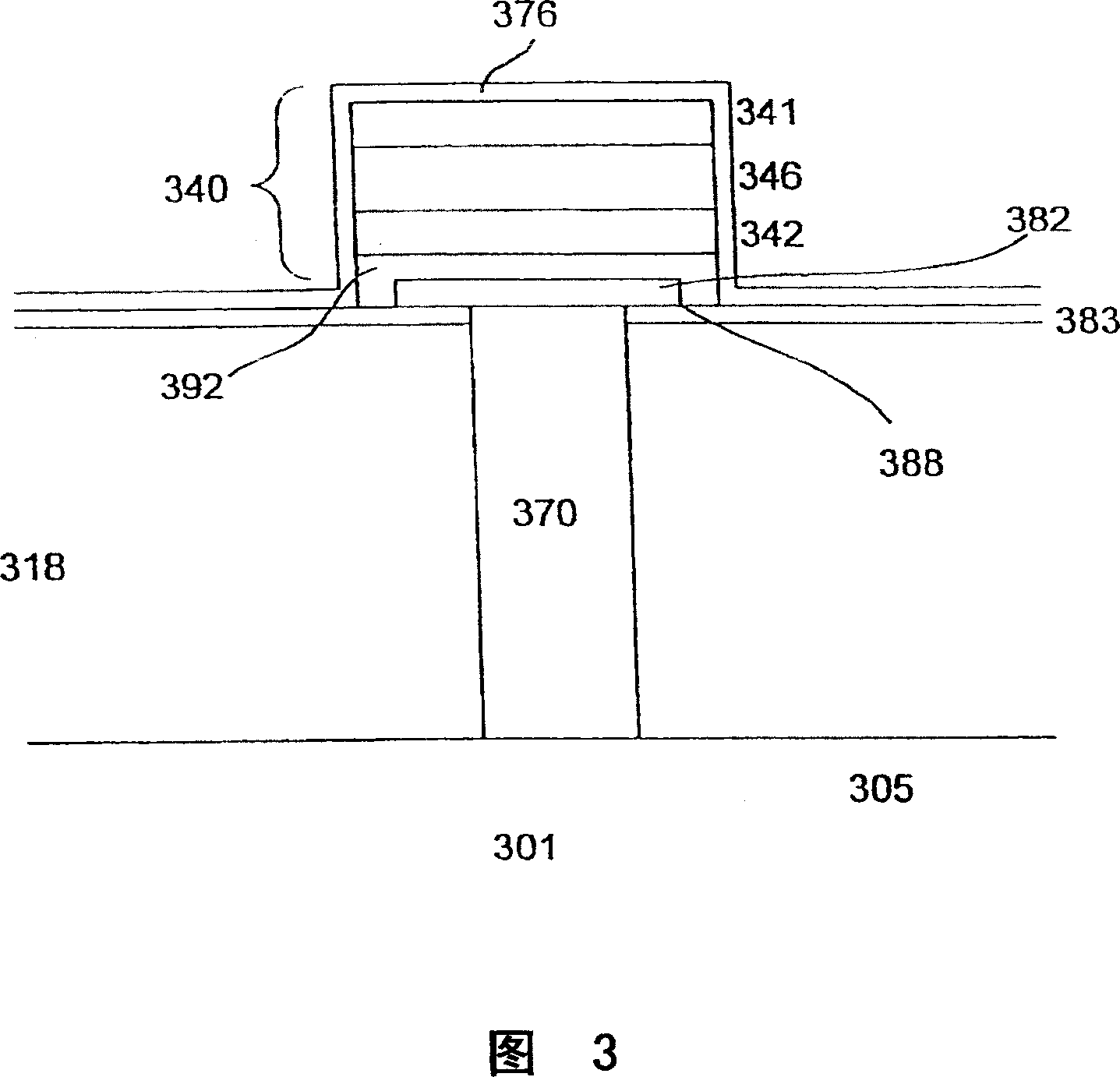

[0013] The present invention relates to improved barriers for reducing the diffusion of atoms and molecules such as oxygen. The barrier is particularly useful for capacitors in plug structures of memory cells. In one embodiment, the barrier is applied to a ferroelectric capacitor. This barrier can also be used for other types of capacitors such as high-k dielectric capacitors.

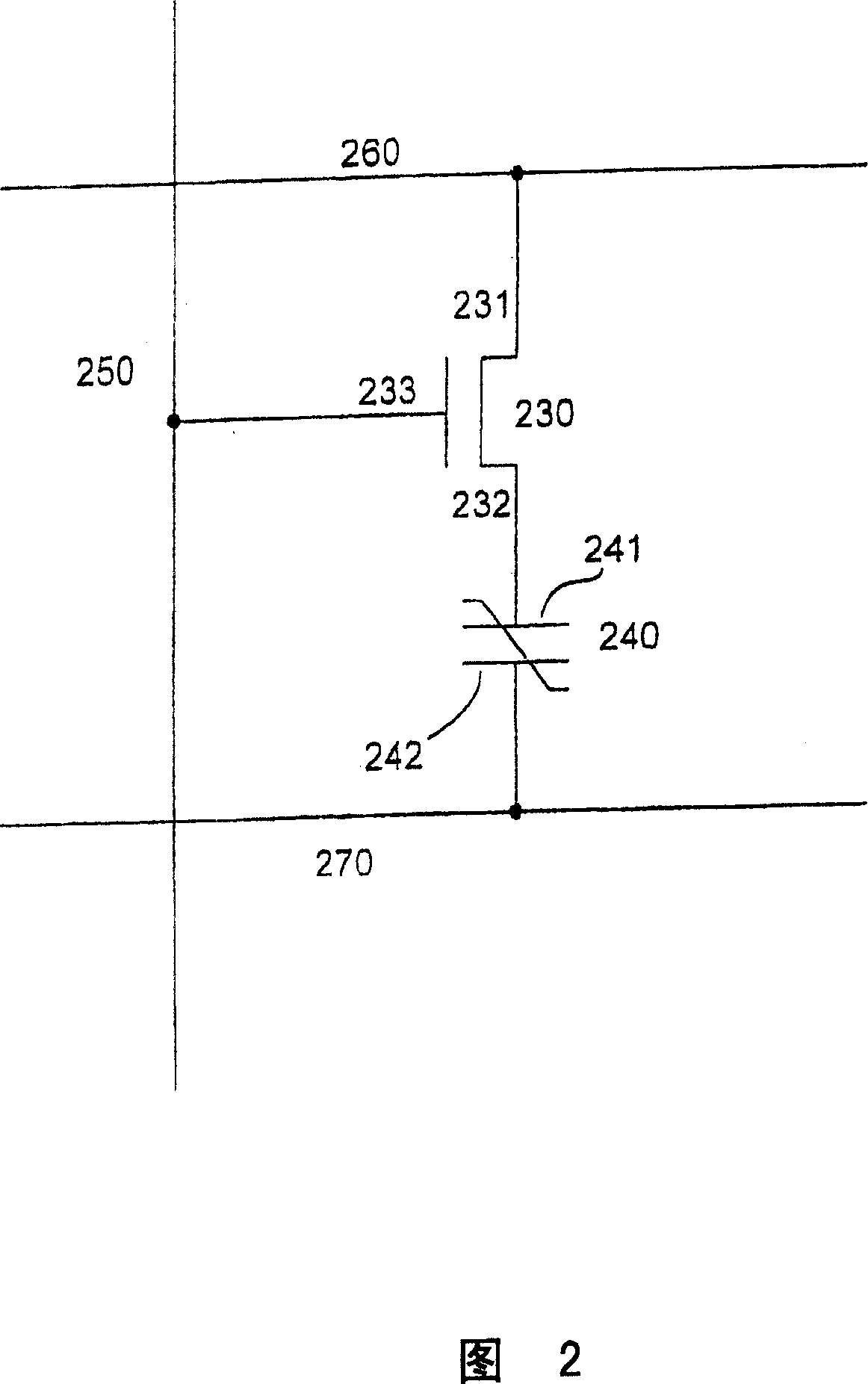

[0014] FIG. 2 shows a ferroelectric memory cell 201 having a transistor 230 and a capacitor 240 . The second terminal 232 of the transistor is coupled to the first electrode 241 of the capacitor. The gate 233 and the first terminal 231 of the transistor are coupled to the word line 250 and the bit line 260, respectively. Coupled to the second electrode 242 of the capacitor is a plate line 270 . Capacitors use the hysteresis polarization property of ferroelectrics to store information. The logic value stored in the memory cell depends on the polarization of the capacitor. To change polarity, a vol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More