Method for making metal-oxide-semiconductor transistor

A transistor area, MOS transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effect of improving the carrier drift rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

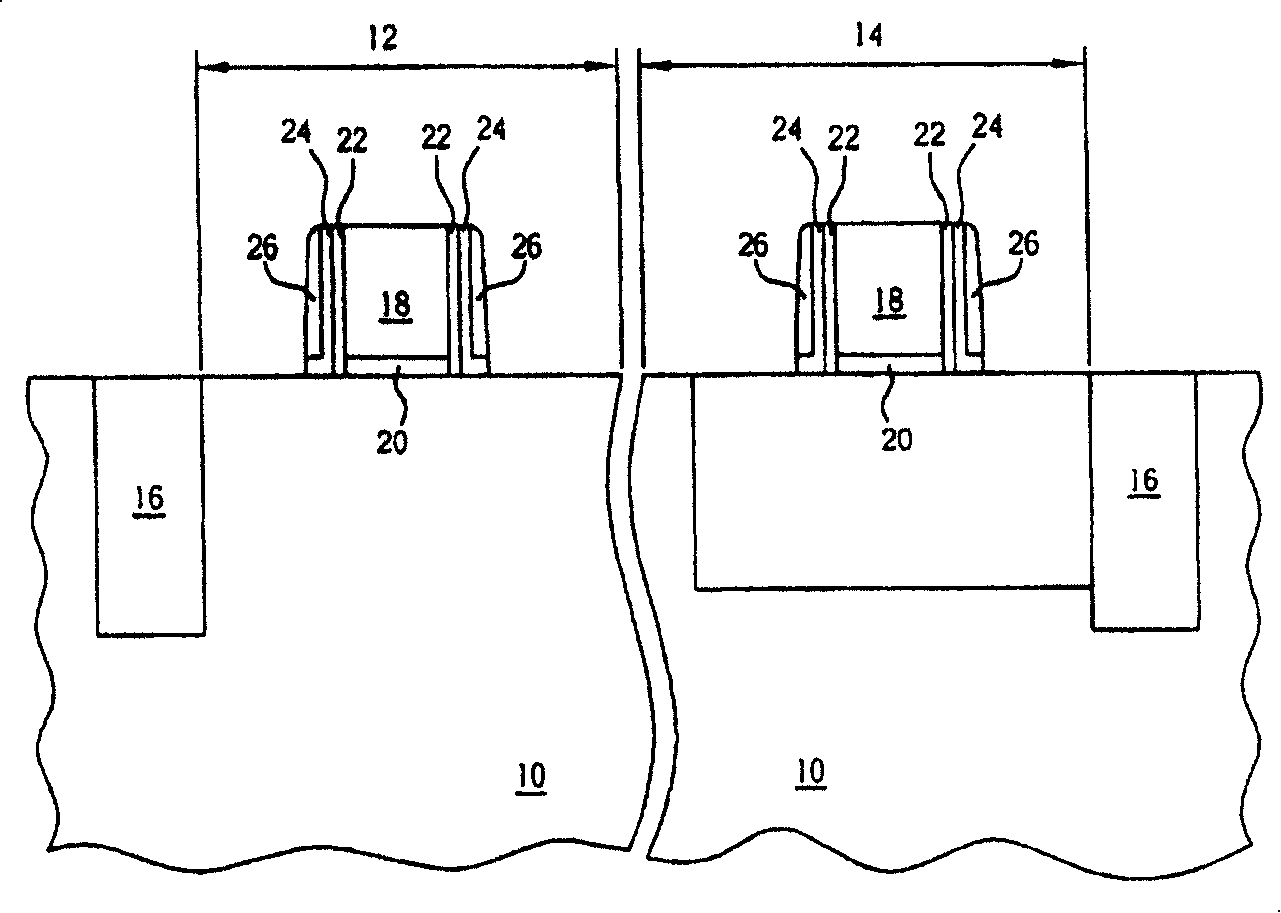

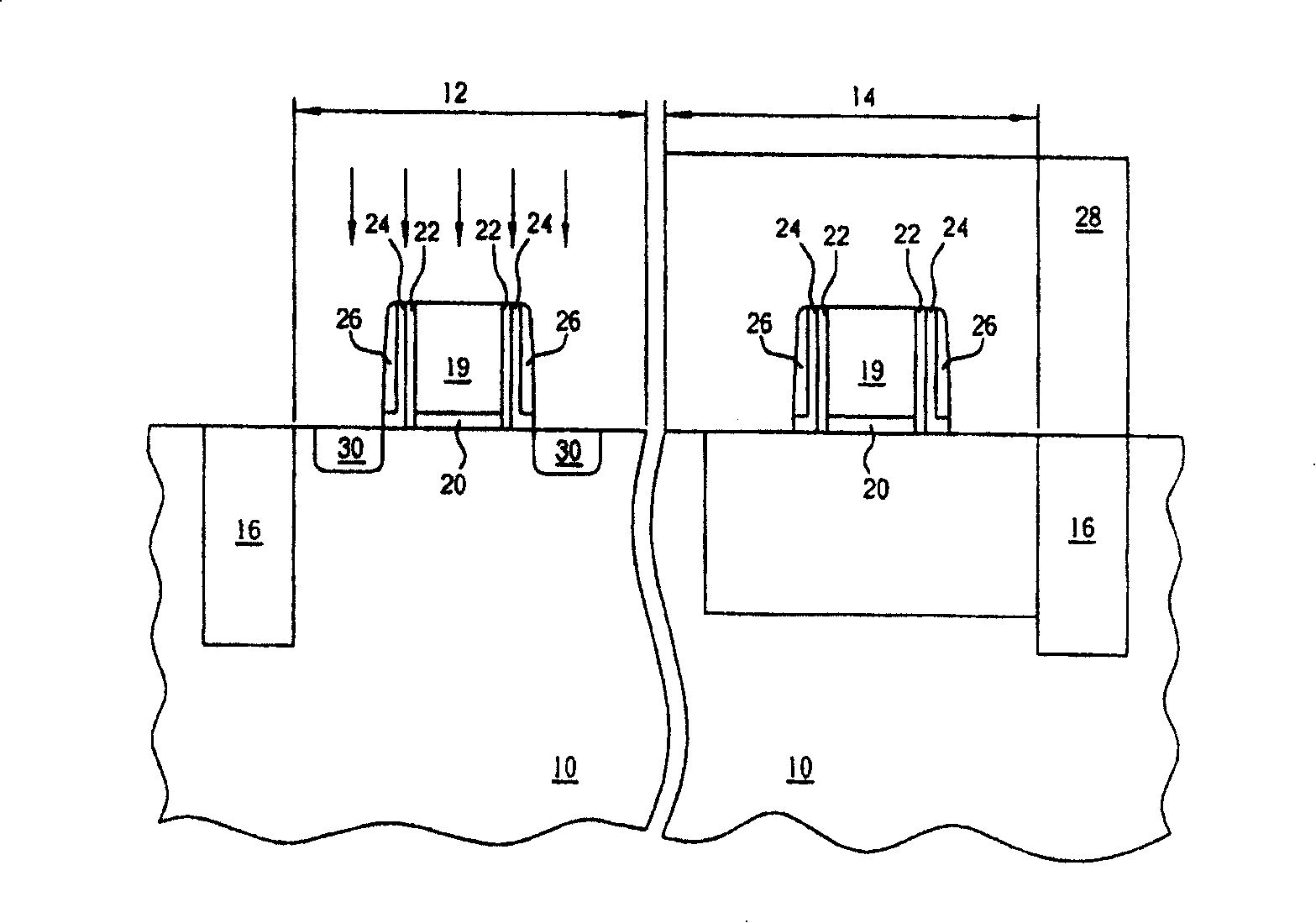

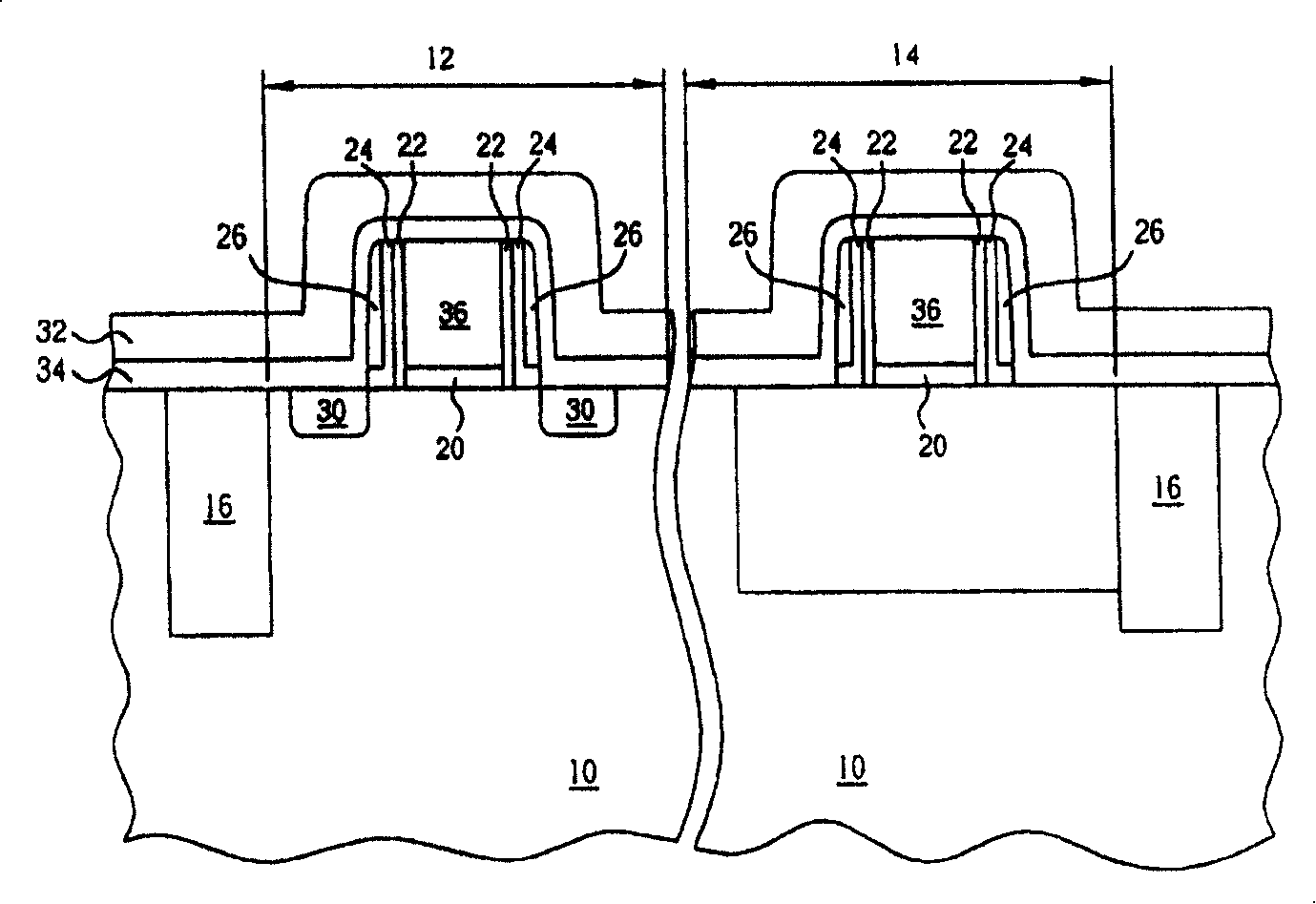

[0029] Please refer to Figure 1 to Figure 5 , Figure 1 to Figure 5 It is a schematic diagram of a method for making a MOS transistor in the first preferred embodiment of the present invention, wherein in order to highlight the characteristics of the present invention and simplify the description, Figure 1 to Figure 5 Only one NMOS transistor region and one PMOS transistor region are shown. Such as figure 1 As shown, a substrate 10, such as a silicon substrate, is provided first. The substrate 10 includes a plurality of NMOS transistor regions 12 and a plurality of PMOS transistor regions 14 separated by shallow trenches 16 . In addition, the substrate 10 further includes a plurality of polysilicon gate structures 18 respectively disposed in each NMOS transistor region 12 and each PMOS transistor region 14 , and a gate insulating layer 20 is further included between each polysilicon gate structure 18 and the substrate 10 . Next, a liner layer 22 , a dielectric layer 24 and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More