CMOS image sensor and fabricating method thereof

A technology of image sensor and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., and can solve problems such as inability to provide voltage and device performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

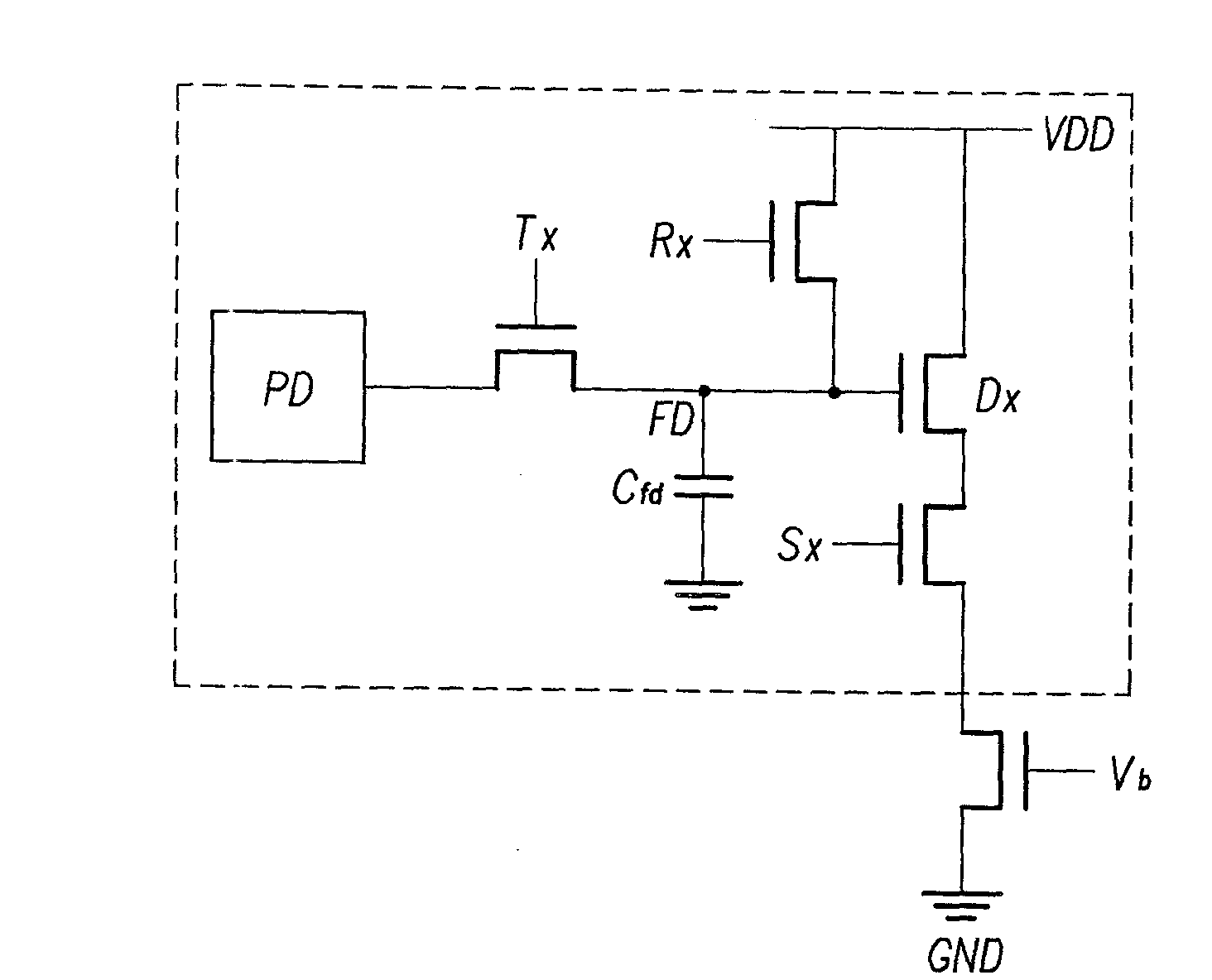

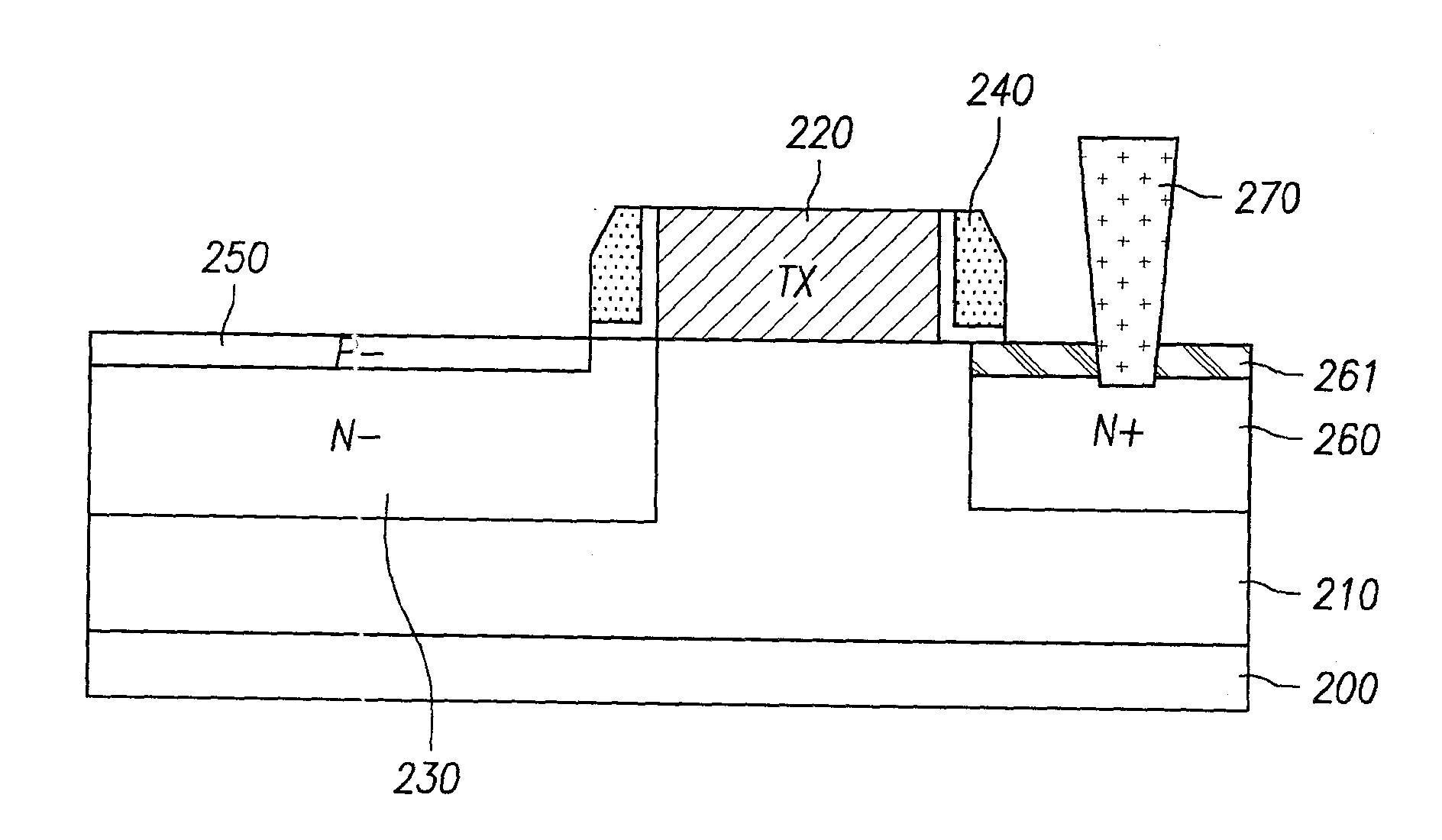

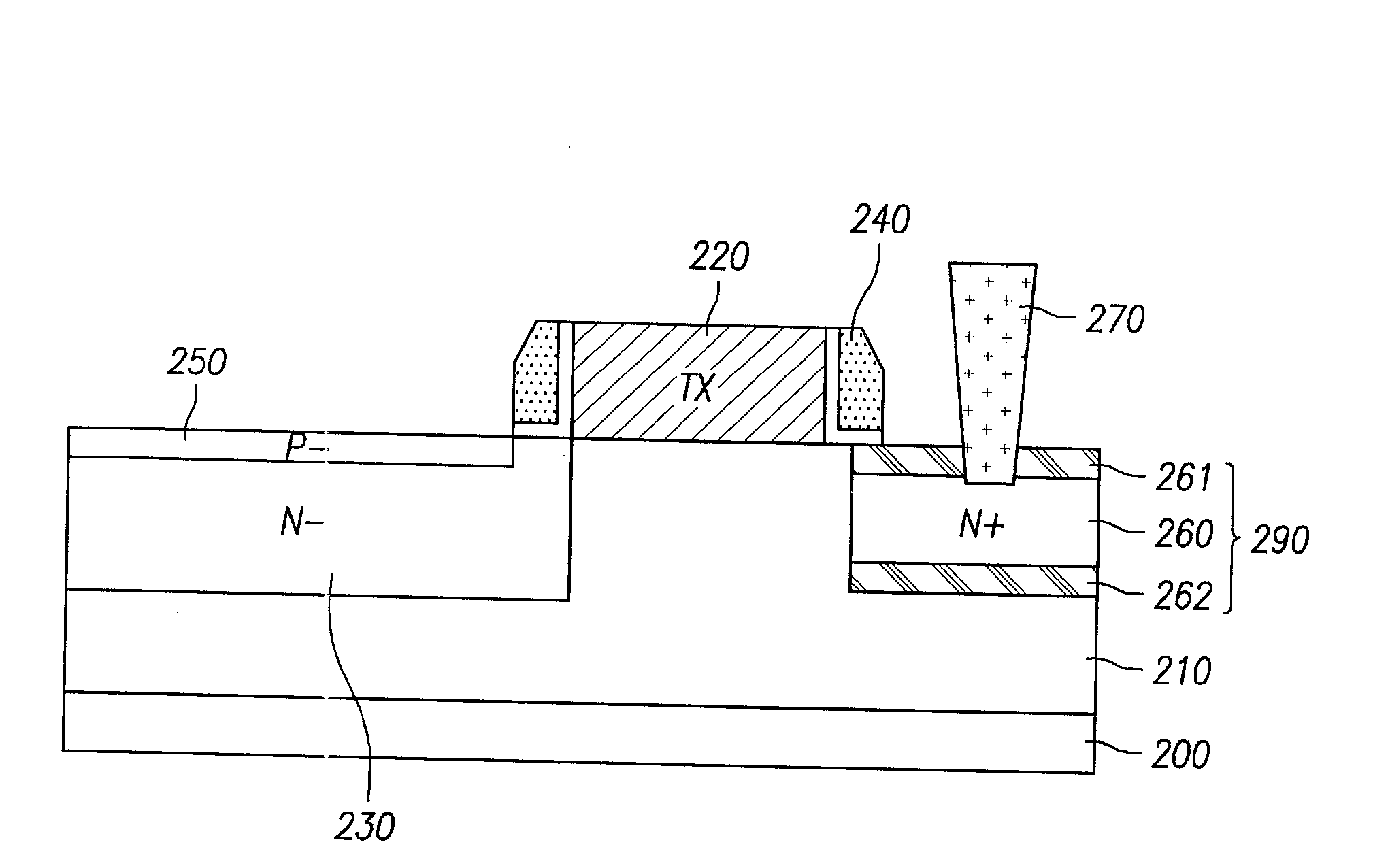

[0012] example Figure 2a with 2b Schematically shows the transfer transistor T x the gate, photodiode region, and floating diffusion region. In particular, a reset transistor (R x ), drive transistor (D x ) and select transistor (S x ).

[0013] Refer to example Figure 2a , the lightly doped p- epitaxial layer 210 is grown on the heavily doped p+ substrate 200 . A device isolation layer for inter-unit-pixel isolation may be formed at a designated portion of the p-epitaxial layer 210 by local oxidation of silicon (LOCOS) or shallow trench isolation (STI). Subsequently, the transfer transistor (T x ) gate (hereinafter abbreviated as gate 220 ) is formed on the p- epitaxial layer 210 .

[0014] The deep n-diffusion layer 230 is formed by lightly implanting n-type impurities (n-) with high energy into the portion of the p- epitaxial layer 210 immediately adjacent to the gate 220 . When forming the n-diffusion layer 230, an n-very lightly doped drain (VLDD) region can b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More