Semiconductor assembly, seal ring structure and forming method thereof

A technology of guide holes and metal wires, which is applied in the field of semiconductor integrated circuits, can solve problems such as short circuits and loss of function of aluminum pads 140, and achieve the effects of avoiding stress damage and improving the pass rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

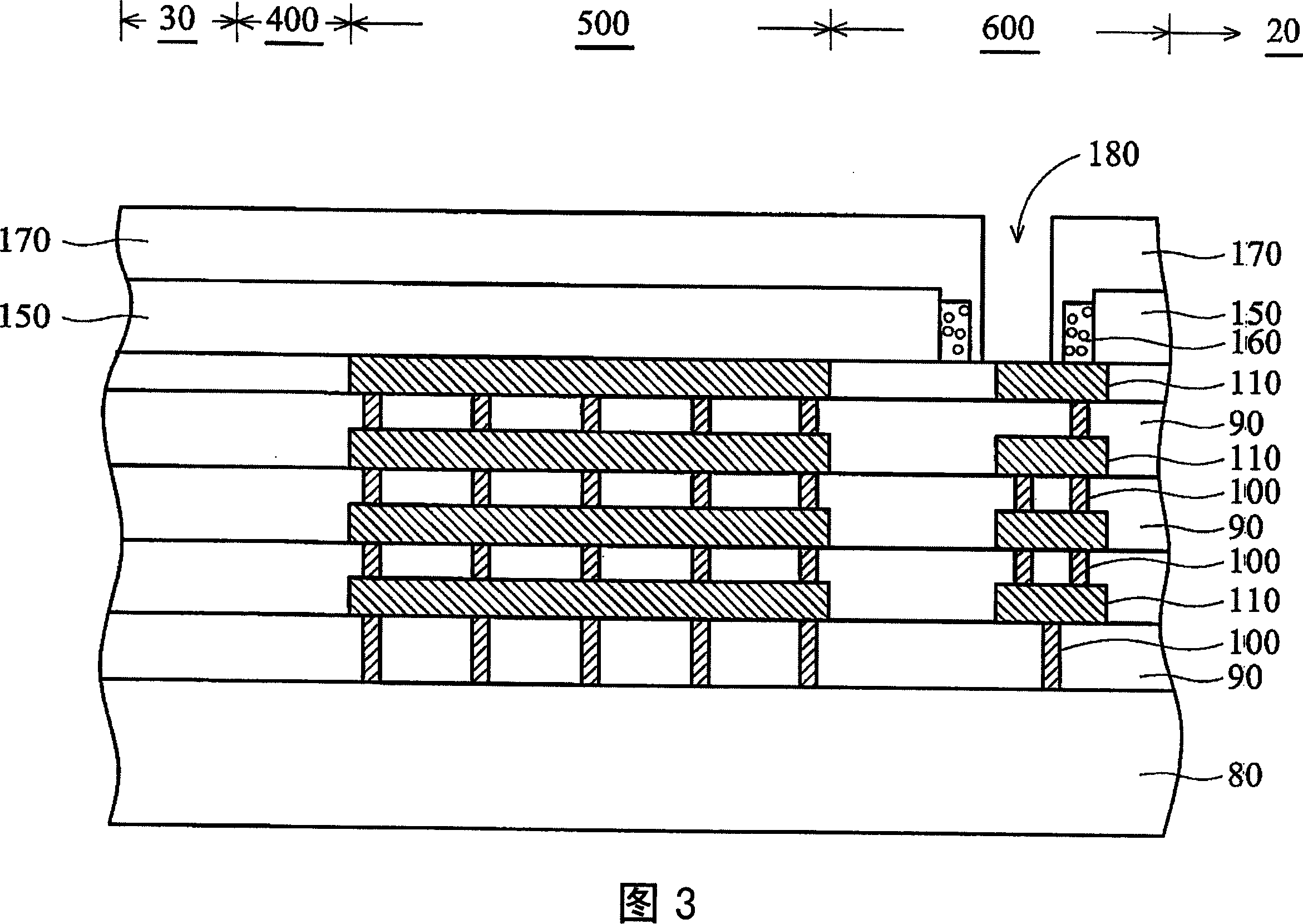

[0033] As shown in FIG. 3 , it is a cross-sectional view of the sealing ring structure of the embodiment of the present invention. As shown, the integrated circuit 30 is formed on a silicon substrate 80 . The silicon substrate 80 may have components, junctions, or other components (not shown). For example, a field oxide layer (as shown) can be formed between the sealing ring structure (the first sealing ring 600 , the second sealing ring 500 , and the isolation region 400 ) and the integrated circuit 30 . The second sealing ring 500 has metal layers 110 and dielectric layers 90 stacked alternately, and the two are electrically connected by via plugs 100 . A preferred dielectric layer can be a material with a low dielectric constant (dielectric constant less than 3.9), and the formation method can be a known deposition process such as chemical vapor deposition (hereinafter referred to as CVD). In the present invention, the function of the guide hole plug is to reduce the stre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More