A sonos memory device with optimized shallow trench isolation

A technology of shallow trenches and devices, which is applied in the manufacture of electric solid devices, semiconductor devices, semiconductor/solid devices, etc., can solve problems affecting the electronic characteristics of SONOS units, and achieve the effect of reducing thickness changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] For the purpose of illustrating the invention, preferred embodiments of the methods and devices of the invention are described below. It will be appreciated by those skilled in the art that other alternative and equivalent embodiments of the invention can be conceived and put into practice without departing from the scope of the invention, which is only defined by the appended claims.

[0038] Objects denoted by the same reference numerals refer to the same objects shown in the preceding figures.

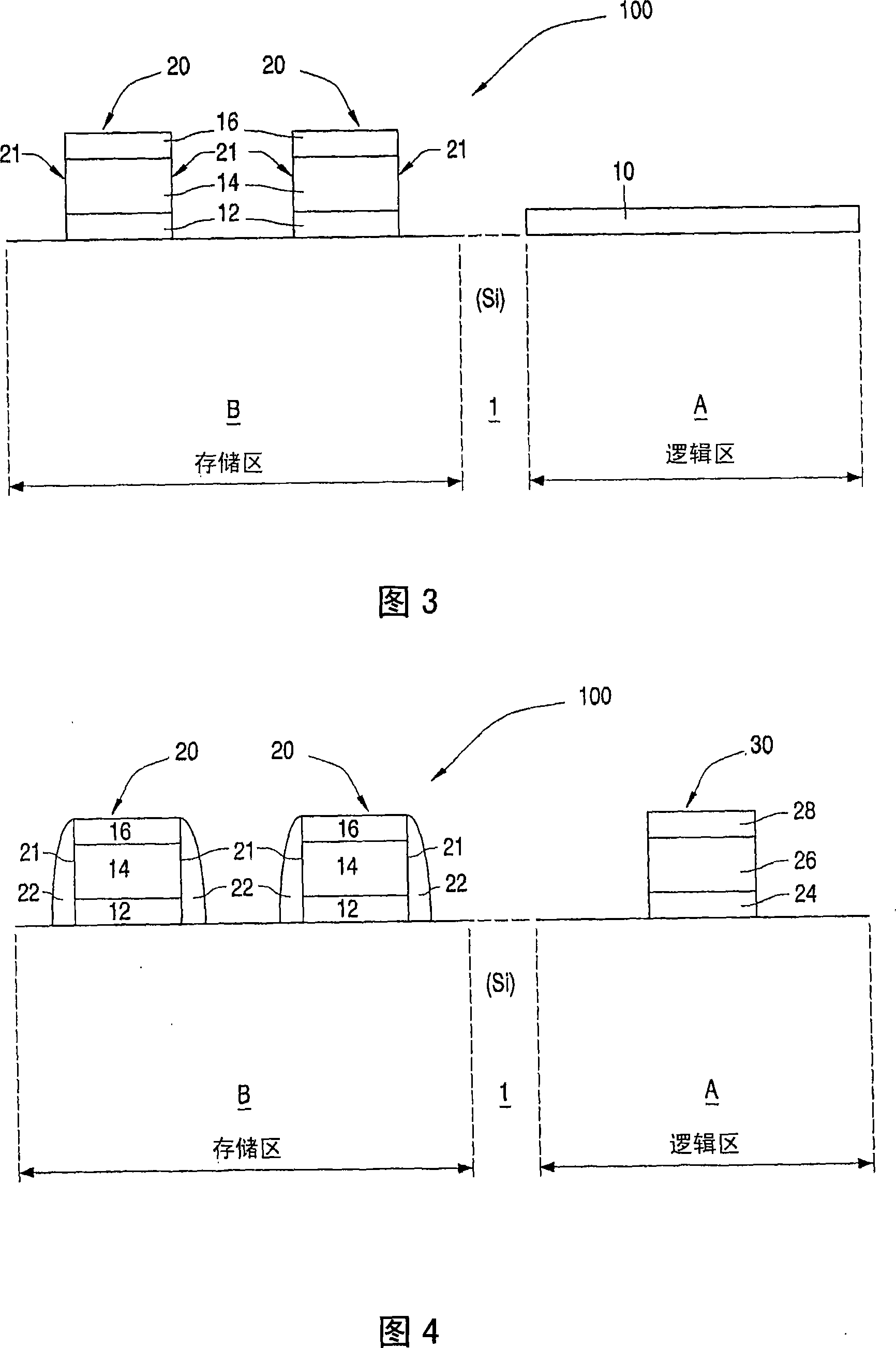

[0039] Figure 3 diagrammatically shows a cross-sectional view of a microelectronic device comprising a SONOS memory cell according to the invention at a first moment during manufacture.

[0040] A microelectronic device 100 comprising a logic area A and a memory area B is produced on a semiconductor substrate 1 .

[0041] The logic area A includes device components constituting a logic circuit, and the memory area B includes device components such as the SONOS memory cell 20...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com