Checking matrix forming device and communication device

A check matrix and generation device technology, applied in check code calculation, encoding, error detection encoding, etc., can solve the problems of wide distance, insufficient performance of error correction ability, etc., and achieve the effect of easy characteristics and good error correction ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

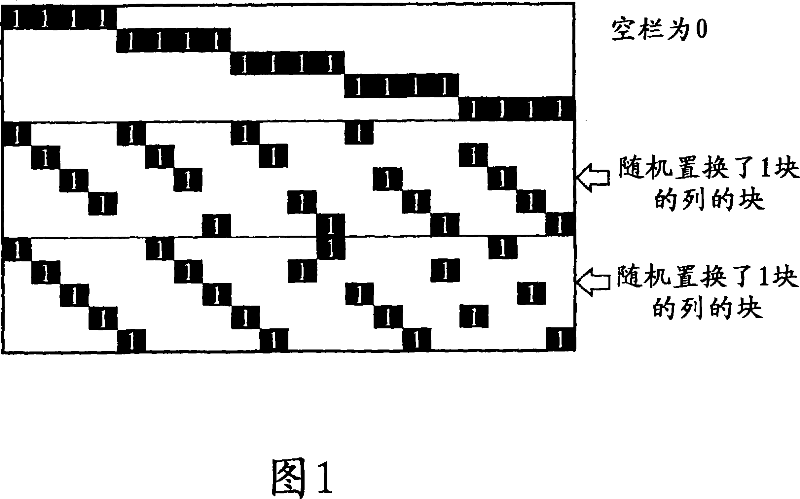

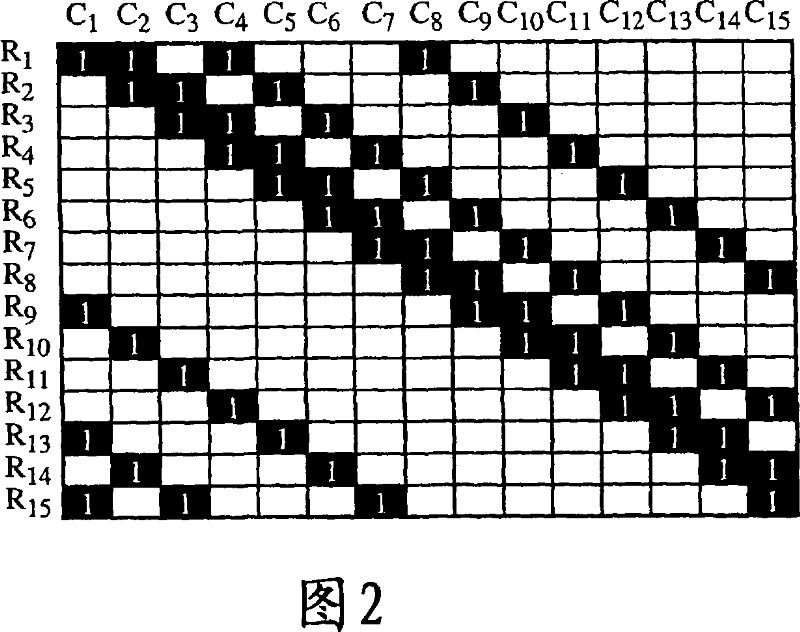

[0060] First, before describing the parity check matrix generation method for LDPC codes according to Embodiment 1, the positioning of encoders and decoders using the generated parity check matrixes for LDPC codes and existing methods for "irregular LDPC codes" will be described. check matrix generation method.

[0061] Fig. 4 is a structural block diagram of an LDPC encoding / decoding system. In FIG. 4 , the communication device on the transmitting side has a configuration including an encoder 101 and a modulator 102 , and the communication device on the receiving side has a configuration including a demodulator 104 and a decoder 105 . Here, the flow of encoding and decoding when using the check matrix for the generated LDPC code will be described.

[0062] A parity check matrix H generated by a parity check matrix generation device for LDPC codes is used in the communication device on the transmitting side, as will be described later. Then, in the encoder 101, the generator...

Embodiment approach 2

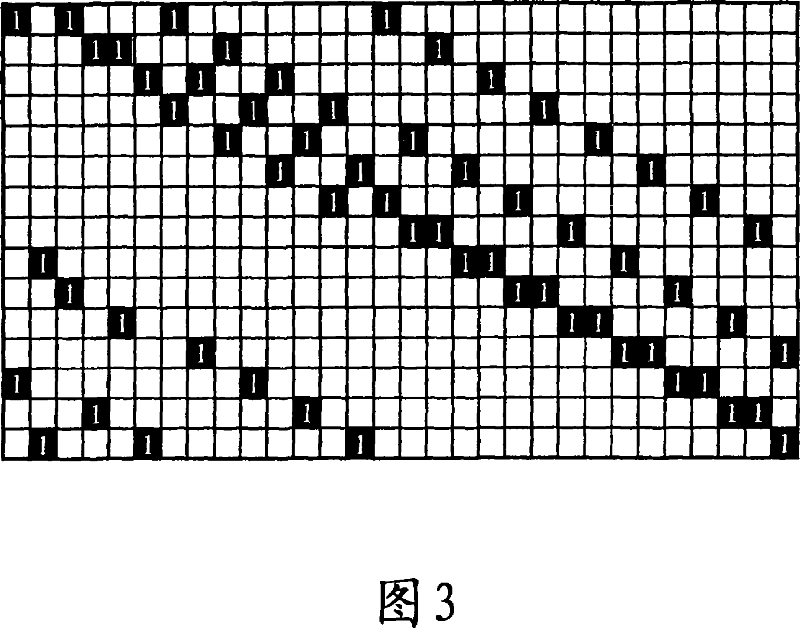

[0275] In the following, we will explain the check matrix generation method of the RC (Rate comapatible (rate compatible))-LDPC code with interchangeability in multiple coding rates (without changing the information length and only changing the coding rate) in the extended embodiment 1. .

[0276] Fig. 7 is a configuration diagram showing a parity check matrix generation device for an LDPC code according to Embodiment 2 of the present invention. This parity check matrix generating device is provided with information length, encoding rate, column maximum order input unit 21, parameter calculation unit 22 for pseudo-random number permutation matrix, pseudo-random number permutation matrix generation unit 23, and parameter calculation unit for order distribution optimization. 24. A frequency distribution optimization unit 25 and a parity check matrix generation unit 26. The parity check matrix generating device may be installed in the communication devices of the transmitting si...

Embodiment approach 3

[0341] Fig. 10 is a block diagram showing the configuration of a parity check matrix generation device for LDPC codes according to Embodiment 3 of the present invention. This parity check matrix generating device is provided with information length, encoding rate, column maximum order input unit 31, parameter calculation unit 32 for pseudo-random number permutation matrix, pseudo-random number permutation matrix generation unit 33, and parameter calculation unit for order distribution optimization. 34. A frequency distribution optimization unit 35 and a check matrix generation unit 36. The parity check matrix generating device may be installed in the communication devices of the transmitting side and the receiving side in FIG. Outside the communication device on the receiving side, the generated parity check matrix is stored in memories (not shown) in the communication devices on the transmitting side and receiving side, and output to the encoder 101 and decoder 105 .

[03...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com