Nonvolatile semiconductor storage device and method for manufacturing the same

A non-volatile, storage device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, static memory, etc., can solve problems such as inability to suppress parasitic transistors, failure to form, etc., and achieve the effect of favorable charge retention characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

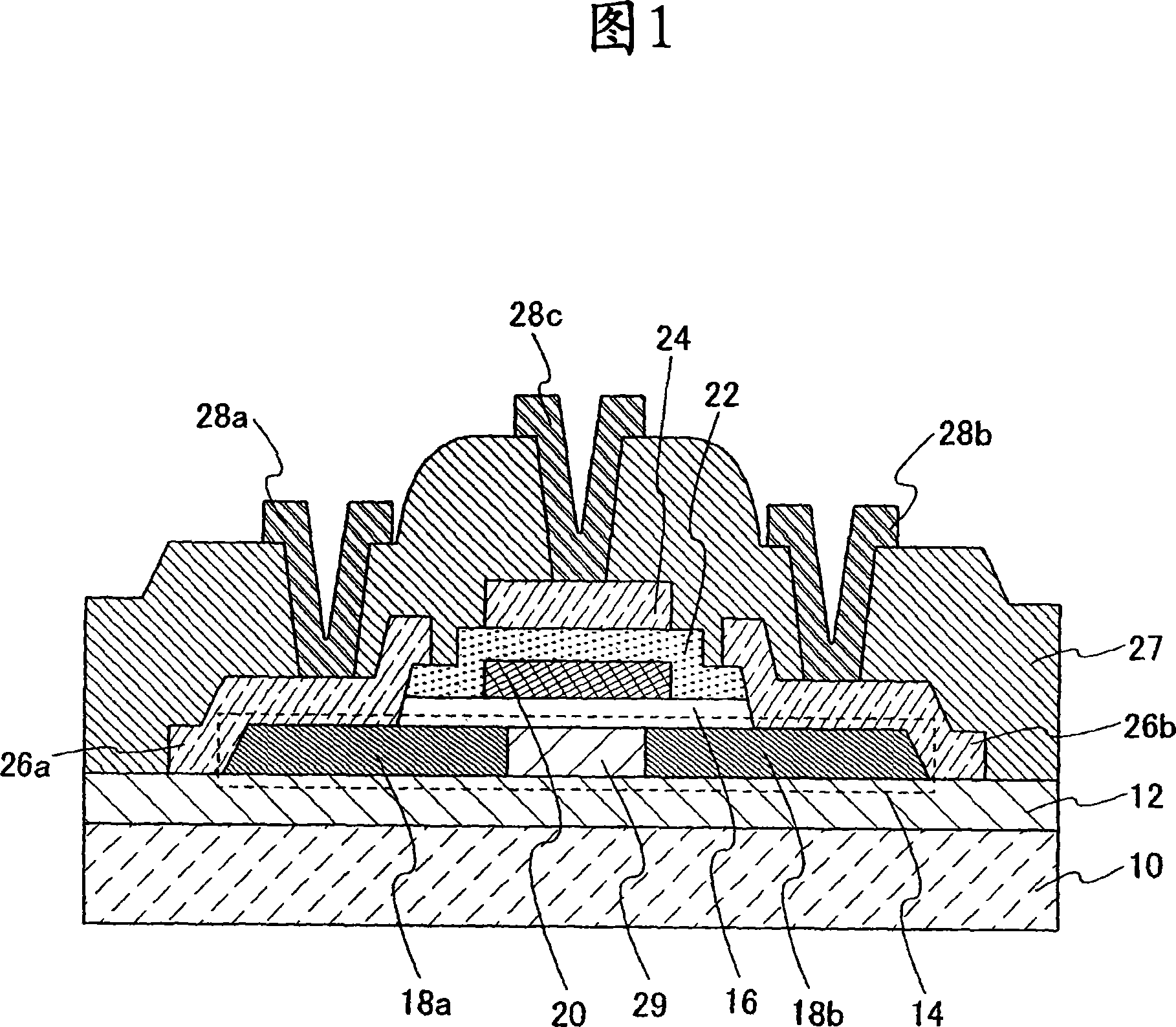

[0051] FIG. 1 is a sectional view illustrating the main structure of a nonvolatile semiconductor memory device related to the present invention. FIG. 1 illustrates, inter alia, the main part of the nonvolatile memory element.

[0052] In FIG. 1, reference numeral 10 denotes a substrate, 12 is a base insulating film, 14 is a semiconductor layer, 29 is a channel formation region, 18a and 18b are source regions or drain regions, and 16 is a first insulating film (also called tunnel insulating film), 20 is a floating gate electrode, 22 is a second insulating film (also known as a control insulating film), 24 is a control gate electrode, 26a and 26b are conductive layers, 28a and 28b are through conductive layers 26a and 26b A source or drain electrode electrically connected to the source or drain regions 18a and 18b, 28c is a gate wiring electrically connected to a control gate electrode, and 27 is an insulating film for passivation.

[0053] In the structure shown in FIG. 1 , ba...

Embodiment approach 2

[0106] In this embodiment mode, a method of manufacturing a nonvolatile memory element having a structure different from that of the nonvolatile memory element shown in FIG. 1 will be described. In this embodiment mode, a nonvolatile memory element as shown in FIG. 11 will be explained. In the nonvolatile memory element shown in FIG. 11 , the control gate electrode 24 has side walls 300 .

[0107] 11, reference numeral 10 denotes a substrate; 12, a base insulating film; 14, a semiconductor layer; 29, a channel formation region; 18a and 18b, a source region or a drain region; 20 is a floating gate electrode; 22 is a second insulating film (also called a control insulating film); 24 is a control gate electrode; 300 is a side wall; 26a and 26b are conductive layers; 28a and 28b are through Conductive layers 26a and 26b are connected to source or drain electrodes of source or drain regions 18a and 18b; 28c is a gate wiring electrically connected to a control gate electrode; 27 is...

Embodiment approach 3

[0122] In this embodiment mode, a structure of a nonvolatile memory different from the structure shown in FIGS. 1 and 11 will be described with reference to FIGS. 14A and 14B, FIGS. 15A to 15D, and FIGS. 16A and 16B.

[0123] In the nonvolatile memory element shown in FIG. 14A, first impurity regions (source or drain regions) 306a and 306b, second impurity regions 307a and 307b, etc. are provided in the semiconductor layer 14, and the floating gate electrode 20 is composed of A floating gate electrode 20a and a second floating gate electrode 20b are formed, which are different from the structures shown in FIGS. 1 and 11 .

[0124] In the structure shown in FIG. 14A, a base insulating film 12 is formed on a substrate 10, and a base insulating film 12 having first impurity regions 306a and 306b, second impurity regions 307a and 307b, and a channel formation region 29 is formed on the base insulating film 12. The semiconductor layer 14. The first insulating film 16 and the condu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More