Method and system for processing interruption

A processing method and technology of co-processing chips, applied in electrical digital data processing, instruments, etc., can solve problems such as affecting the processing speed of embedded systems, increasing software load, and large workload, saving system power consumption and reducing software load. , the effect of improving the processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

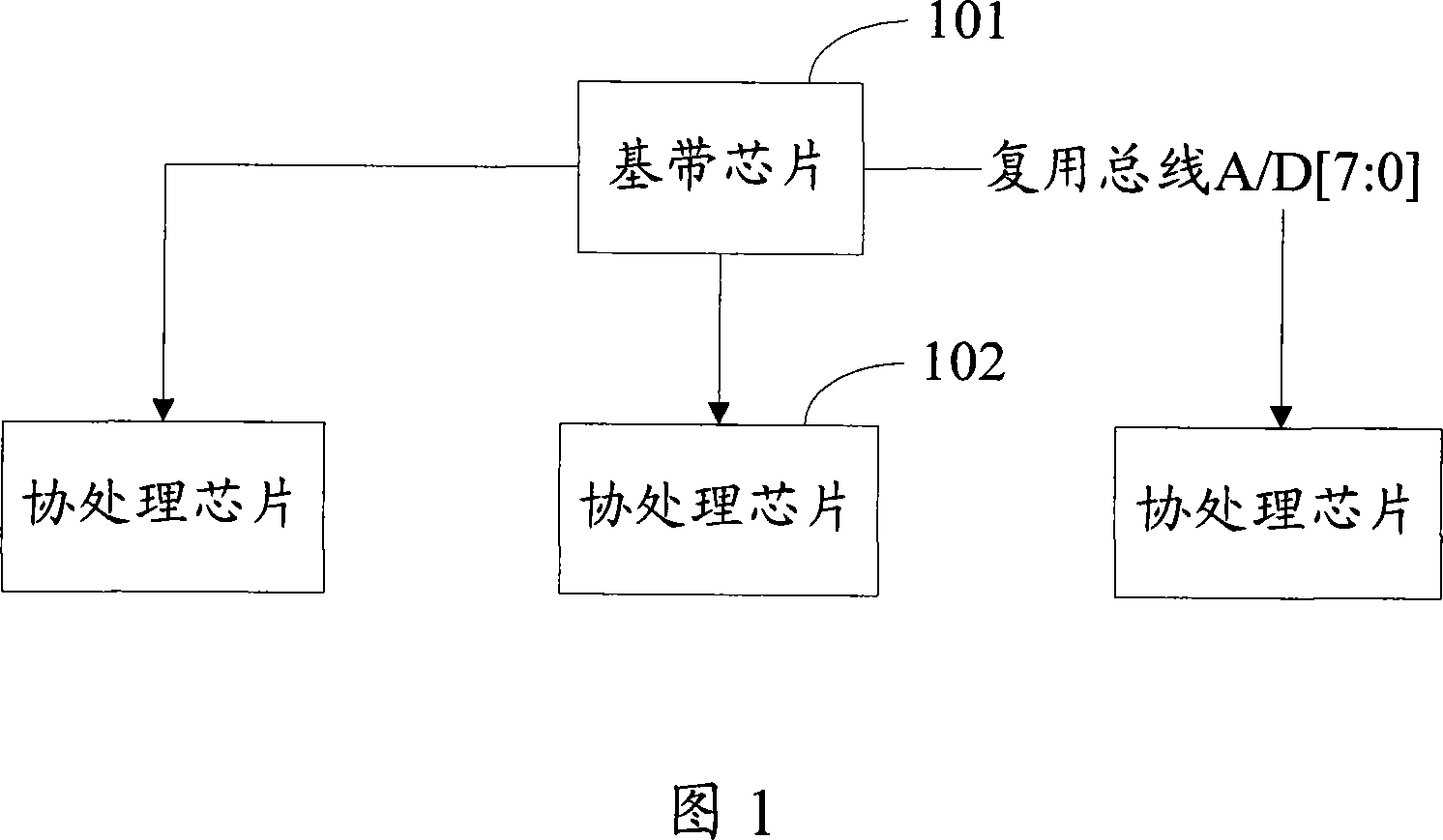

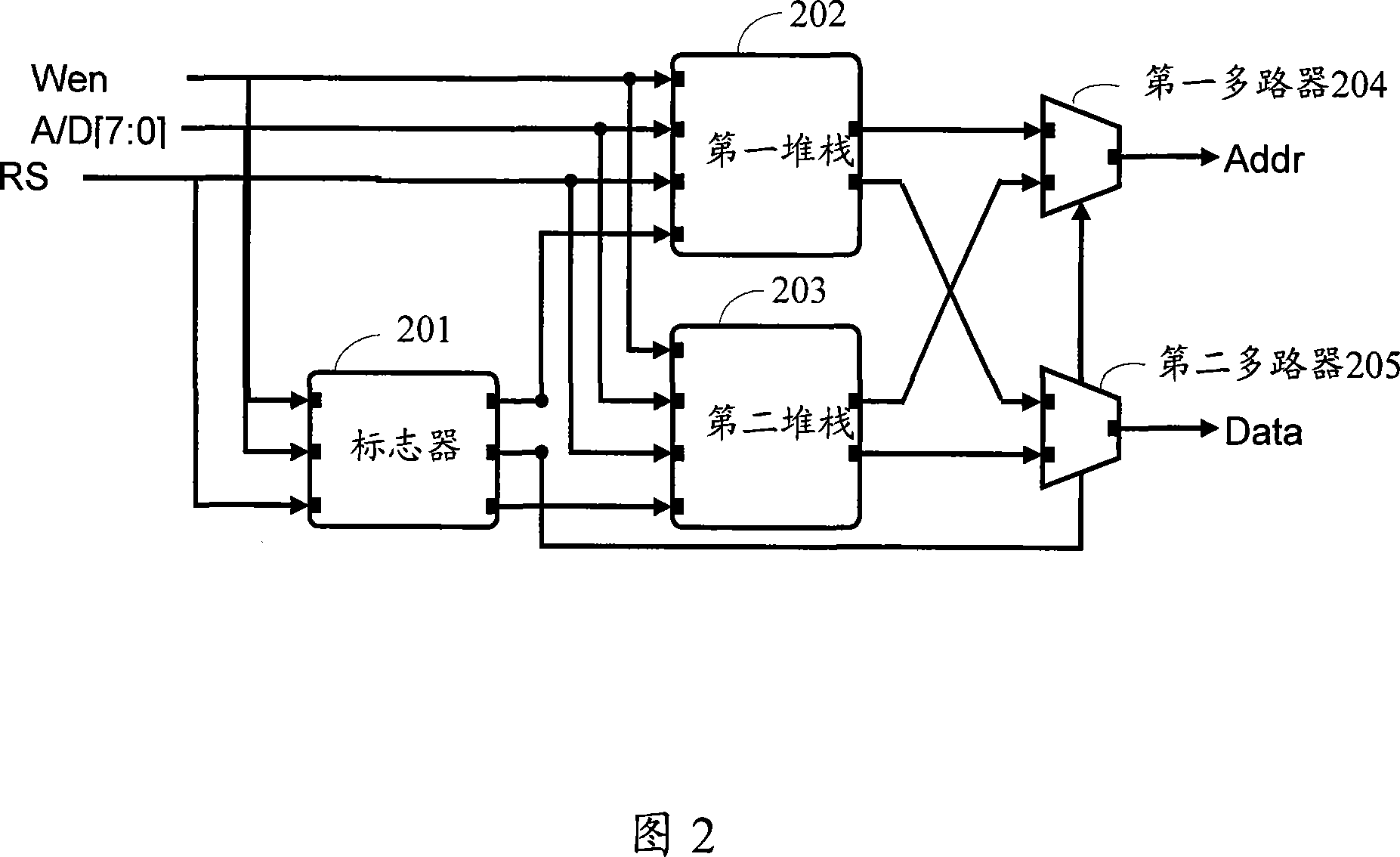

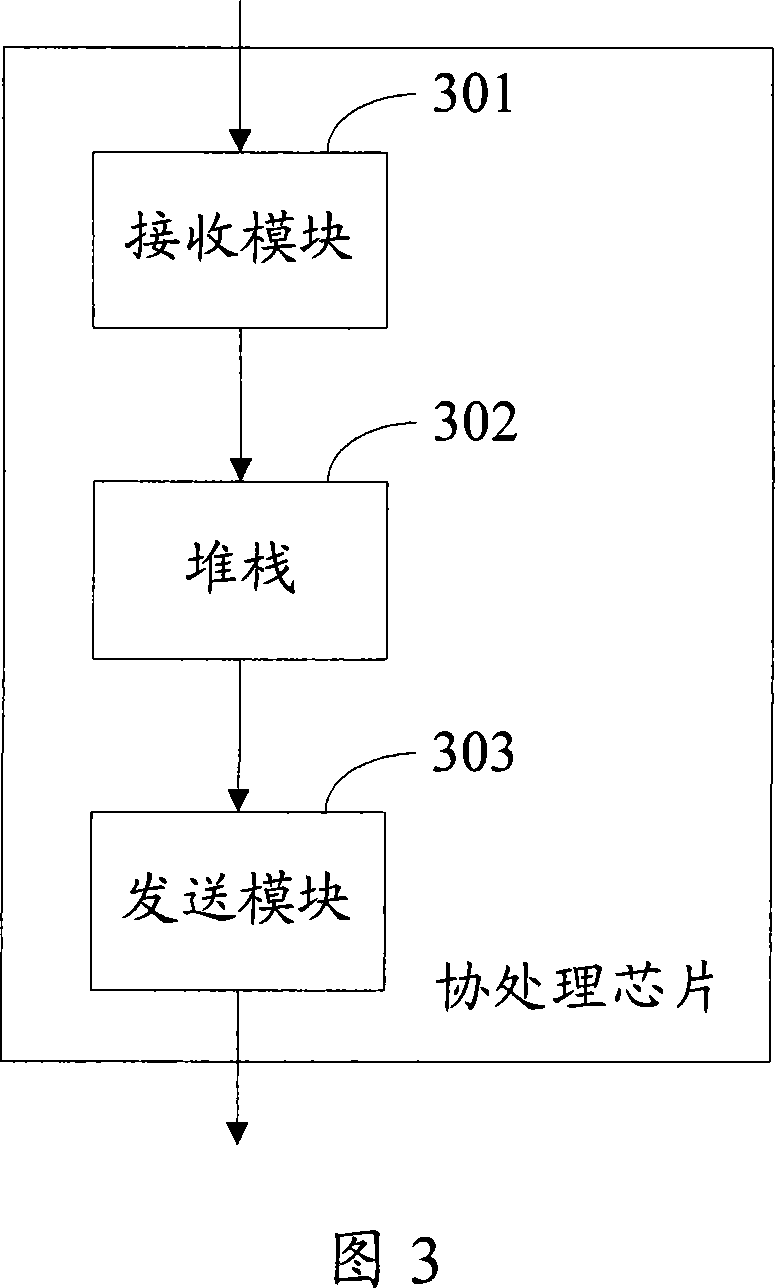

[0030] In this embodiment, when the baseband chip generates an interrupt, it sends an interrupt flag to the co-processing chip through the data / address multiplexing bus (hereinafter referred to as the multiplexing bus), and notifies the co-processing chip to perform operations related to the interrupt. This embodiment provides a co-processing chip including at least two hardware stacks (hereinafter referred to as stacks), one of which is used to process data and addresses in normal mode, and the other stack is used to process data and addresses in interrupt mode. The normal mode in this embodiment is relative to the interrupt mode, that is, the working mode after no interrupt is generated or the interrupt ends.

[0031] The baseband chip can send an interrupt flag to the co-processing chip through the data multiplexing bus in the form of data, or send the interrupt flag to the co-processing chip in the form of an address through the data multiplexing bus, depending on the locat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More