Semiconductor device

A technology for semiconductors and devices, applied in the field of semiconductor devices, can solve the problems of increasing the area of ESD protection circuits, the cost of ESD protection circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

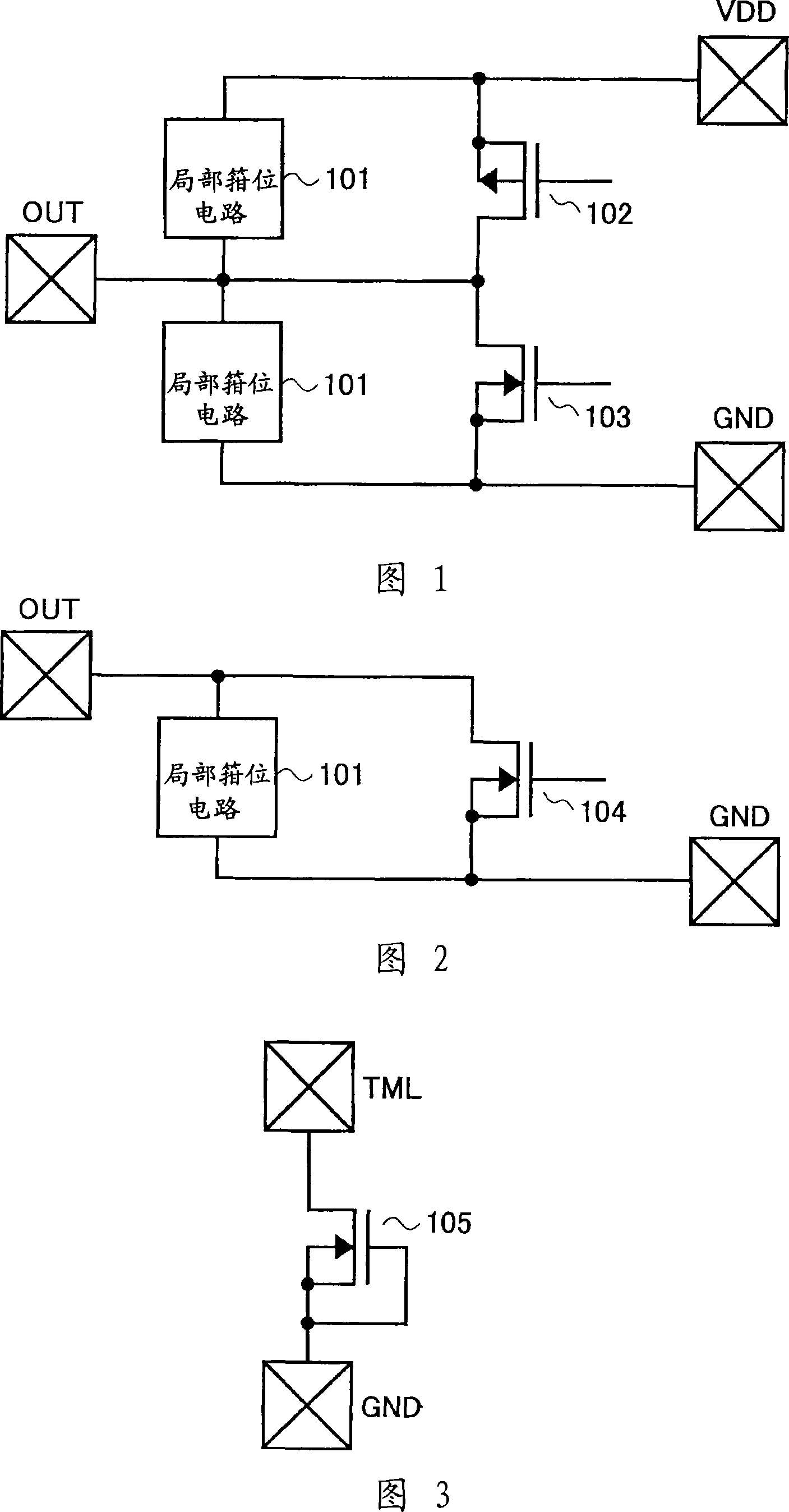

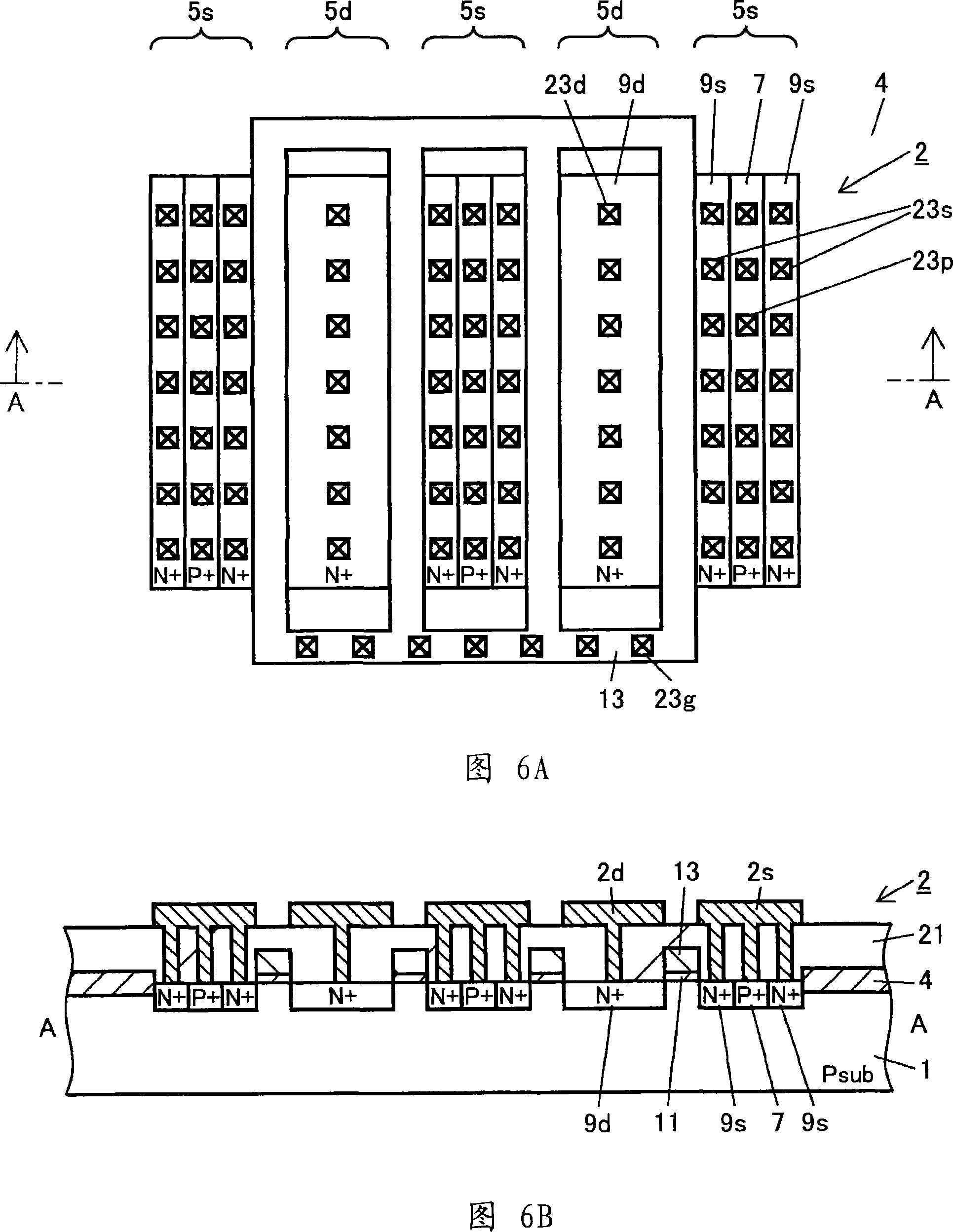

[0033] 6A to 6D are diagrams showing a first embodiment of a semiconductor device according to the present invention. 6A is a plan view showing an output NMOS driver, and FIG. 6B is a cross-sectional view of the output NMOS driver taken along line A-A of FIG. 6A. FIG. 6C is a plan view of a grounded gate NMOS (ggNMOS) protection element, and FIG. 6D is a cross-sectional view of the ggNMOS protection element taken along line B-B of FIG. 6C . FIG. 7 is a circuit diagram showing a first embodiment of the semiconductor device. First, a description will be given of the structures of the output NMOS driver and the ggNMOS protection element with reference to FIGS. 6A to 6D .

[0034] The LOCOS oxide layer 4 is formed on the P-type silicon substrate 1 to define a driver formation area where an output NMOS driver (NMOS switching element) 2 is formed and a protection element formation area where a ggNMOS protection element (NMOS protection element) 3 is formed.

[0035] A description ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More