QC-LDPC encoder horizontal arithmetic unit fast assembly line cascade connection structure

A computing unit and cascaded structure technology, applied in the field of digital information transmission, can solve the problems of increasing computing time, not being able to meet the simple structure of multiplexed computing units of multiple HPUs, restricting the system clock frequency, etc., achieving increased design costs and simple structure , to achieve the effect of reuse

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

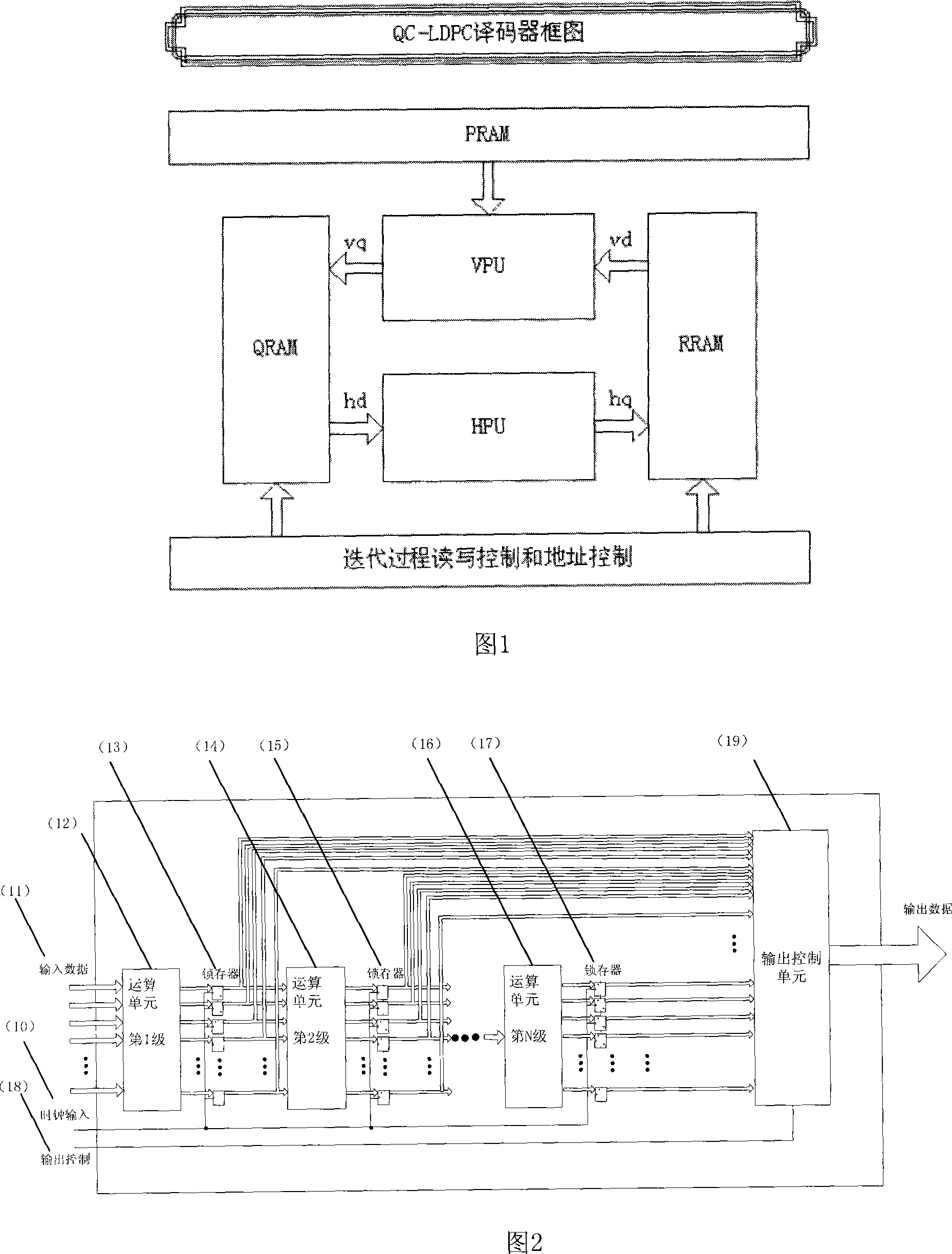

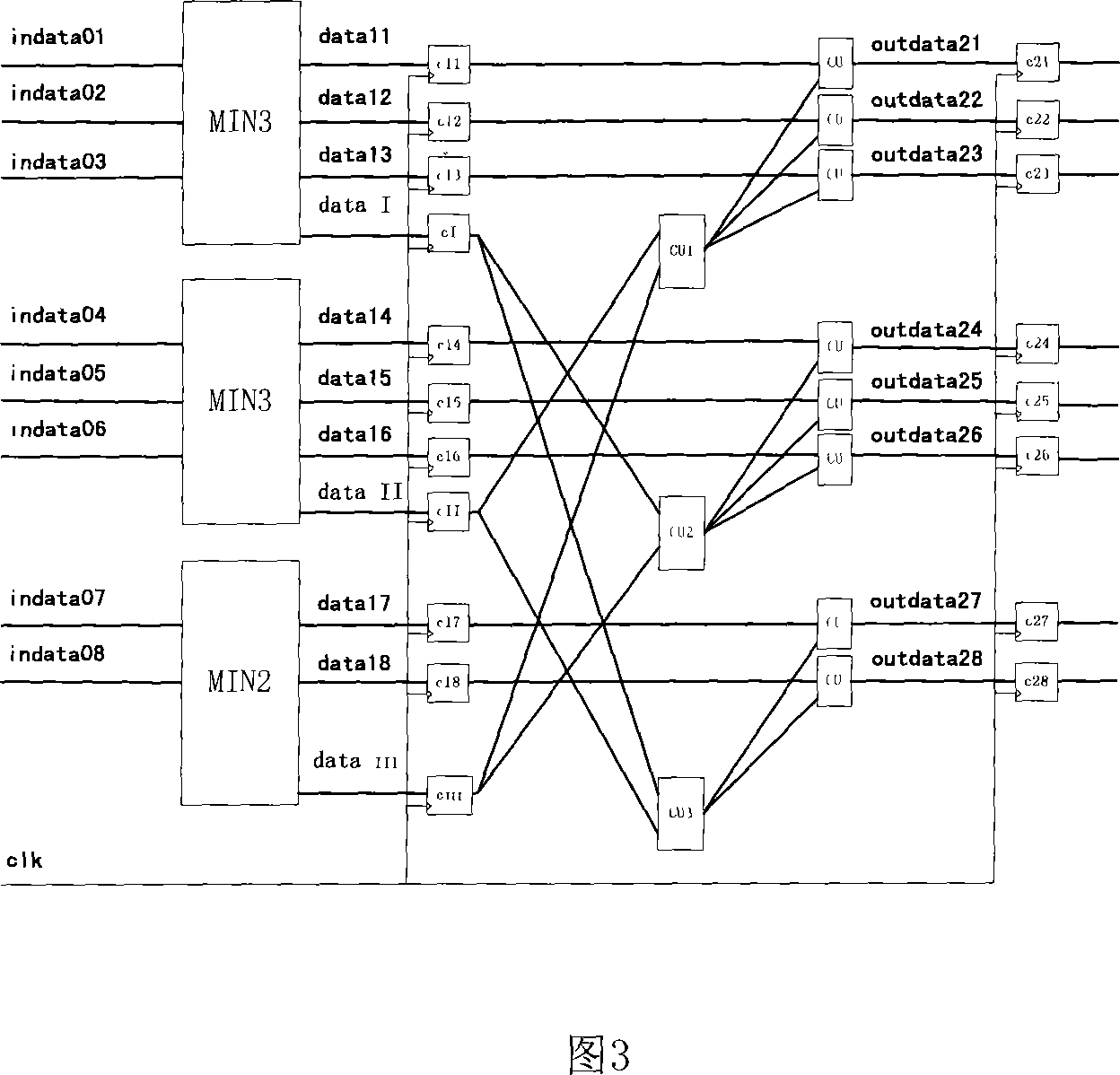

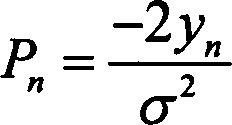

[0061] The invention provides a method for realizing the high-speed pipeline cascade structure of the HPU unit of the QC-LDPC decoder. According to the characteristics of different QC-LDPC codes, by rationally arranging the cascade structure of HPU units, the complex operations of HPU units can be realized in different clock cycles through classification. With such a pipeline structure, high-speed clock processing is realized. The present invention is characterized in that the traditional HPU unit is converted into a novel HPU unit with a multi-stage pipeline structure and can adapt to high-speed clock processing, so that it can be realized on FPGA.

[0062] The high-speed HPU unit with pipeline structure of the present invention comprises:

[0063] 1) Input port, the data of the input port is the data from the front-end QRAM, which is sent to the inside of the HPU unit through the input port. For different HPU units, the number of input ports is correspondingly different; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More