Clock synchronization device and synchronization method thereof

A clock synchronization and clock signal technology, applied in synchronization devices, digital transmission systems, electrical components, etc., can solve the problems of communication system soft switching failure, hardware unit reset, one or more abnormal output clocks, etc., to avoid system clocks Abnormal events, improve reliability, and ensure the effect of system communication quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The preferred embodiments of the technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings.

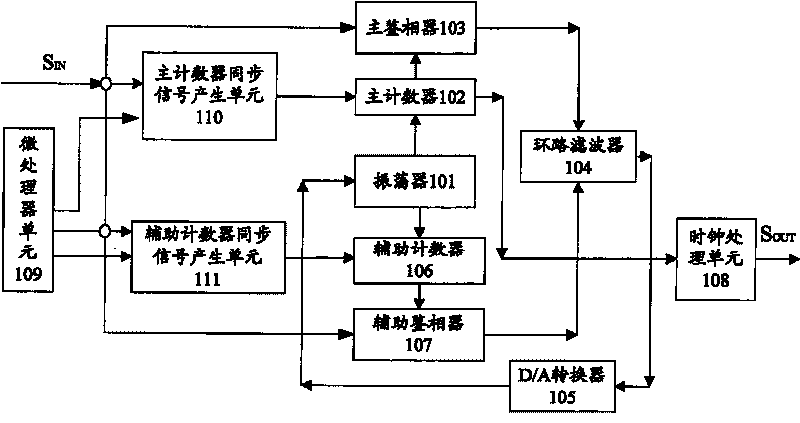

[0037] refer to figure 1 As shown, the synchronization processing device for synchronizing clock output signals in digital communication equipment uses the digital phase-locked loop on the reference clock unit to make the output clock signal of the oscillator 101 track the input reference clock signal S IN , so that the output clock signal S OUTSynchronized with the output clock signal of the oscillator 101, and finally the reference clock signal S IN , the clock signal output by the oscillator 101, the output clock signal S OUT The three are phase-synchronized. In the process of digital phase discrimination, the microprocessor unit 109 and the input reference clock S IN It works together with the main counter synchronization signal generation unit 110 or the auxiliary counter synchronization signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More