Method for forming device isolation region

A technology of device isolation and wet etching, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of polysilicon layer residue, word line short circuit, etc., to maintain height and reduce static leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

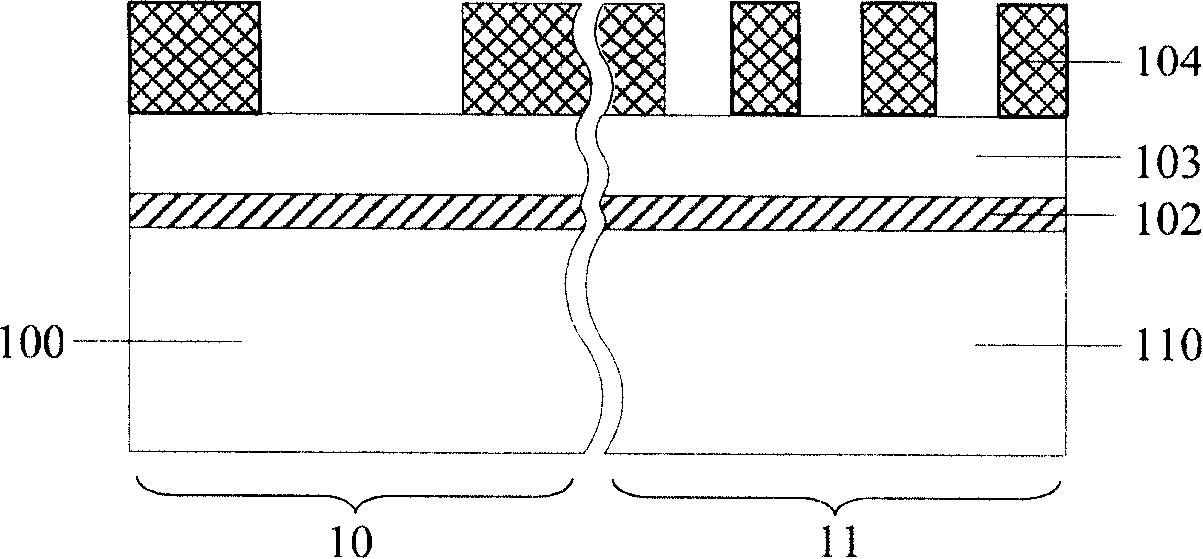

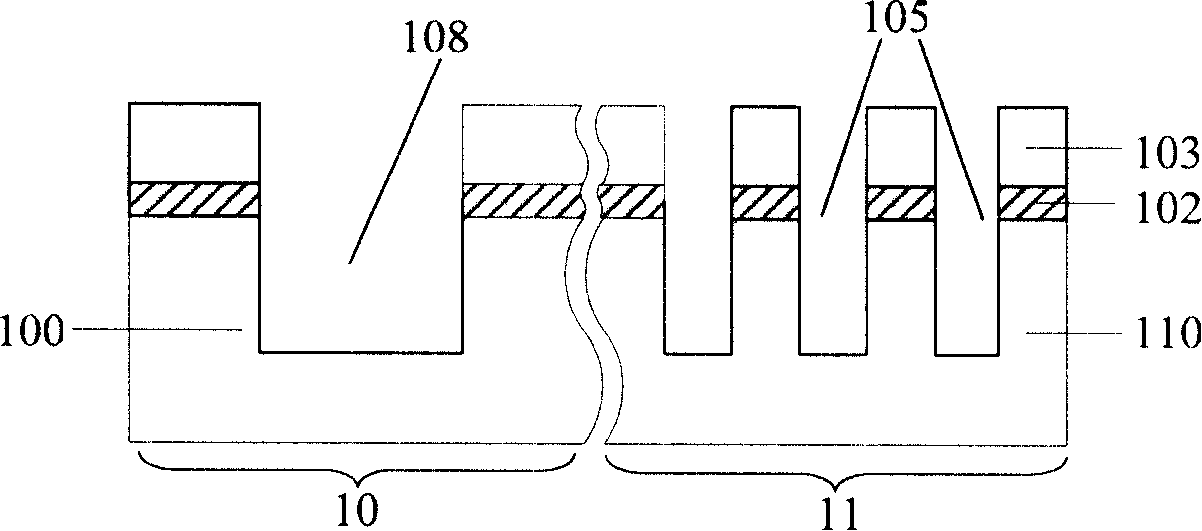

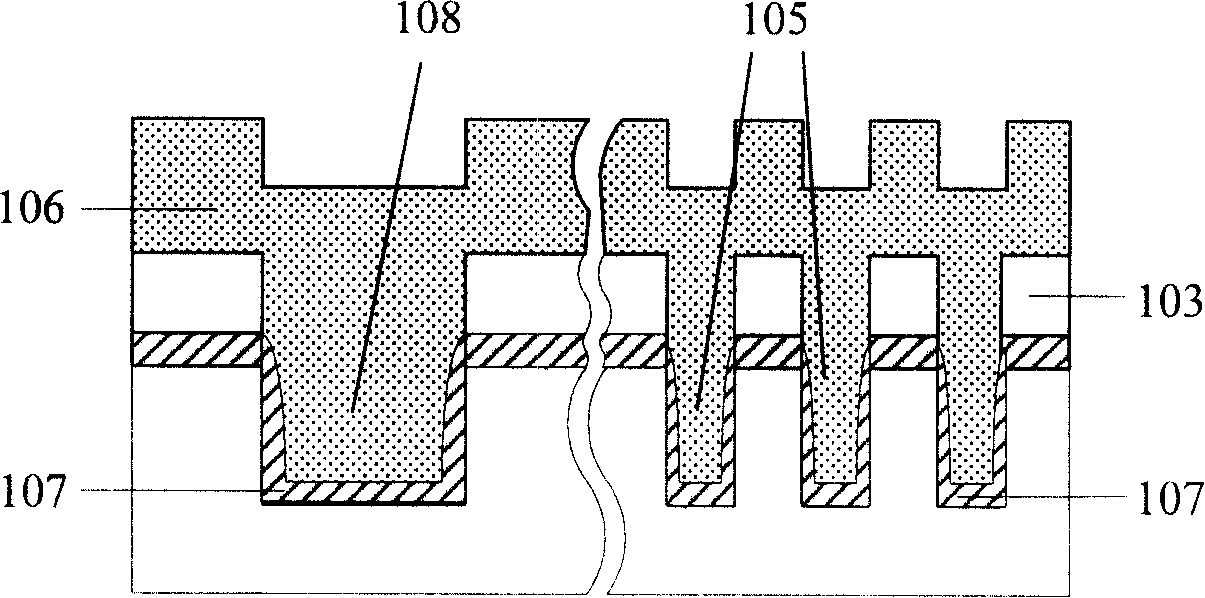

[0019] As the semiconductor technology enters the deep submicron era, the active area isolation of devices below 0.18 μm has mostly been produced by shallow trench isolation technology. Shallow trench isolation technology is an effective method to solve the "bird's beak" problem caused by local oxidation isolation in MOS circuits. In the existing process of manufacturing the shallow trench isolation structure, since the insulating oxide layer in the shallow trench is lower than the insulating oxide layer on the silicon nitride layer after the deposition of the insulating oxide layer, the insulating oxide layer is polished to the silicon nitride layer. When the silicon nitride layer is over-polished to ensure that the insulating oxide layer on the silicon nitride layer is completely removed, when the silicon nitride layer is over-polished, the insulating oxide layer in the shallow trench will also be removed. During grinding, since the rate of grinding the silicon nitride layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More