ECC/RSA encryption/decryption coprocessor

A coprocessor, encryption and decryption technology, applied in encryption devices with shift registers/memory, public keys for secure communication, and calculations using non-number system representation, etc., can solve the problem of large chip area, high cost, soft Problems such as multiple hardware interactions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The above and other technical features and advantages of the present invention will be described in more detail below in conjunction with the accompanying drawings.

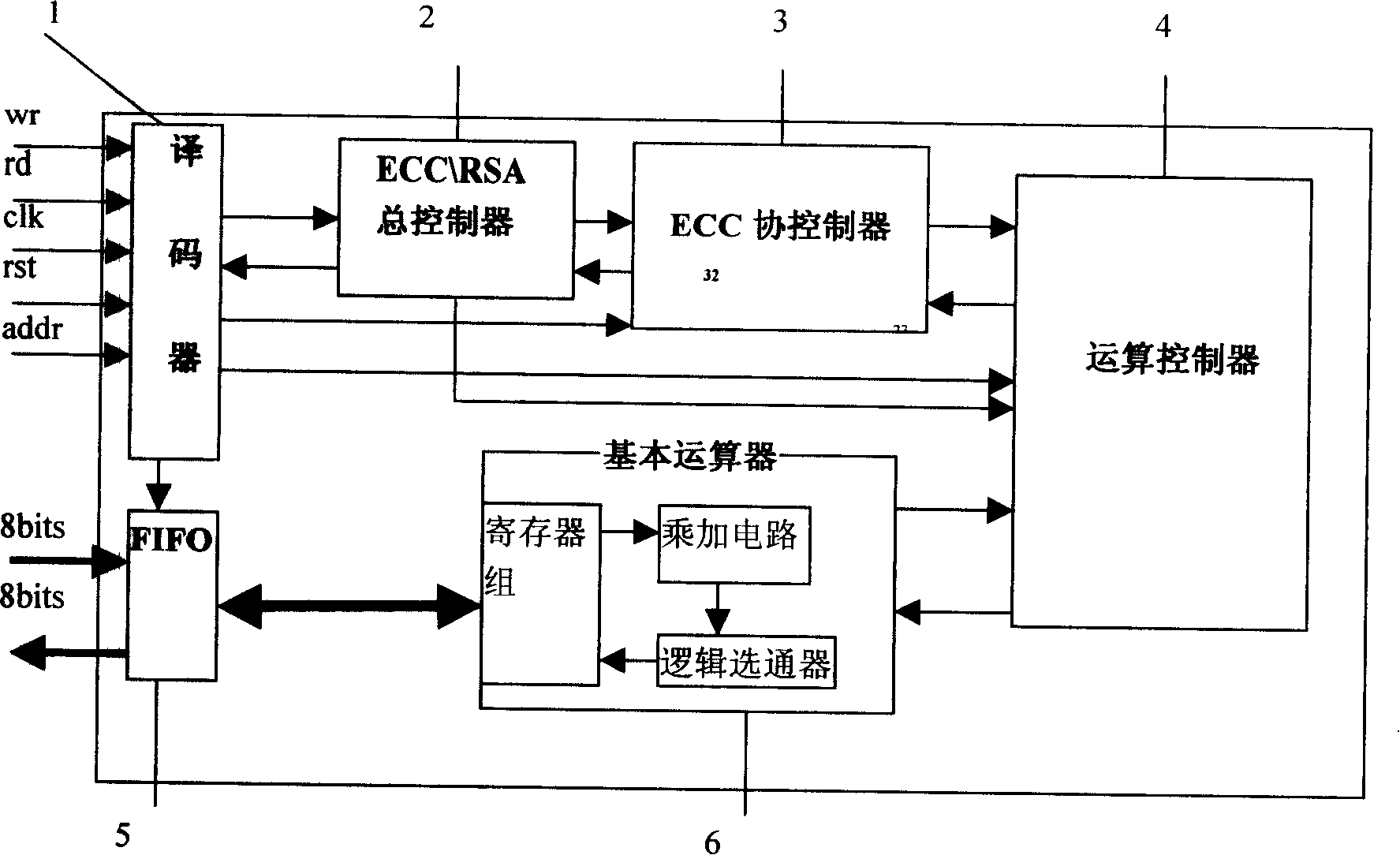

[0020] see figure 1 It is the configuration diagram of the preferred embodiment of the coprocessor of the ECC\RSA encryption algorithm of the present invention, which includes: decoder 1; ECC\RSA general controller 2; ECC co-controller 3; computing controller 4; FIFO ( cache) 5; basic arithmetic unit 6.

[0021] Wherein, described decoder 1 is connected with ECC\RSA total controller 2, ECC co-controller 3, operation controller 4 and FIFO5 respectively; Exchange data; after the external data is written into FIFO5, it is controlled by decoder 1 and sent to the corresponding register. It can directly control the ECC\RSA main controller 3 to complete RSA and ECC operations; it can also directly control the ECC co-controller 3 to complete ECC single-step calculation; it can directly control the operation cont...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More