Printed circuit board image skeletonization method based on FPGA

A technology of printed circuit board and image skeleton, which is applied in the direction of measuring electricity, measuring electrical variables, measuring devices, etc., can solve the problems of missing image features, time-consuming detection, and difficulty in real-time processing, so as to release software resources and improve processing speed. Effect

Inactive Publication Date: 2008-07-16

THE 45TH RES INST OF CETC

View PDF0 Cites 7 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

[0003] The purpose of the present invention is to provide an FPGA-based printed circuit board image skeletonization method, to solve the technical problems that the existing algorithm for thinning and extracting image skeletons often loses image features, and the detection is time-consuming and difficult to realize real-time processing

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

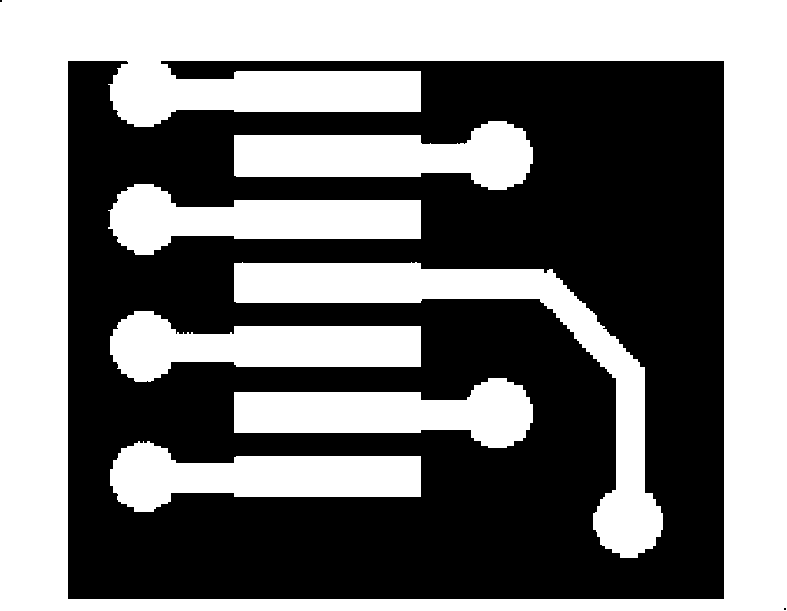

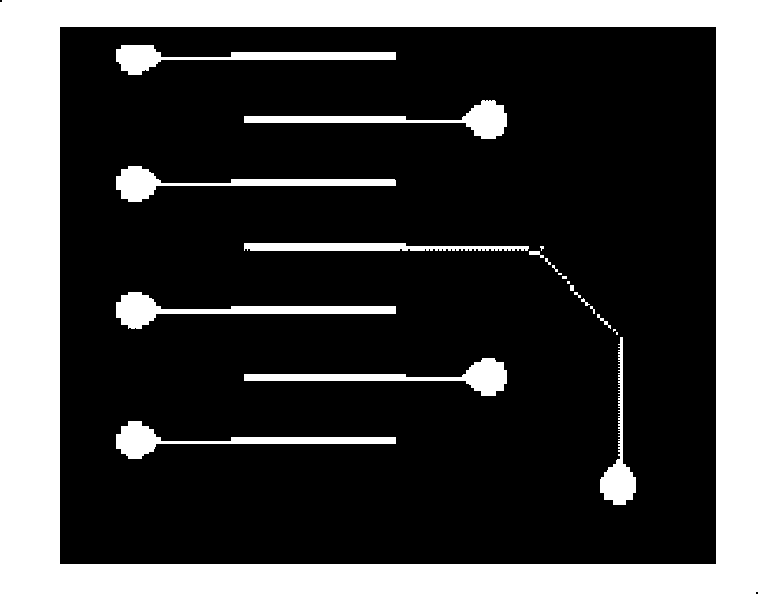

[0028] Examples see Figure 4 :

[0029] Step 1, input image data.

[0030] Step 2, analyze the 3×3 neighborhood of each pixel, and count the number n of 1 in the surrounding 8 pixels, and the number S of conversions between 0 and 1, the output is 1, and the pixel that is 1 is retained.

[0031] Step 3, judge whether the center pixel is 1, if the output is 0, delete the center pixel.

[0032] Step 4, when 1

[0033] Step 5, when 1

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

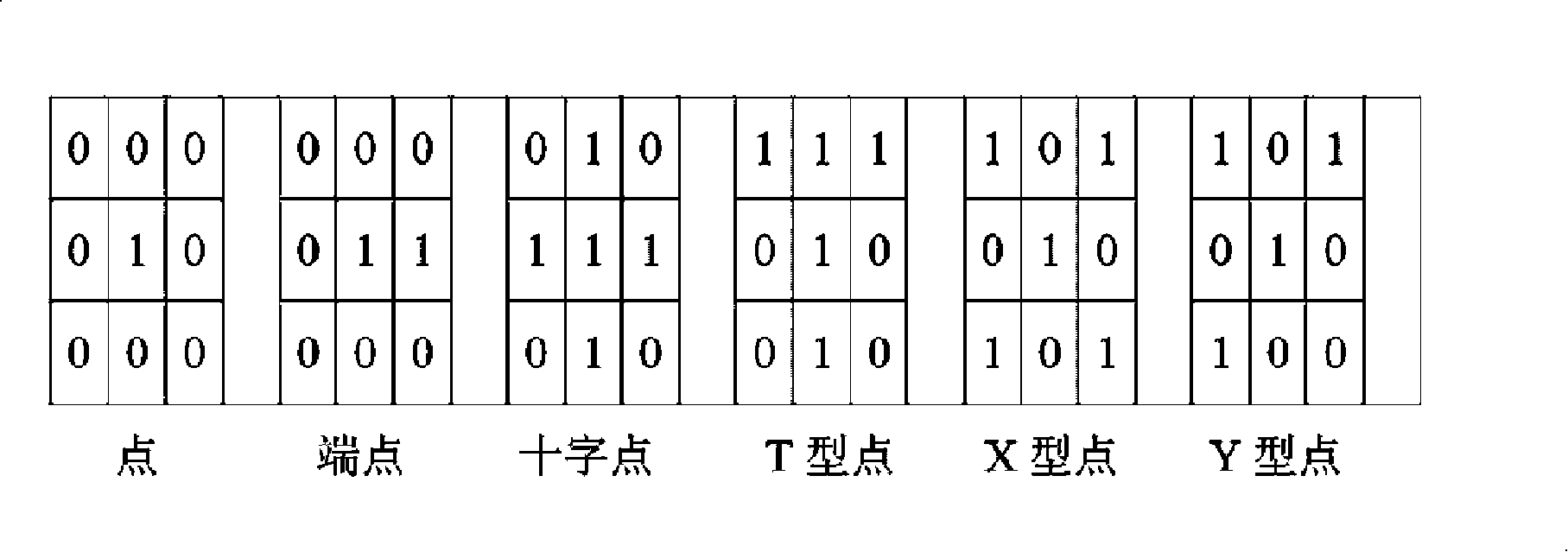

The invention relates to an image skeletonization method of a printing circuit board based on FPGA which firstly inputs an image to analyze the neighborhood of each pixel and count the number n with a pixel value of 1 among the surrounding 8 pixels and the pixel with a switch time S between 0 and 1, with an output being 1 and a preservation being 1; then, judging whether a central pixel is 1; deleting the central pixel if the central pixel is zero; when n is more than 1 but is equal to or less than 6, S is equal to 2, and circulating time is odd, investigating the pixels on the right and lower directions of the central pixel and the pixels on the left and right directions of the central pixel, judging whether 0 and 1 are cross, outputting 0 and deleting the pixel; when n is more than 1 but is equal to or less than 6, S is equal to 4, n is equal to 4, and the circulating time is odd, investigating the pixels on the upper-left and upper-right directions of the central pixel and the pixels on the lower-left and lower-right directions of the central pixel; judging whether the lower side pixel of the central pixel is 1 and whether 0 and 1 are two communicating areas; if the pixel is 0, deleting the pixel. The invention can fast and accurately withdraw the image skeleton.

Description

(1) Technical field [0001] The invention relates to a detection method for defects of printed circuit boards. (2) Background technology [0002] At present, the known detection methods for printed circuit board defects are based on simple logical operations such as addition and subtraction of images. The real-time processing of the collected images is realized, which affects the detection efficiency. The existing method for extracting the image skeleton is a thinning algorithm, which uses binary morphological operations to determine the 8-neighborhood of pixels. In the process of skeleton extraction, because the speed of deleting pixels in the up, down, left, right and diagonal directions is different, the result will lose some basic features of the image. The skeleton of the pad is extracted as a cross or ×, which seriously affects the subsequent Image processing; and the thinning algorithm needs to perform 8-neighborhood analysis on each pixel, and processing a large ima...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G01N21/956G01R31/00

Inventor 姚立新邴守东张云连军莉付纯鹤魏祥英

Owner THE 45TH RES INST OF CETC