LDPC decoding circular hierarchical minimum calculation method and its realization device

A calculation method and minimum value technology, applied in the field of digital information transmission, can solve problems such as limiting the working speed of LDPC decoders, restricting the throughput performance of decoders, and complex minimum value calculations, so as to improve the working clock frequency and throughput rate , simple structure, and the effect of reducing hardware resource consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

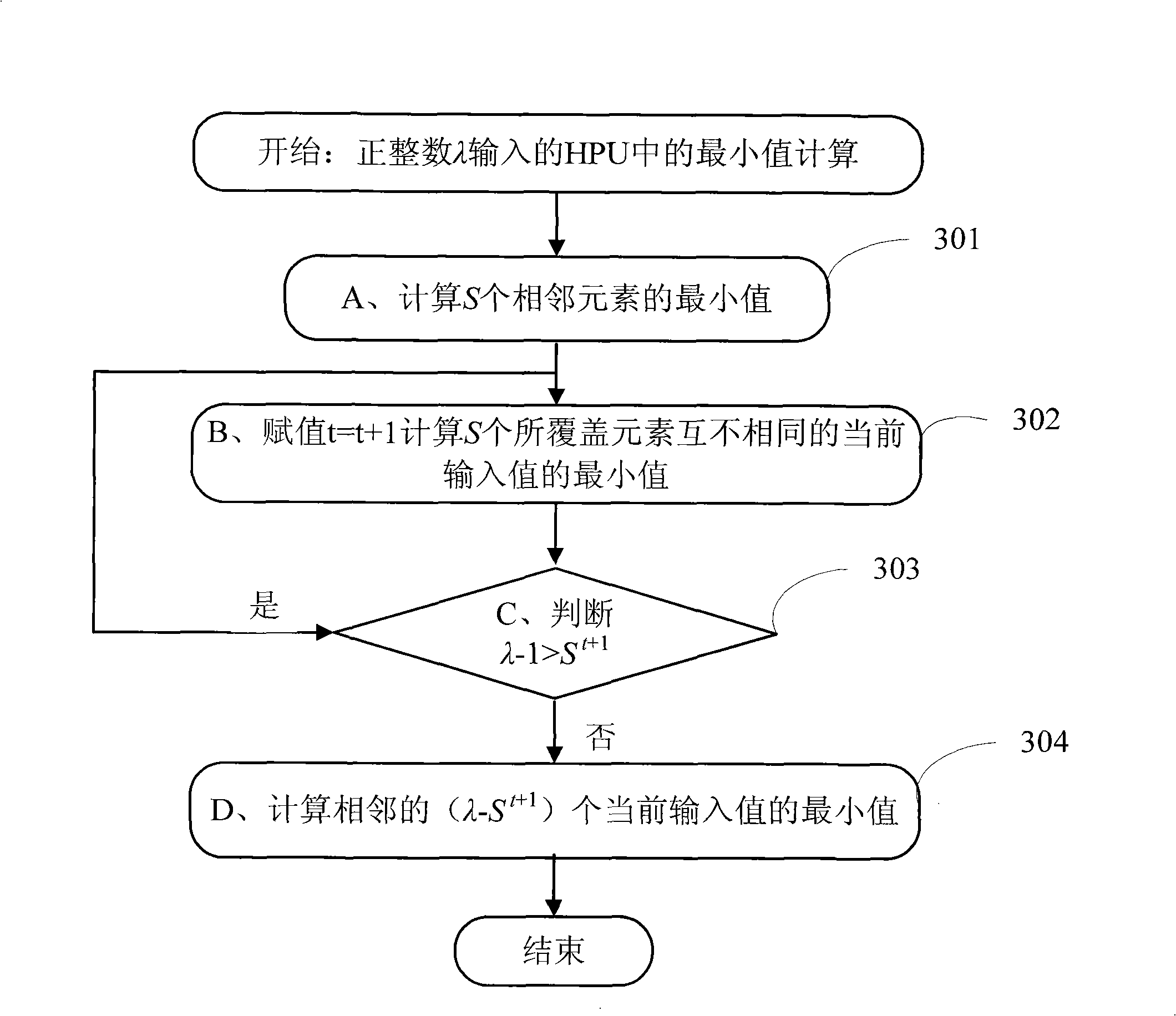

[0133] refer to Figure 5 , representing another embodiment as the implementation device, is a structure diagram of the implementation device based on the cyclical hierarchical minimum calculation method of the 3-input minimum calculation module, and the device is used to complete the minimum calculation in the HPU of the λ input. Among them, the min module represents the minimum value calculation module of 3 inputs. For the convenience of explanation, each min module in the figure is identified by two subscripts, the first subscript indicates the classification of the module, and the second subscript indicates the The number of the module in its hierarchy. The minimum value calculated by each module is marked above each minimum value module in the figure. Minimum calculation device based on 3-input minimum calculation module, including Each level consists of λ 3-input minimum calculation modules. The specific implementation of each classification is as follows:

[0134] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More