Analog switch chip design method and chip device

An analog switch chip and design method technology, applied in electronic switches, electrical components, pulse technology, etc., can solve the problems of affecting the operating bandwidth, performance mutual restraint, limiting the turn-off isolation performance of analog switches, etc., to improve the charge injection performance. , the effect of eliminating the offset effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in detail below in conjunction with a specific embodiment circuit.

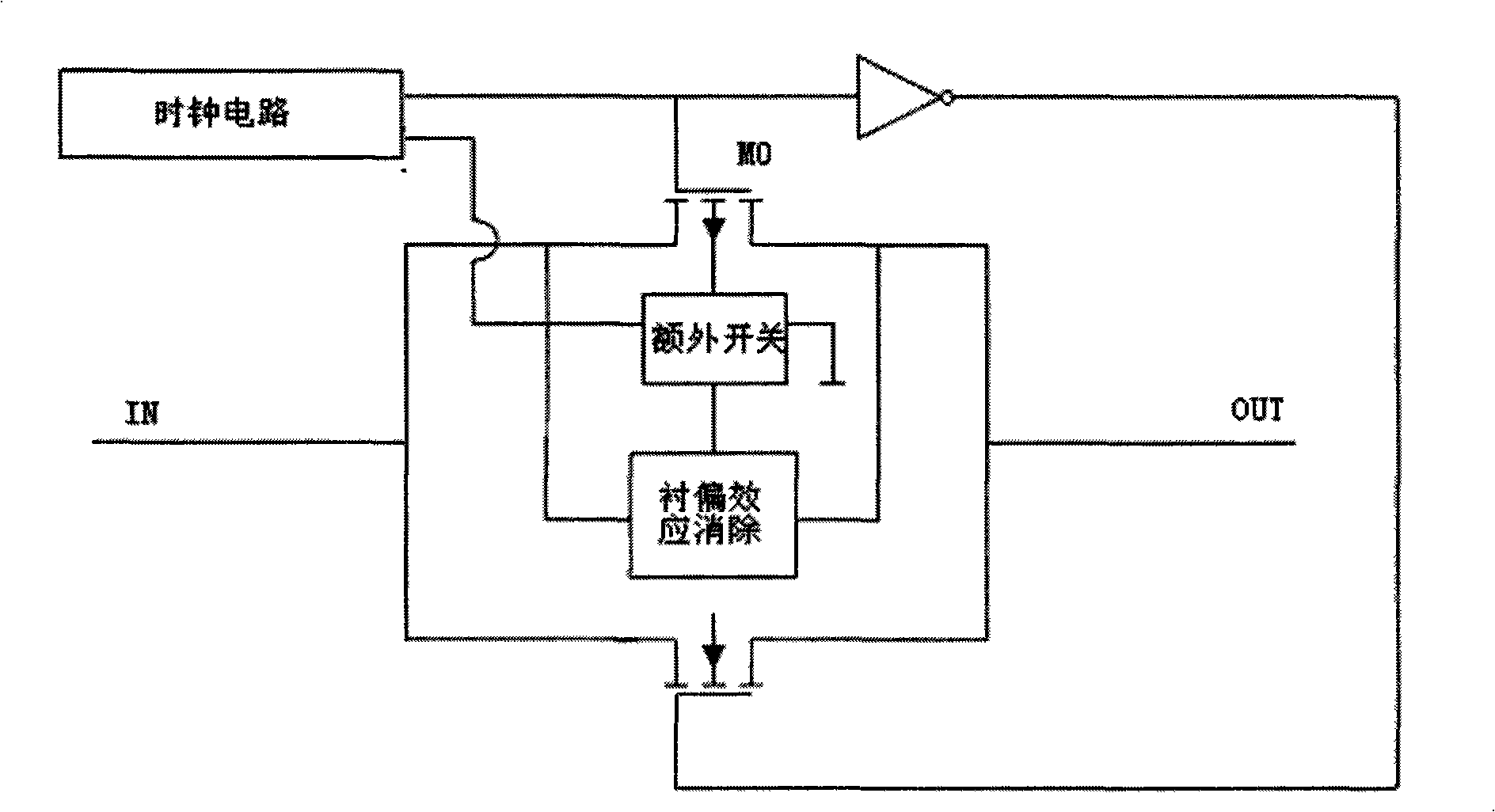

[0019] As attached figure 2 Schematic diagram of the circuit, the key point of the present invention is to use an additional switch controlled by the clock circuit to make the offset elimination circuit work under certain conditions, so that the substrate of the main switch MOS is connected to the relatively high potential end of the input and output terminals ; When the main switch is turned off, the substrate is directly connected to the power source to avoid the adverse effects of the offset elimination circuit on the main switch.

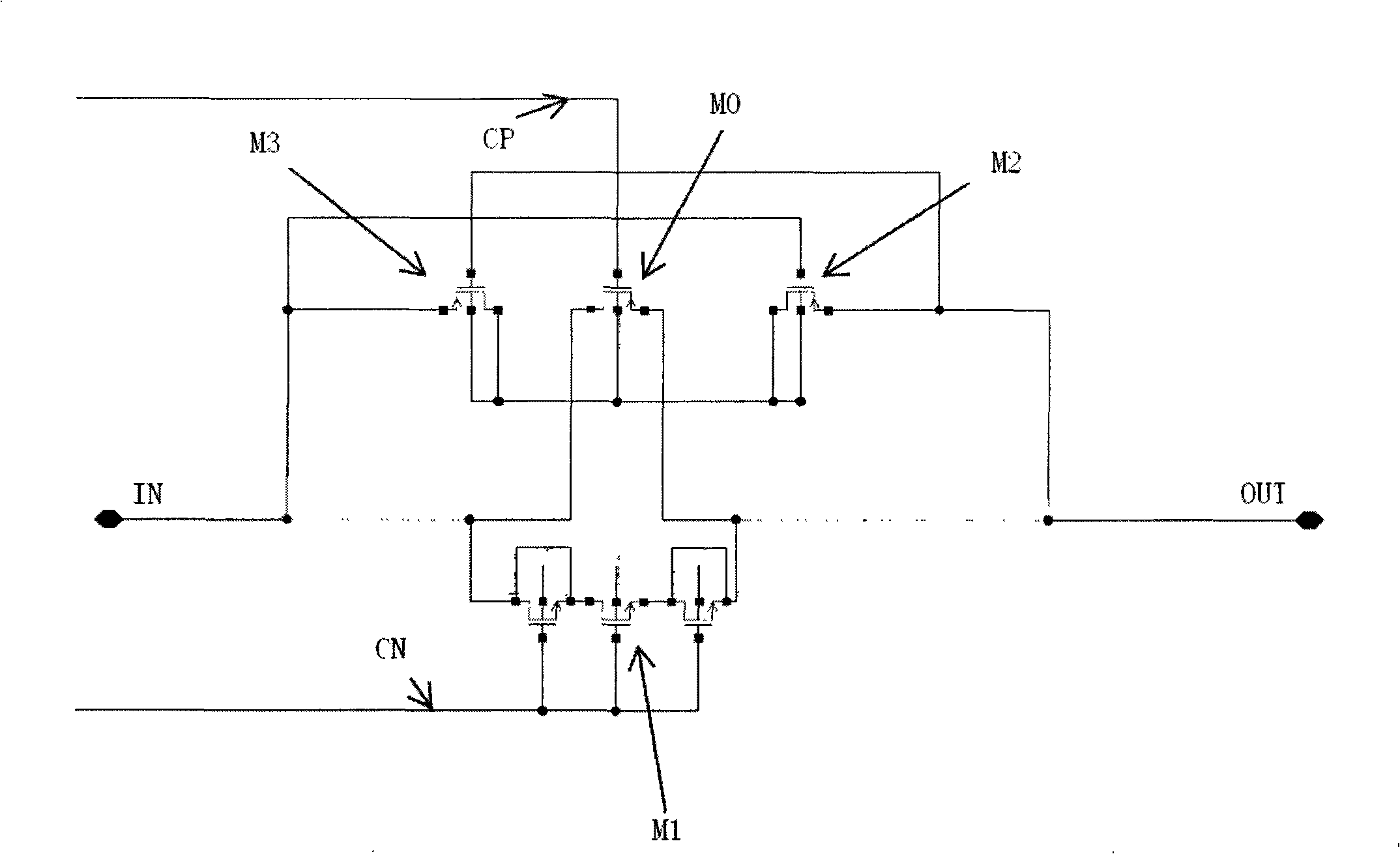

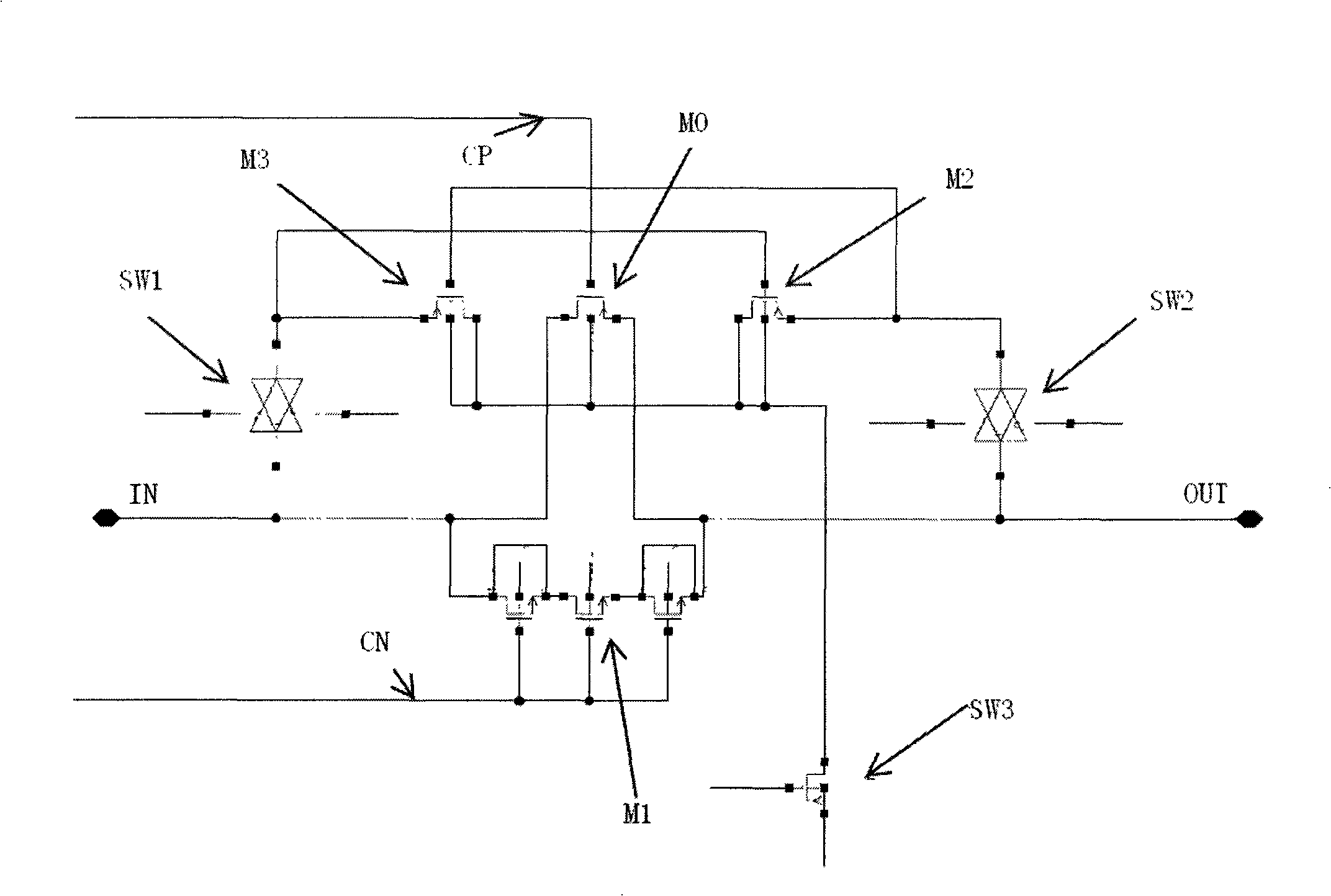

[0020] We take PMOS as an example, as attached image 3 It is a detailed circuit diagram of a specific embodiment of the analog switch chip of the present invention, and attached figure 1 Compared with the standard CMOS process analog switch circuit with offset elimination circuit shown, it can be clearly seen that M0 and M1 are the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More