Semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve the problems of operational amplifier oscillation and larger chip size, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

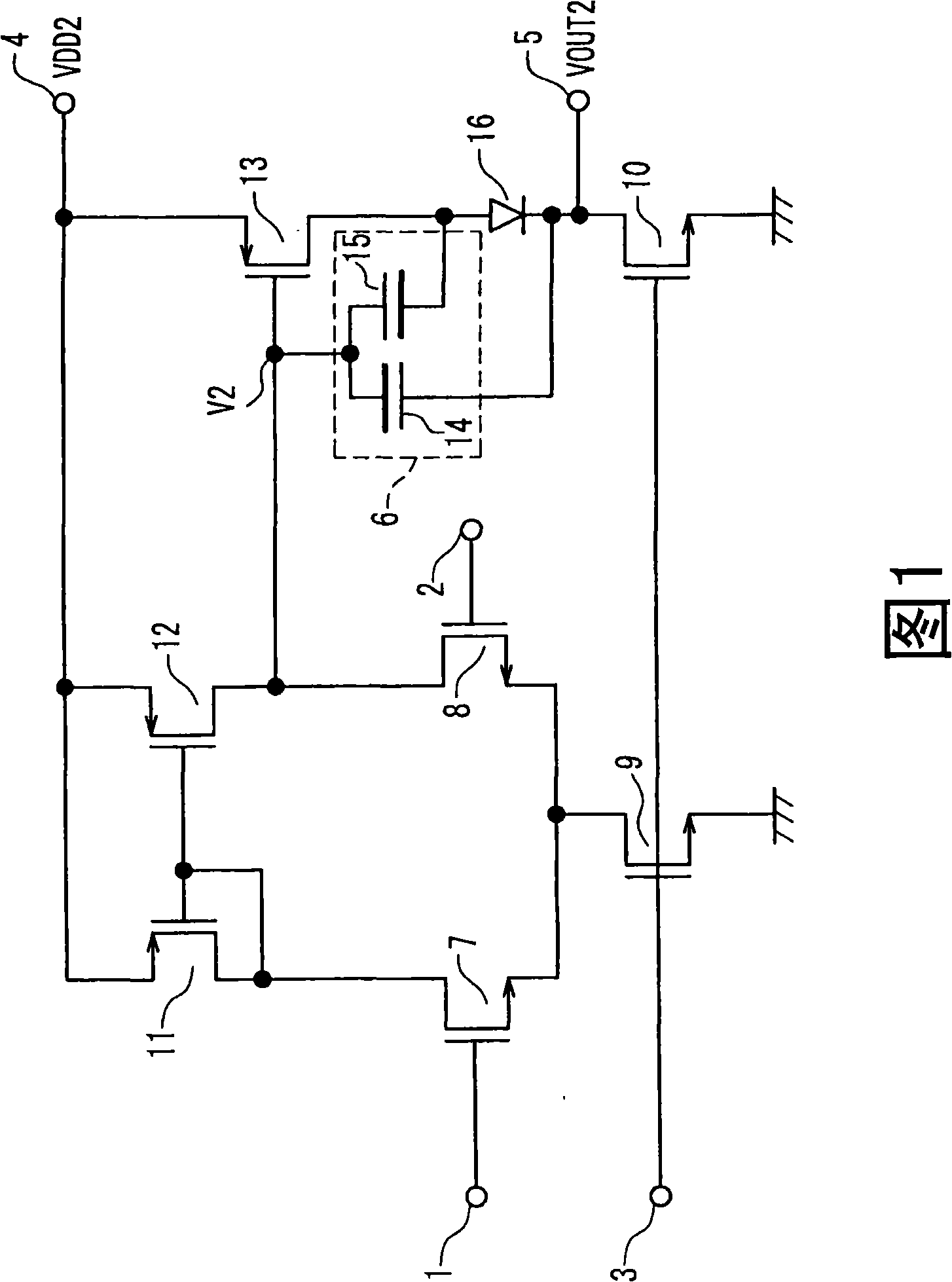

[0037]FIG. 1 shows a semiconductor device in Embodiment Mode 1 of the present invention. The N-channel MOS transistor 7 and the N-channel MOS transistor 8 constitute a differential input stage portion, and signals from the inverting input terminal 1 and the non-inverting input terminal 2 are input to respective gates. The source of the MOS transistor 7 and the source of the MOS transistor 8 are connected to each other, and a constant current is introduced from the drain of the N-channel MOS transistor 9 . The drain current of the MOS transistor 9 is set by the voltage of the bias voltage input terminal 3 .

[0038] The sources of the P-channel MOS transistors 11 and 12 are commonly connected to the power supply terminal 4 (high side power supply VDD2 ). The drain of the MOS transistor 7 is connected to the gates of the MOS transistors 11 and 12 and the drain of the MOS transistor 11 , and the drain of the MOS transistor 8 is connected to the drain of the MOS transistor 12 . ...

Embodiment approach 2

[0056] A semiconductor device according to Embodiment 2 of the present invention will be described with reference to FIG. 6 . This semiconductor device is an operational amplifier composed of bipolar transistors, MOS capacitors, diodes, and resistors. It is an example of a circuit that provides negative feedback from the output terminal to the inverting input terminal to buffer the input voltage (increase the current capability). .

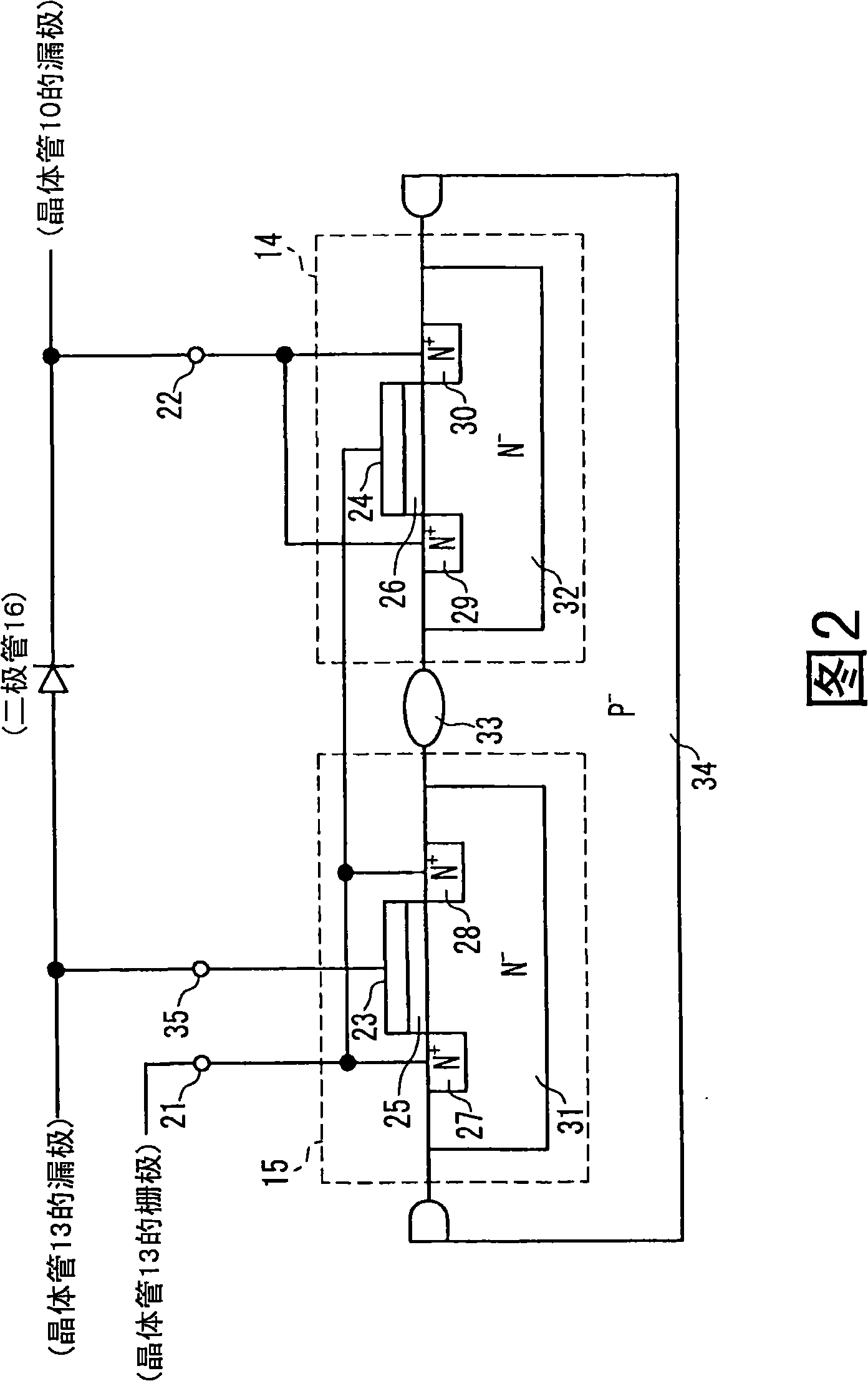

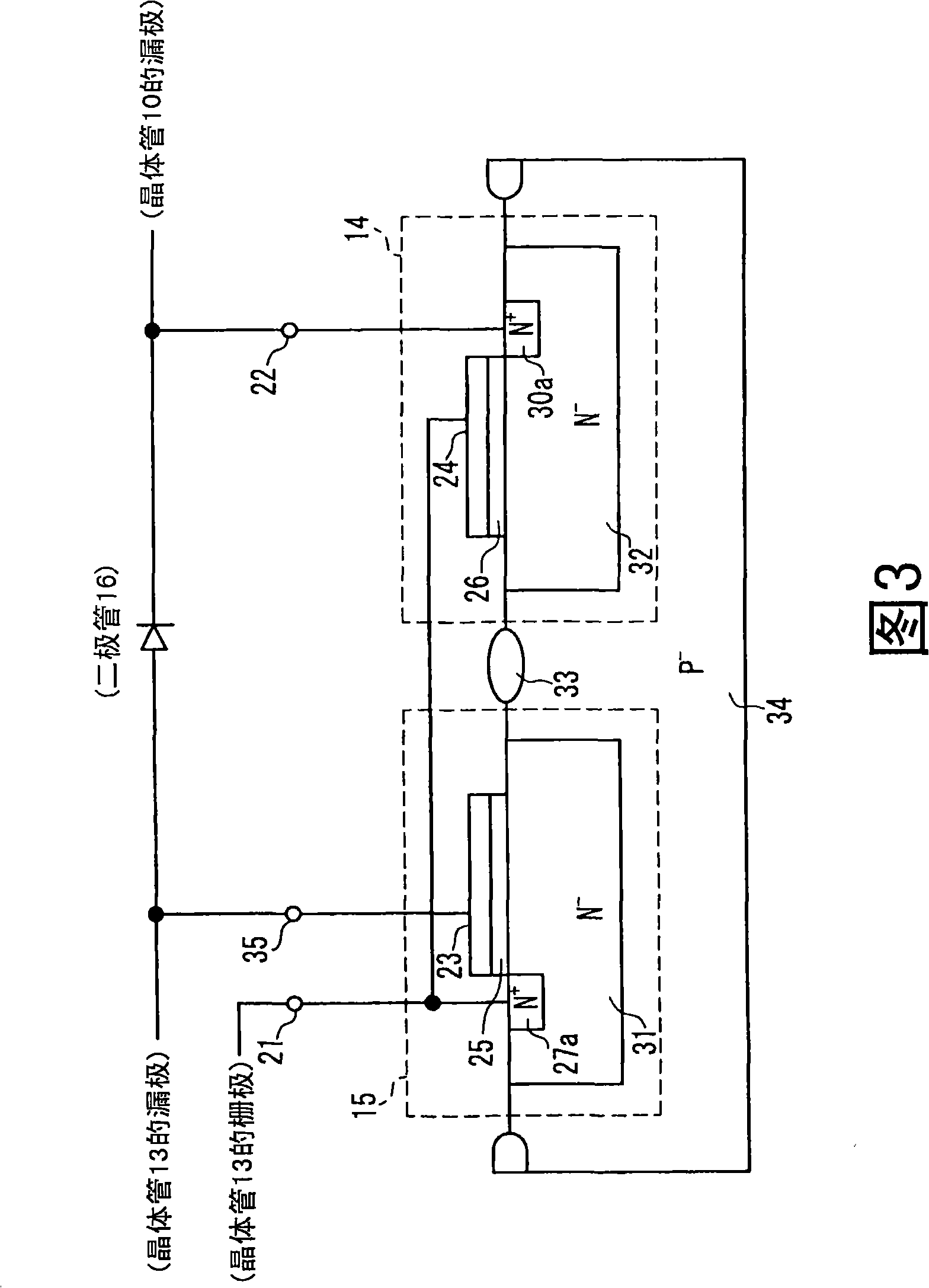

[0057] In Figure 6, 51-60 are PNP transistors, 61-64 are NPN transistors, 65 are diodes, 66-70 are resistors, 71 and 72 are MOS capacitors, 73 are constant current sources, 74 are high-side power supplies, and 75 are output Terminal 76 is a non-reversing input terminal, and 77 is a variable power supply. As the MOS capacitors 71 and 72, a structure having a gate oxide film between the gate electrode and the P well layer can also be considered. Here, as shown in FIG. 2 or FIG. In the case of a capacitor with a structure having a gate oxide film b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More