Semiconductor testing apparatus and semiconductor memory testing method

A test device and semiconductor technology, applied in the direction of static memory, read-only memory, information storage, etc., can solve the problems of time-consuming, increased test time, increased test cost, etc., and achieve the effect of shortening the test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Hereinafter, embodiments of the present invention will be described with reference to the drawings. This embodiment is not intended to limit the present invention.

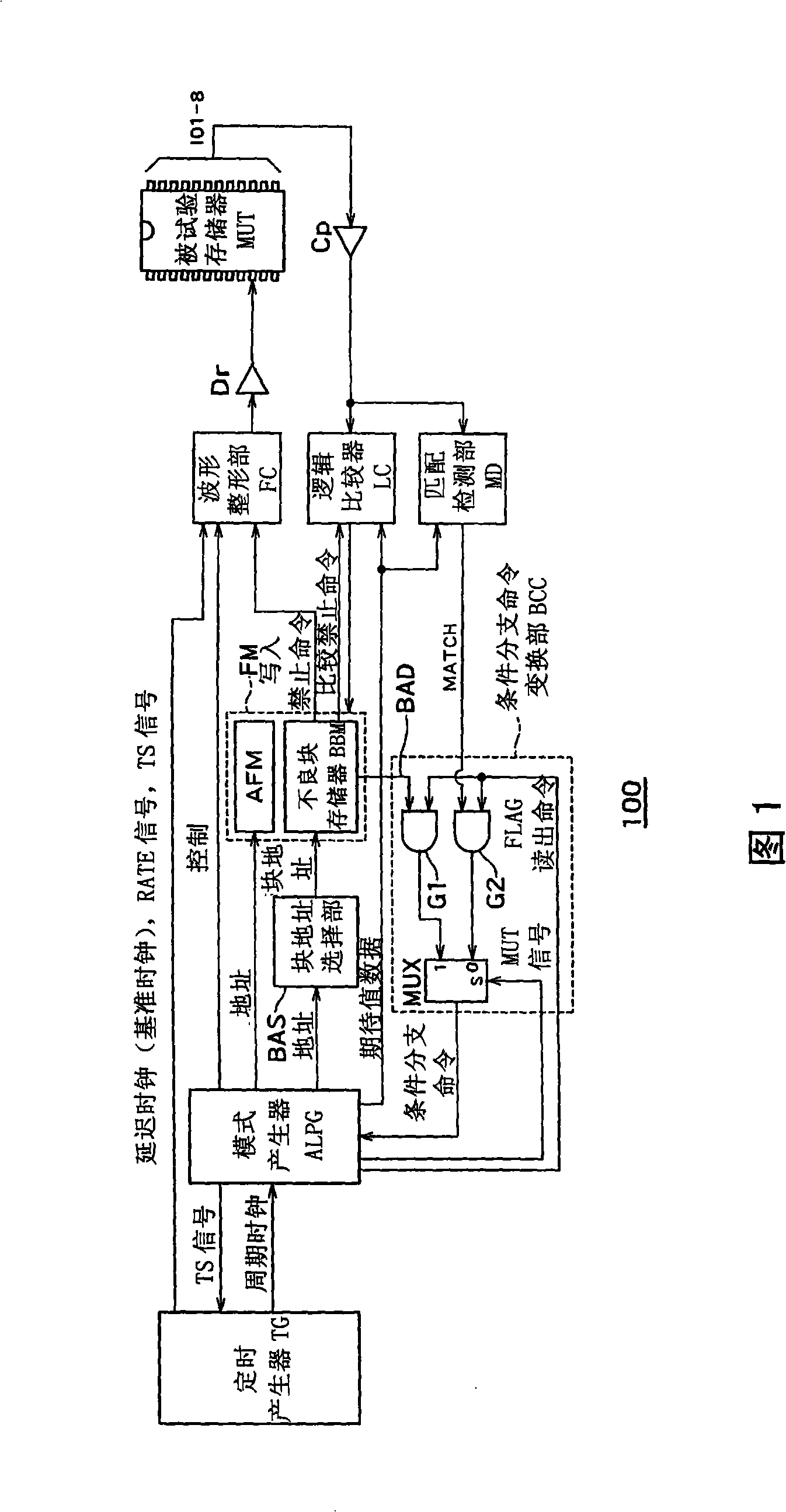

[0020] FIG. 1 is a schematic block diagram of a semiconductor memory testing device 100 (hereinafter referred to as device 100 ) according to an embodiment of the present invention. The device 100 includes: a timing generator TG, a pattern generator ALPG, a waveform shaper FC, a logic comparator LC, a fail bit memory FM, a block address selection unit BAS, a match detection unit MD, and a conditional branch command change unit BCC.

[0021] The pattern generator ALPG outputs a timing setting signal (TS signal) to the timing generator TG. The timing generator TG receives the TS signal, and generates timing edges of various channels defined based on the timing settings described in the device test program. Thus, the timing generator TG generates a periodic clock and a delayed clock. The pattern generator A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More