Time clock and data recovery circuit and integrated chip having the circuit

A technology for recovering circuits and data, applied in the field of data transmission, can solve the problems of large volume and high cost of quartz crystal clock circuits, and achieve the effects of simple circuit structure, low cost and easy implementation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

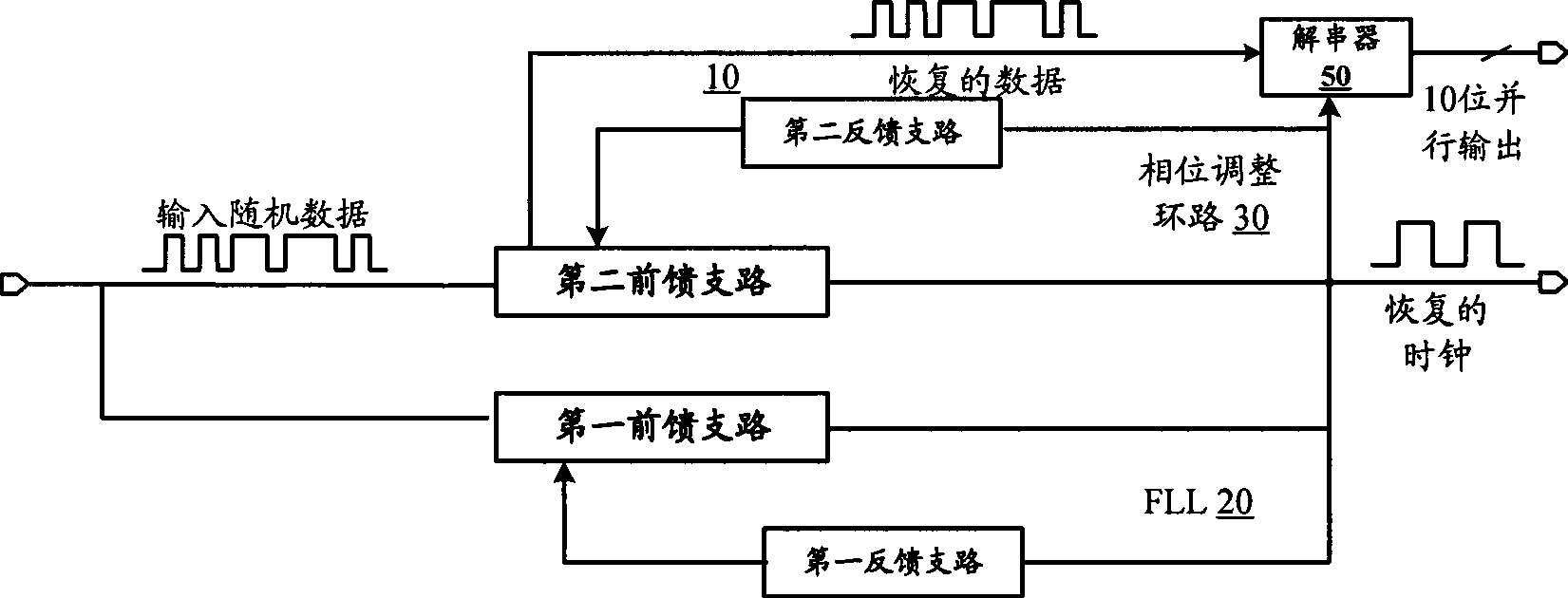

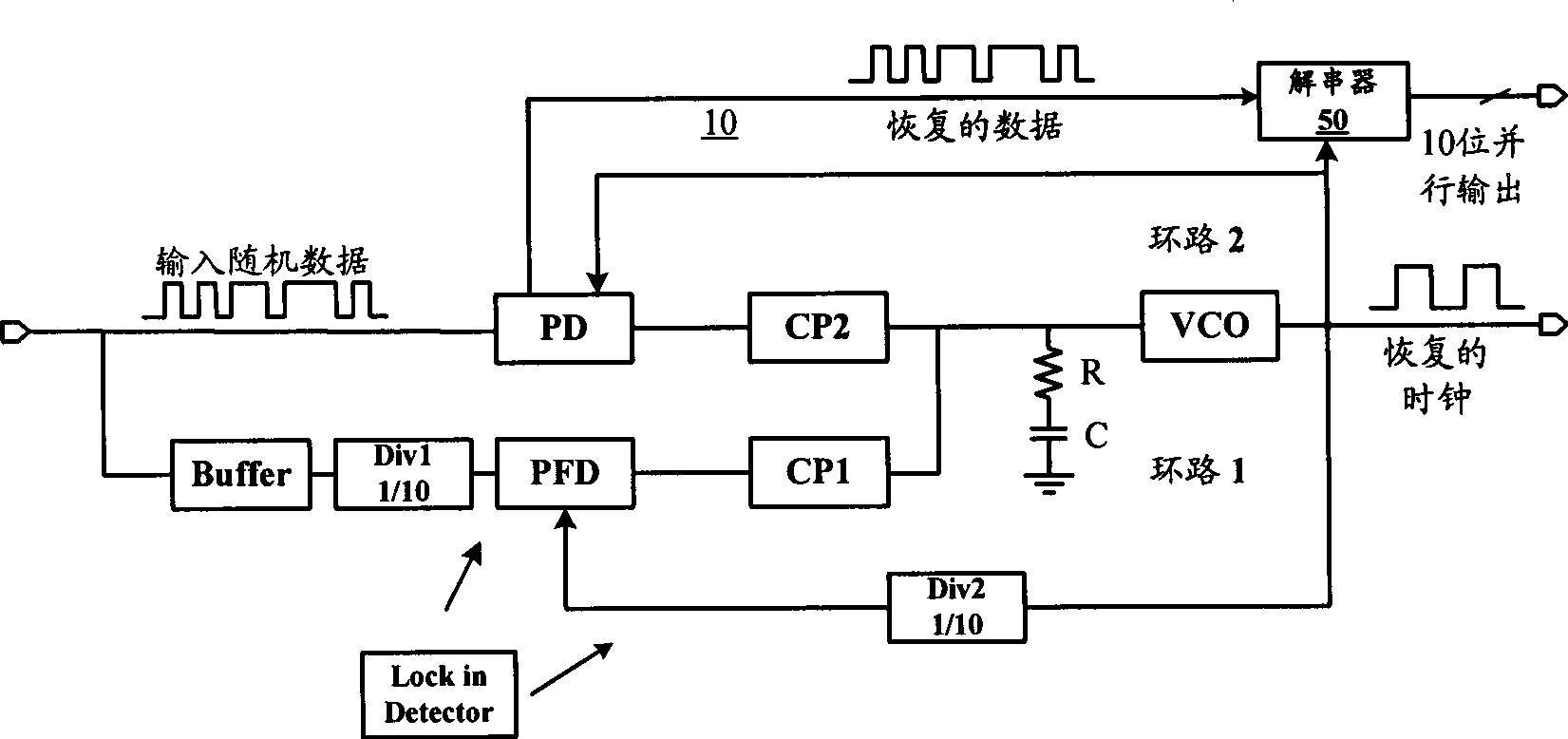

[0029] figure 2 A clock and data recovery circuit according to an embodiment of the present invention is shown, including a data channel 10, a FLL (Frequency Locked Loop, frequency locked loop) 20 and a phase adjustment loop 30, wherein the frequency locked loop is generated using a training signal The clock signal locked to the desired frequency; the phase adjustment loop uses the training signal to adjust the clock signal locked to the desired frequency to the desired phase; the data channel uses the clock signal locked to the desired frequency and adjusted to the desired phase to transmit the recovered data synchronously.

[0030] In this circuit, the training signal is directly used to establish the clock signal, so there is no need to transmit the clock signal during the data transmission process, and it is not necessary to use...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More