Multi-chip 3D stacking and packaging structure

A packaging structure, multi-chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve problems such as poor signal transmission performance, large space for multi-chip packaging structures, and high packaging manufacturing costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

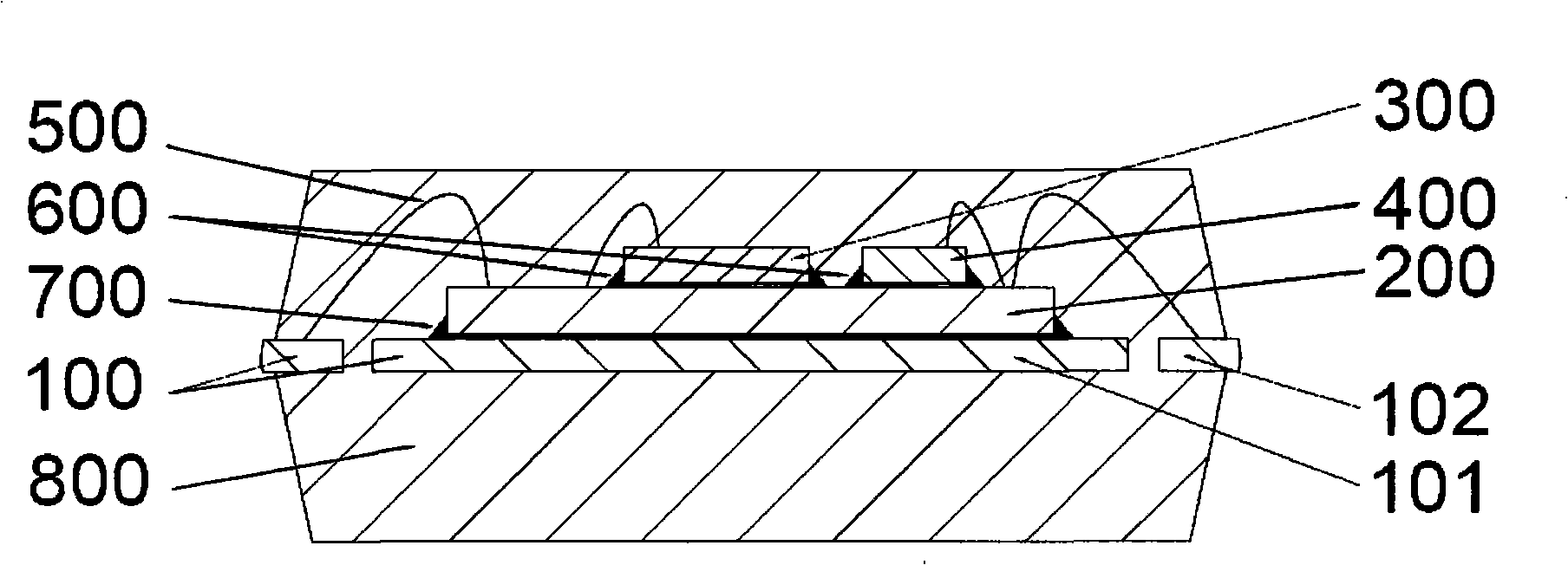

[0019] The following is based on Figure 1 to Figure 6 , give a preferred embodiment of the present invention, and give a detailed description, so that the functions and characteristics of the present invention can be better understood.

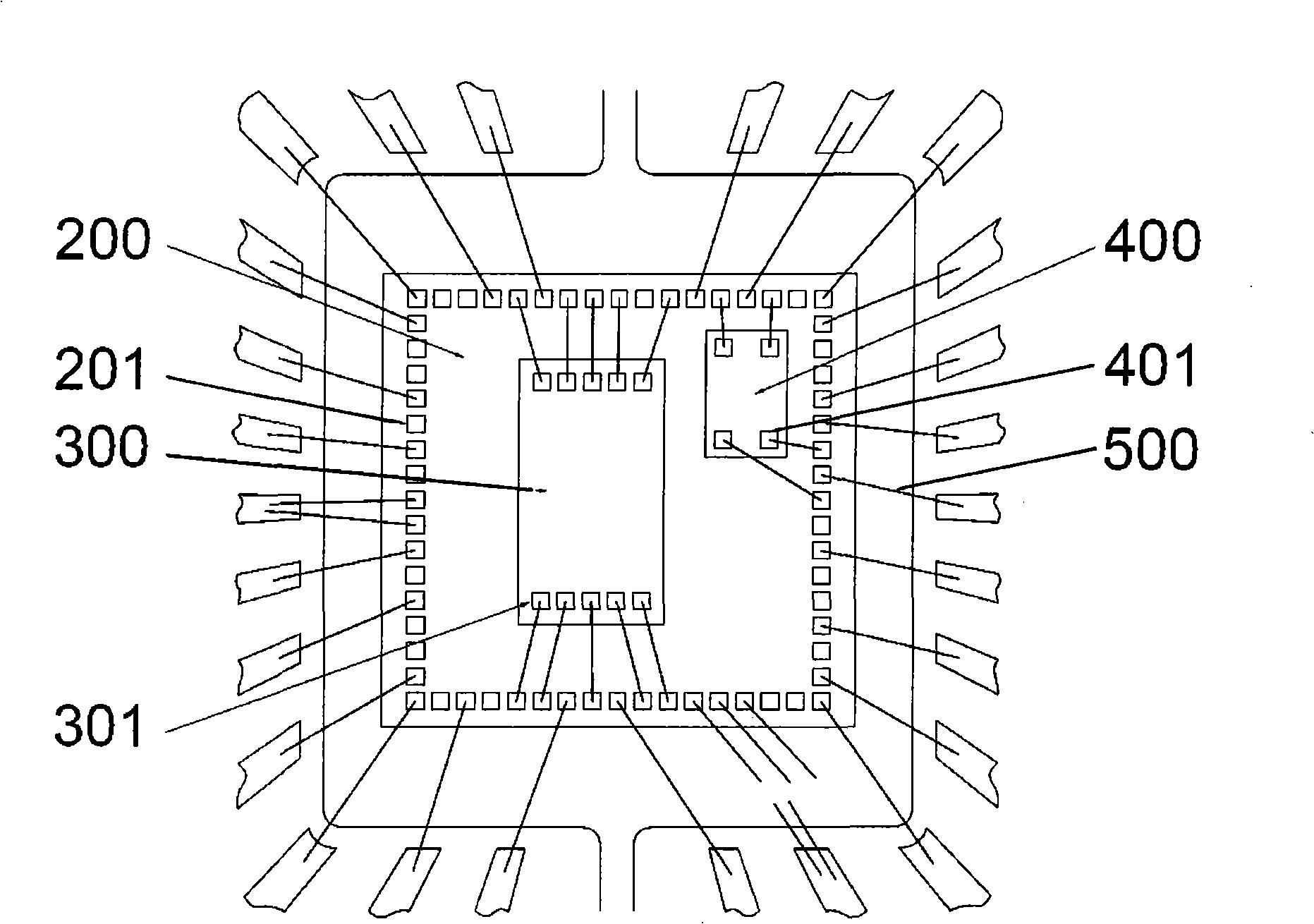

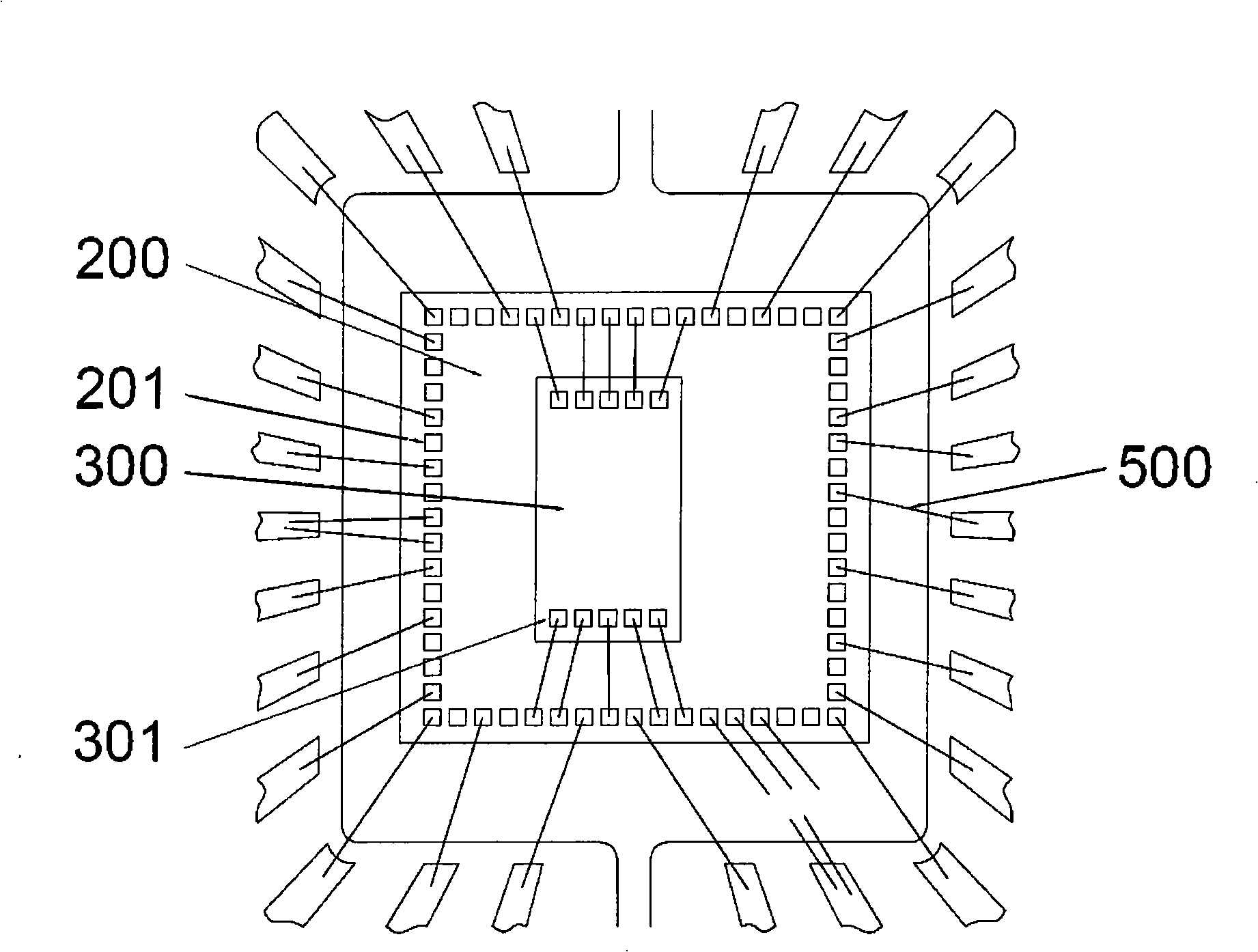

[0020] figure 1 What is shown is a schematic top view of the three-chip 3D stacked package structure of the present invention. A circle of welding pads 201 is formed on the periphery of the circuit surface of the main chip 200. The welding pads 201 can be as follows: figure 1 The single-row distribution shown can also be a double-row distribution (not shown). A row of bonding pads 301 are respectively provided on the upper and lower sides of the auxiliary chip 300 . A plurality of bonding pads 401 are disposed on the periphery of the auxiliary chip 400 . The arrangement of the bonding pads 201 of the main chip 200 is matched with the arrangement of the bonding pads 301 of the auxiliary chip 300 and the bonding pads 401 of the auxiliary chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More