AVS video decoder for software and hardware combined decoding

A video decoder and entropy decoding technology, applied in the field of AVS video decoder structure, can solve problems such as real-time decoding of video that cannot meet standard definition or larger image size, poor compatibility, portability and scalability, and high processor power consumption. , to achieve the effect of easy IP and integration, great flexibility and high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

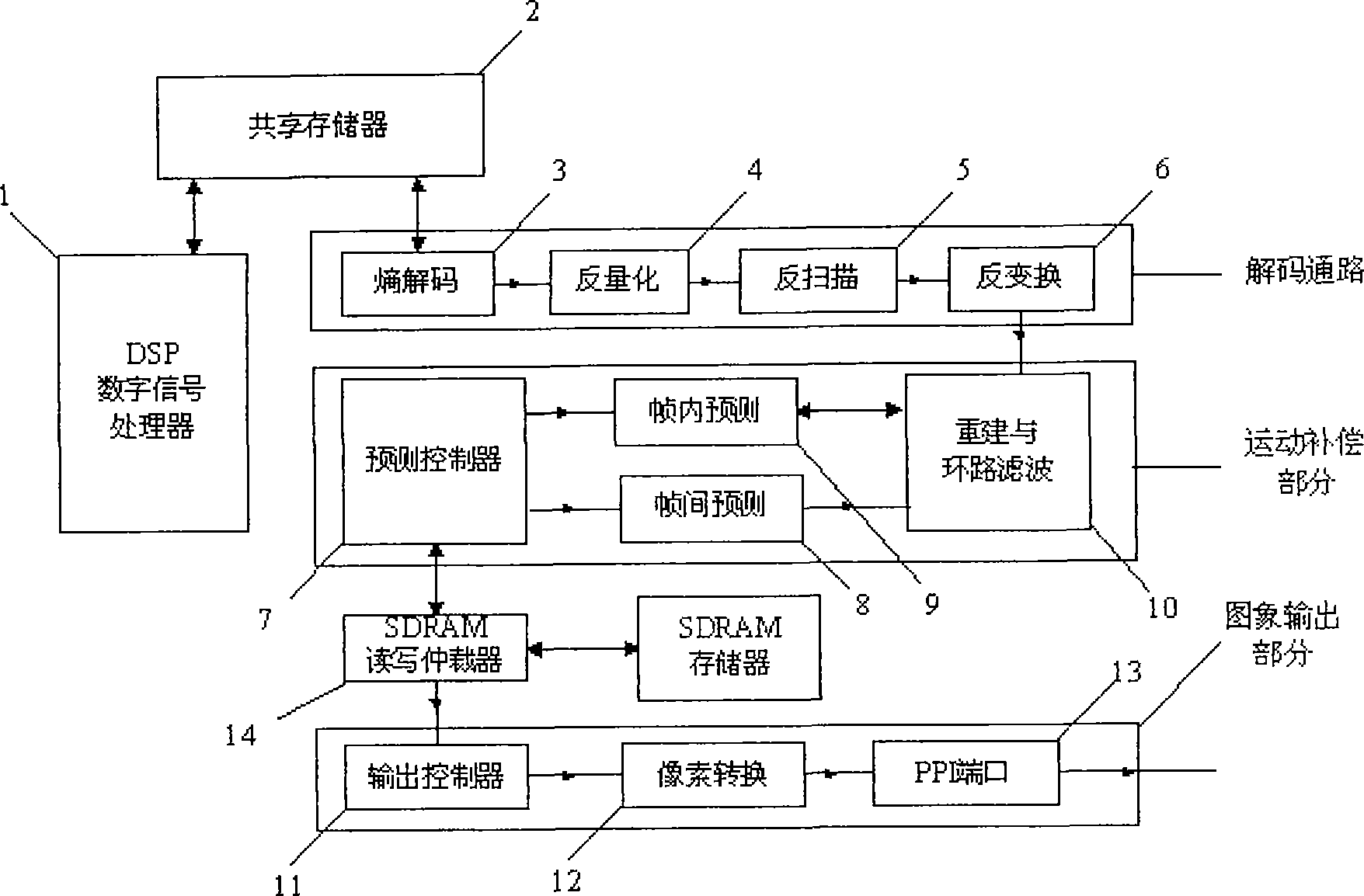

[0025] The AVS video decoder for software and hardware joint decoding can be found in the attached figure 1 . The present invention proposes an AVS video decoder for joint decoding of software and hardware, which uses a DSP digital signal processor and a coprocessor for joint decoding, and is divided into a software part and a hardware part. The software decoding part is completed by DSP, and the analysis of the AVS protocol is completed. Generate various parameters needed for decoding and control the coprocessor decoding process. Due to the great flexibility of DSP programming, the software decoding part can be more flexibly compatible with multiple standards and perform multi-standard protocol analysis. The decoding o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More