Test construction for light doped drain doping region square resistor and manufacturing method thereof

A technology of sheet resistance and test structure, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of film loss, small thickness of NLDD doped region, affecting the detection accuracy of NLDD doped region, etc., to avoid The effect of surface damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0050] When detecting the LDD doping process, it is necessary to form the LDD doping region through the LDD doping process and measure the sheet resistance of the LDD doping region. Usually, in order to save time and cost, multiple test structures including LDD doping regions are formed on a semiconductor substrate, so as to test the entire manufacturing process of semiconductor devices including the LDD doping process. The invention provides a method for manufacturing the test structure of the sheet resistance of the LDD doped region, which can be manufactured synchronously with other test structures, and can protect the LDD doped region from being affected by other manufacturing processes, so that the LDD doped region The sheet resistance can more accurately reflect whether the LDD doping process meets the requirements.

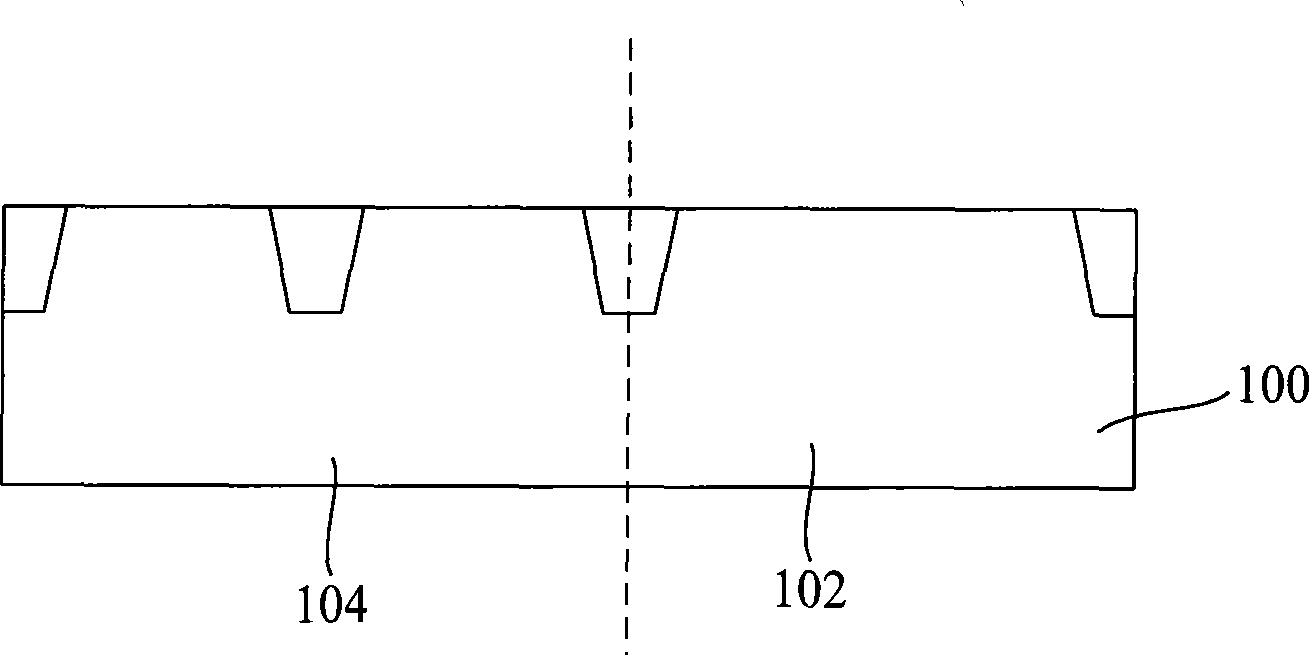

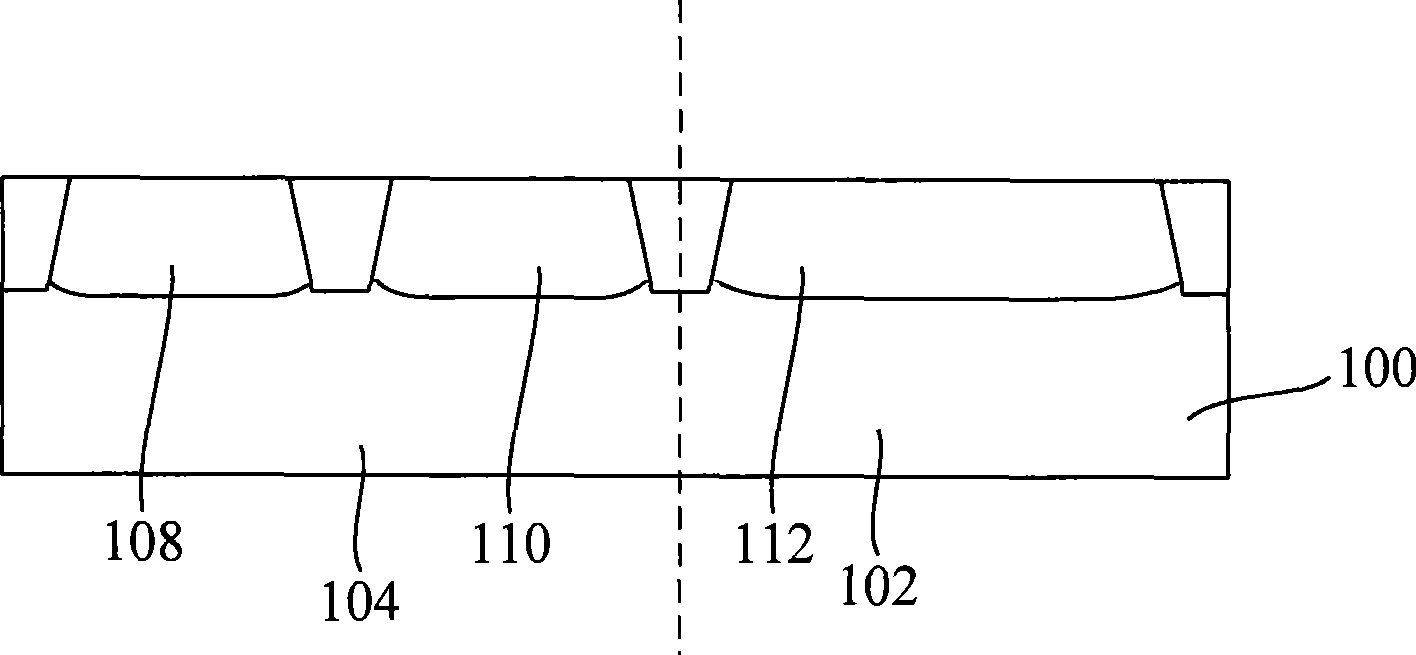

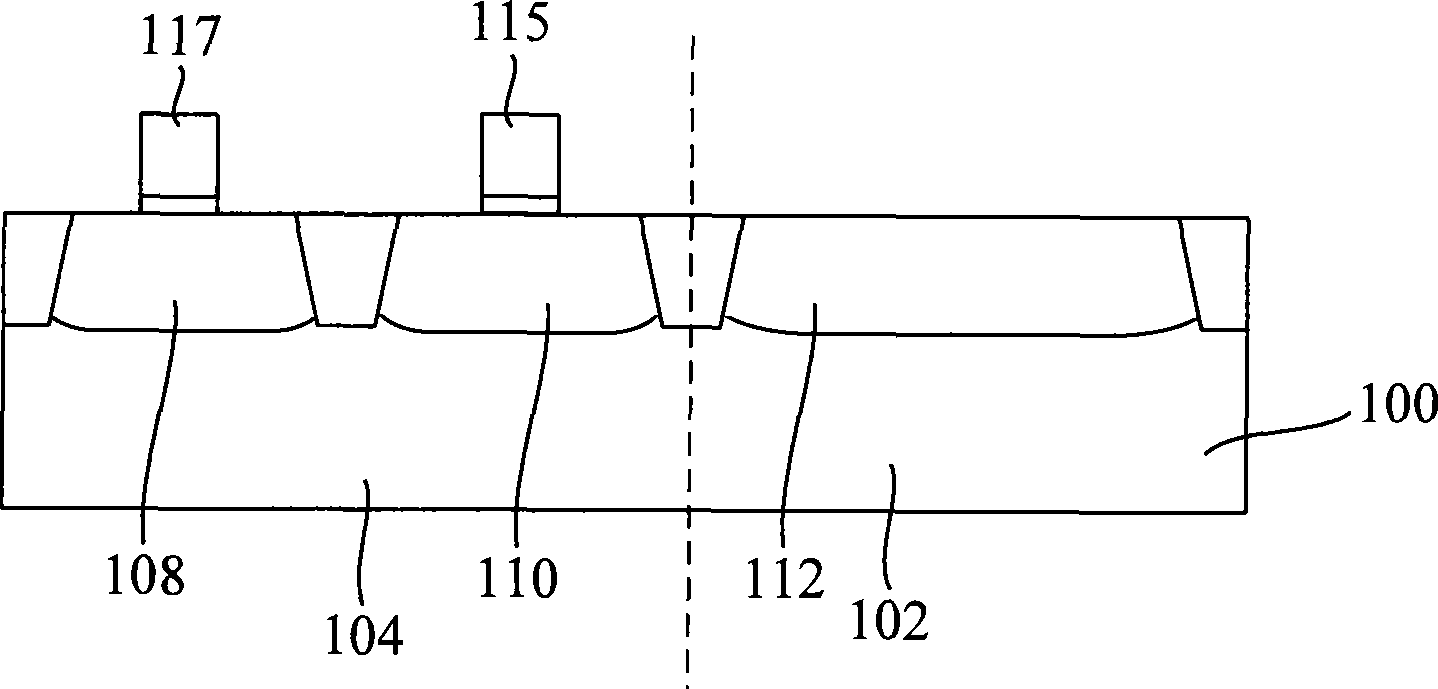

[0051] Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More