Hardware accelerated implementation process for bzip2 compression algorithm

A technology of hardware acceleration and implementation method, applied in the direction of electrical components, code conversion, concurrent instruction execution, etc., can solve the problems of limited use range, slow compression speed, etc., to achieve the effect of speeding up data compression, improving performance, and simplifying design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The specific implementation process of the hardware thread execution method based on the hybrid processor and FPGA architecture is as follows:

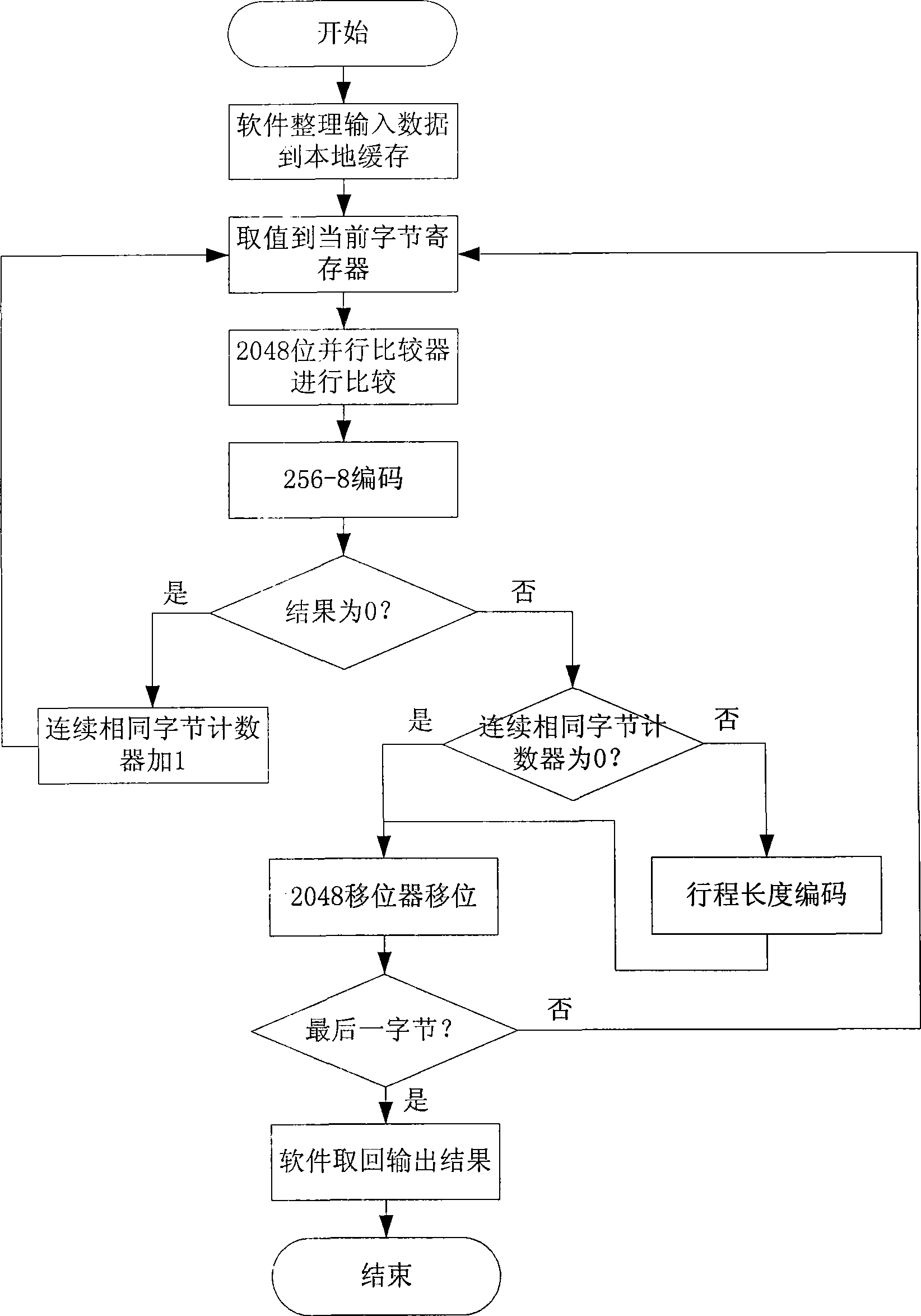

[0034] A method for implementing bzip2 compression algorithm hardware acceleration, the specific steps are as follows figure 1 Shown:

[0035] 1) The software manages the input and output of the accelerator

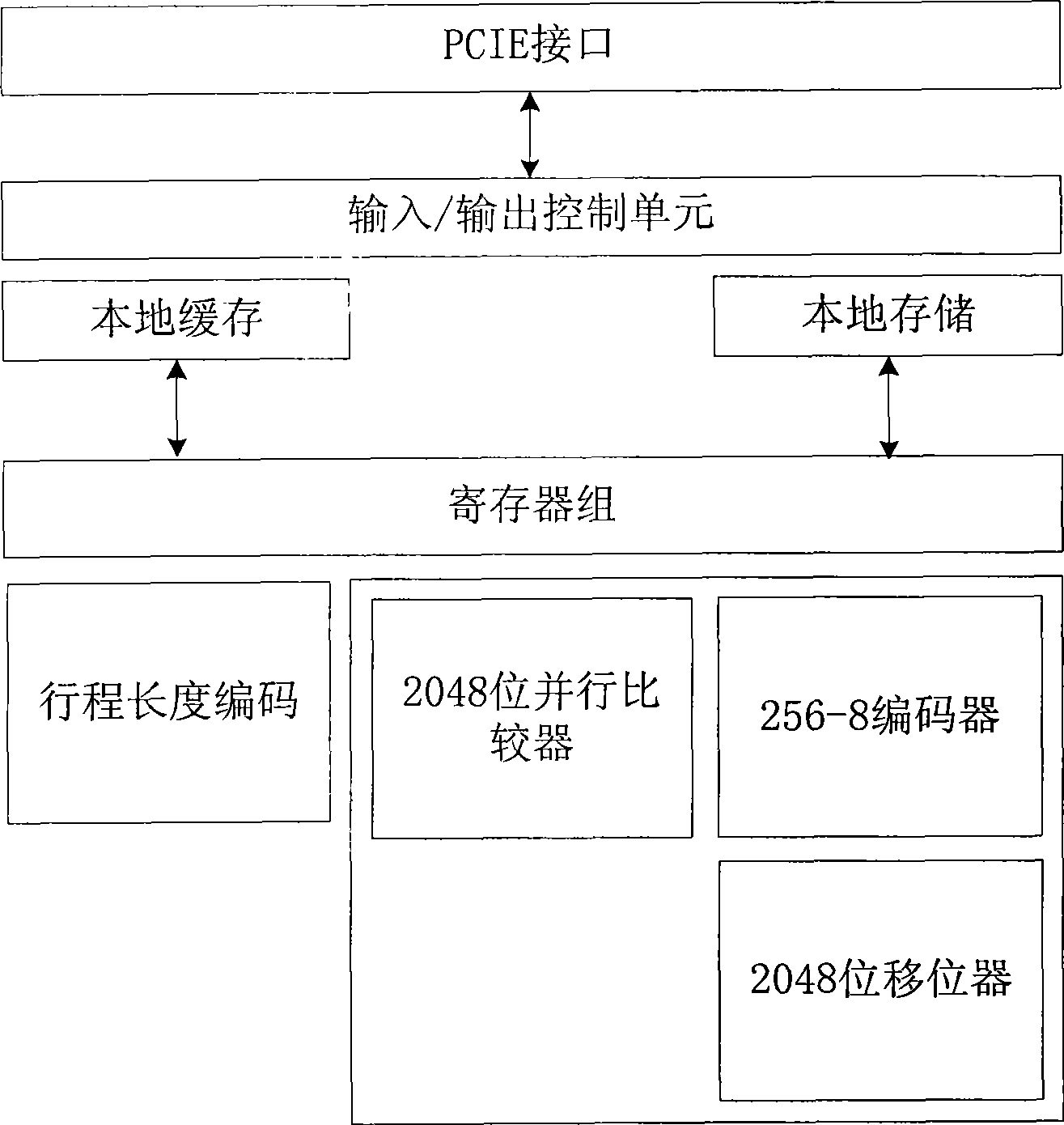

[0036] A hardware accelerator uses an input and output cache as a communication interface with a general-purpose computing system, and a general-purpose computing system refers to a general-purpose computer represented by a traditional desktop computer. The general-purpose computing system accesses the input and output cache of the hardware accelerator through the PCI-E bus. In the present invention, the input cache and the output cache are separated, and the input cache is called a local cache, which is used as the input data of the cache hardware accelerator, and the output cache is called a local storage. , used to st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More