Metal oxide semiconductor (mos) transistors with increased break down voltages and methods of making the same

A transistor and gate oxide technology, applied in semiconductor devices, circuits, electrical components, etc., can solve problems such as increasing the cost of MOS transistors, and achieve the effect of increasing gate breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Specific embodiments of the present invention will be described below. The invention will be described in connection with some specific embodiments of the invention, but the invention is not limited to the specific embodiments described. Any modifications or equivalent replacements made to the present invention shall fall within the scope of the claims of the present invention.

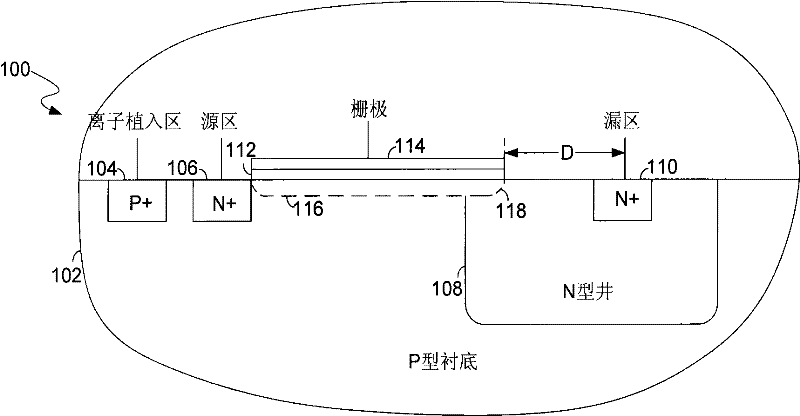

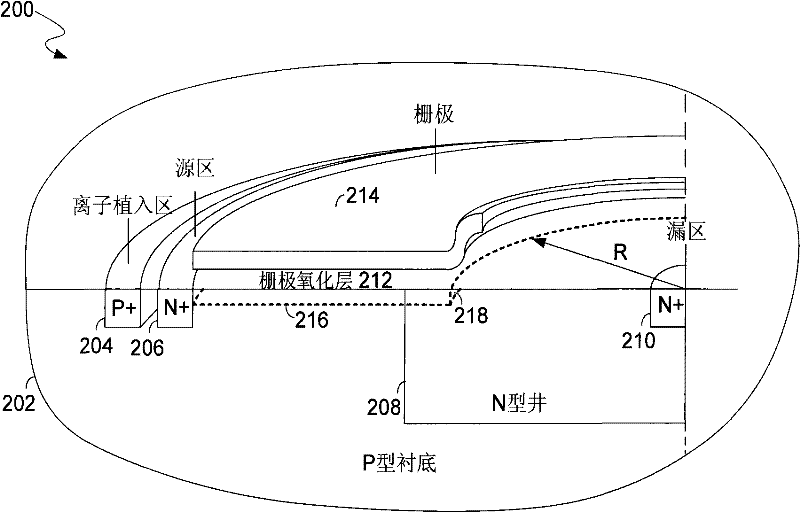

[0018] In one embodiment, the present invention provides a MOS transistor with an improved gate breakdown voltage that can operate at relatively high voltages. In this embodiment, the MOS transistors may be arranged in a predetermined shape (eg, circular) that counteracts junction curvature effects. Therefore, without additional processing steps and masks, the gate breakdown voltage of the MOS transistor can be increased.

[0019] figure 2 Shown is a perspective view of the left half of MOS transistor 200 in accordance with an embodiment of the present invention. MOS transistor 200 may be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More