Structure of semiconductor chip with silicon through hole and stacking assembly thereof

A semiconductor and through-silicon via technology, used in semiconductor devices, semiconductor/solid-state device components, electrical solid-state devices, etc., can solve problems such as poor process yield and difficult chip alignment, avoid displacement, and reduce stacking height. , The effect of easy stacking alignment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

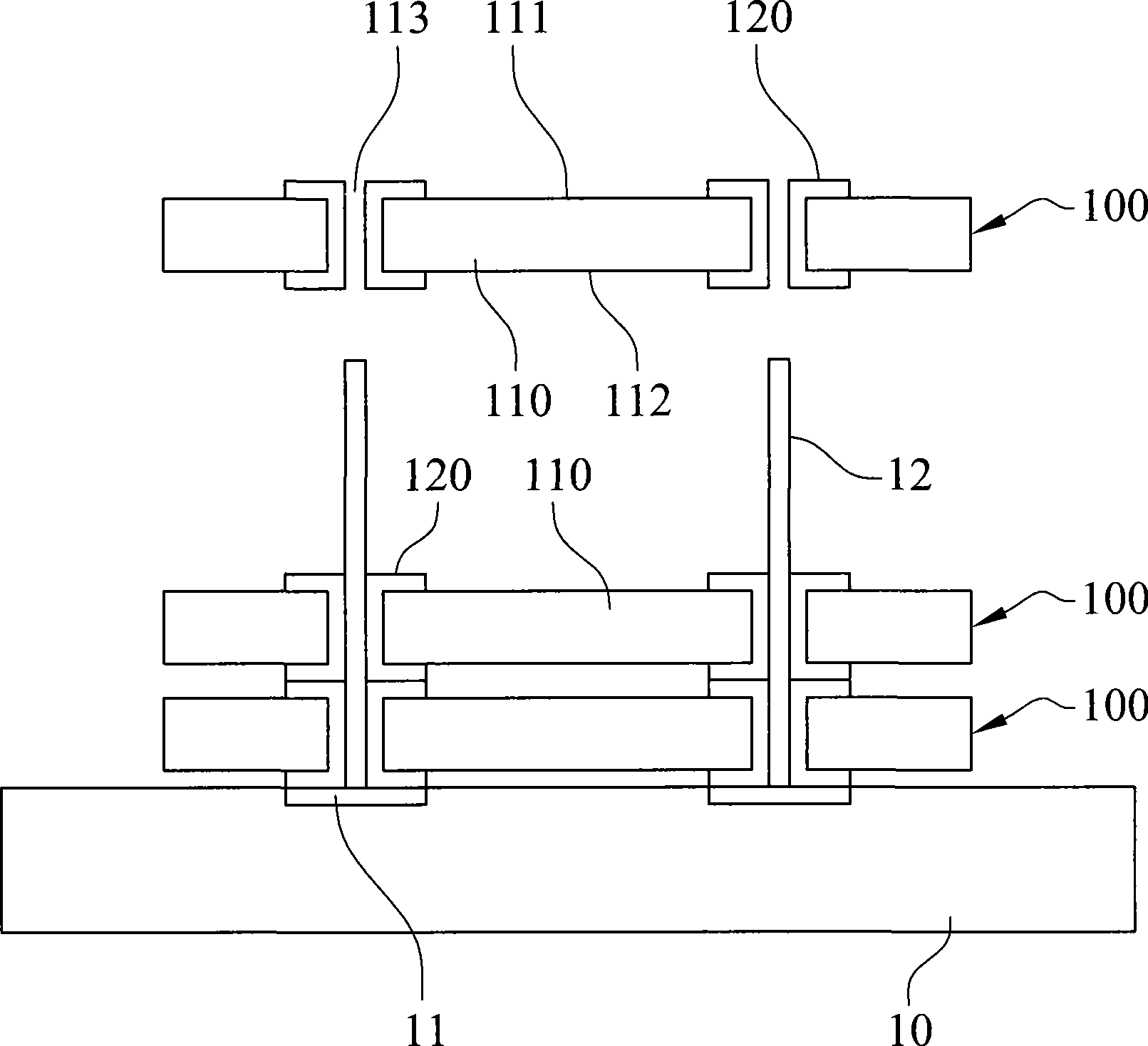

[0068] According to a first specific embodiment of the present invention, a semiconductor chip structure with TSVs and a stacking combination thereof are provided. see image 3 As shown, a semiconductor chip structure 200 with through-silicon vias mainly includes a semiconductor substrate 210, two or more first pads 220, two or more second pads 230, two or more The first flange ring 240 and two or more second flange rings 250 . The semiconductor substrate 210 has a first surface 211 , an opposite second surface 212 and two or more through holes 213 passing through the first surface 211 and the second surface 212 . The semiconductor substrate 210 is made of semiconductor material, such as silicon, gallium arsenide and the like. A surface of the semiconductor substrate 210 can be formed with various integrated circuits and can be electrically connected to the first bonding pads 220 and two or more than two second bonding pads 230 . Preferably, the integrated circuit is formed...

no. 2 Embodiment

[0077] In the second embodiment of the present invention, another semiconductor chip structure with TSVs and its stacking combination are disclosed. see Figure 8As shown, a semiconductor chip structure 300 with TSVs mainly includes a semiconductor substrate 310 , a first bonding pad 320 , a second bonding pad 330 , a first flange ring 340 and a second flange ring 350 . The semiconductor substrate 310 has a first surface 311 , an opposite second surface 312 , a first half-through hole 313 formed in the first surface 311 , and a second half-through hole 314 formed in the second surface 312 . Specifically, the first half-through hole 313 and the second half-through hole 314 can be half-etched and plated to form blind holes.

[0078] The first pad 320 is disposed on the first surface 311 , and the first half-through hole 313 also penetrates through and vertically corresponds to the first pad 320 . The second welding pad 330 is disposed on the second surface 312 , and the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More