Flip-chip packaging method and structure

A technology of packaging structure and packaging method, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of increasing the difficulty of primer, shrinking solder mask openings, and difficulty in printing solder materials.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

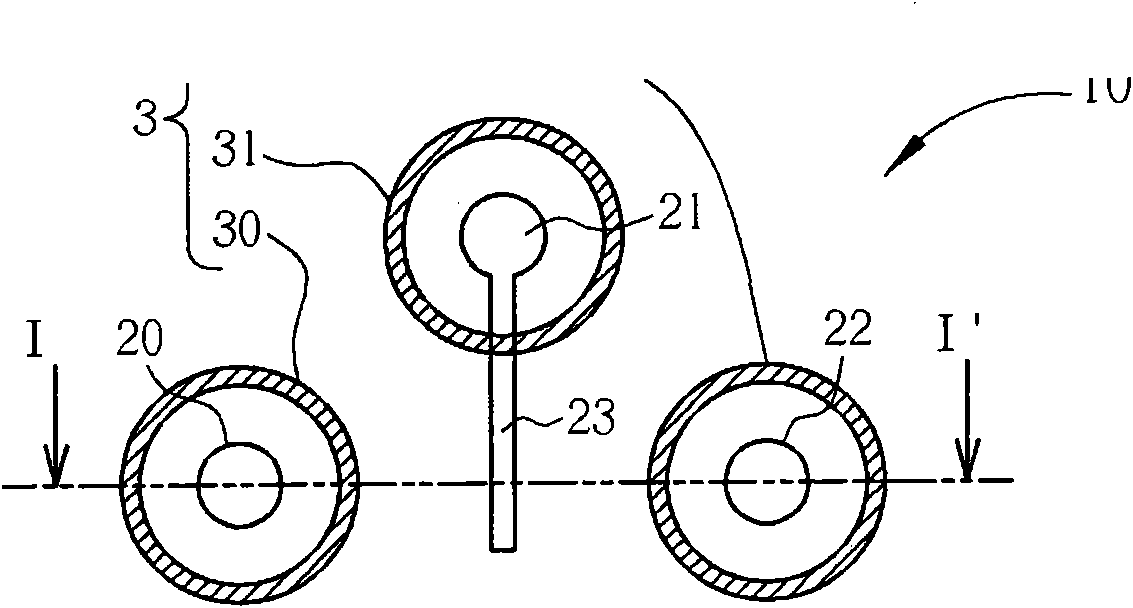

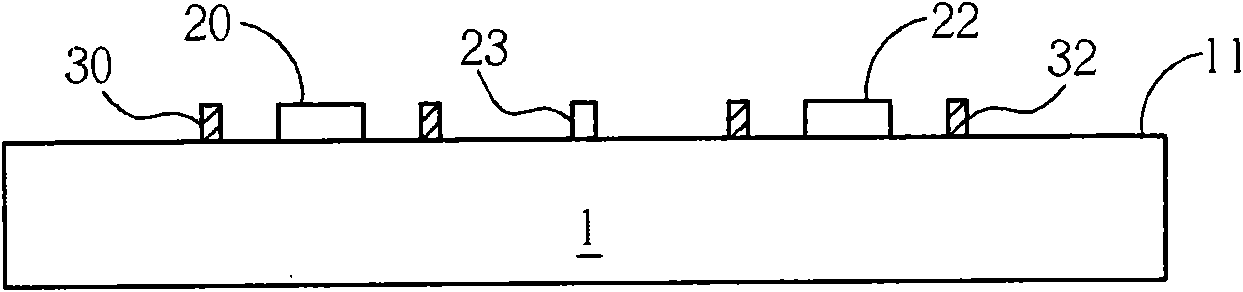

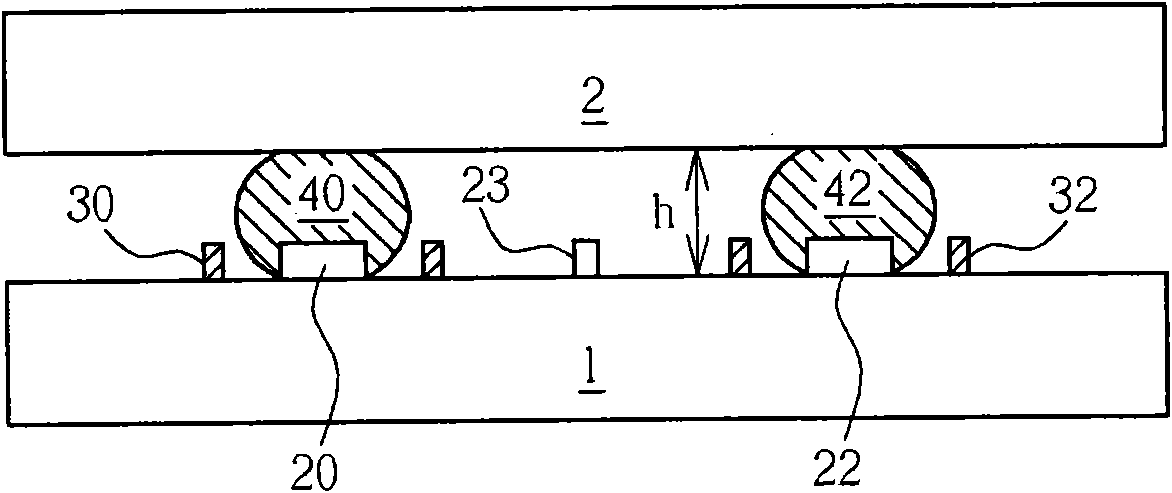

[0027] see figure 1 and figure 2 ,in figure 1 It is a schematic top view of a flip-chip solder resist pattern according to an embodiment of the present invention, figure 2 for along figure 1 The cross-sectional schematic diagram drawn by the middle tangent line I-I'. Such as figure 1 and figure 2 As shown, a substrate 1 is provided at first, and then metal patterns 20, 21, 22 and 23 are formed in a predetermined area 10 of the substrate 1, wherein the metal patterns 20, 21, 22 are metal pads for contact with the tin on the chip. Balls or bumps are combined, and the metal pattern 23 is a metal thin wire connected to the metal pattern 21 .

[0028] According to an embodiment of the present invention, the substrate 1 may be a plastic substrate or a ceramic substrate, etc., and a multi-layer interconnection structure (not shown) may be formed therein. The metal patterns 20 , 21 , 22 and 23 may be made of copper, other metals or metal alloy materials. The methods for for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More