Optimization method of printed-circuit board test path

A technology for printed circuit boards and test paths, applied in electrical digital data processing, instruments, calculations, etc., can solve problems such as building models and failing to achieve efficiency, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

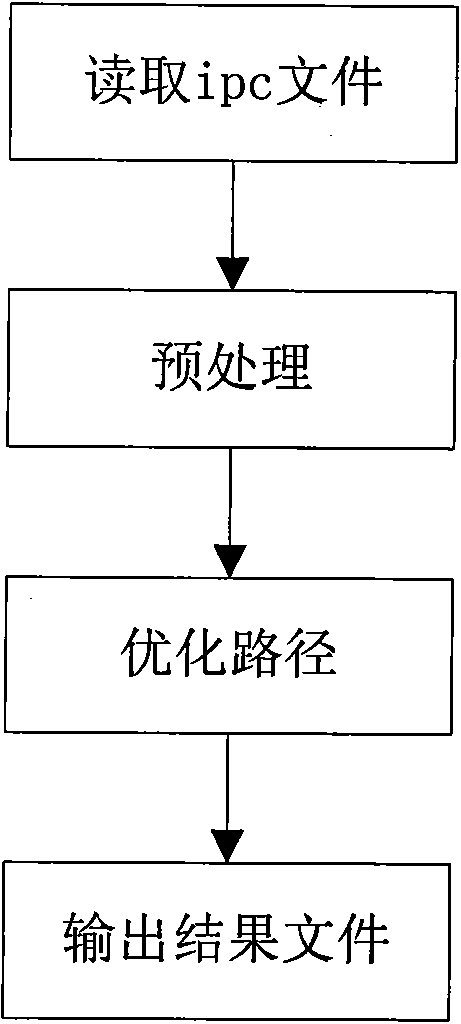

[0063] see figure 1 , a printed circuit board test path optimization method, the method comprises the steps of:

[0064] The method comprises the steps of:

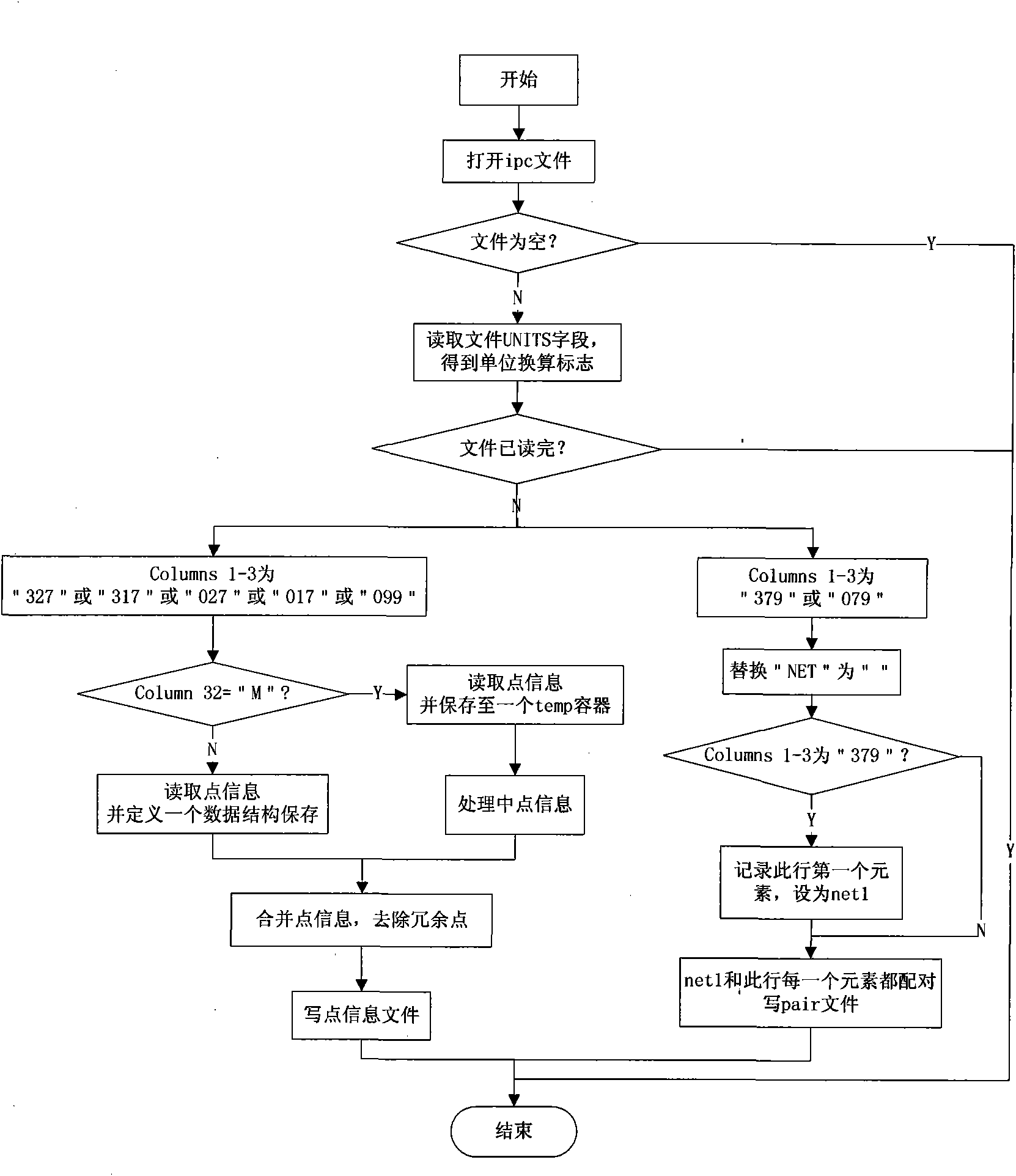

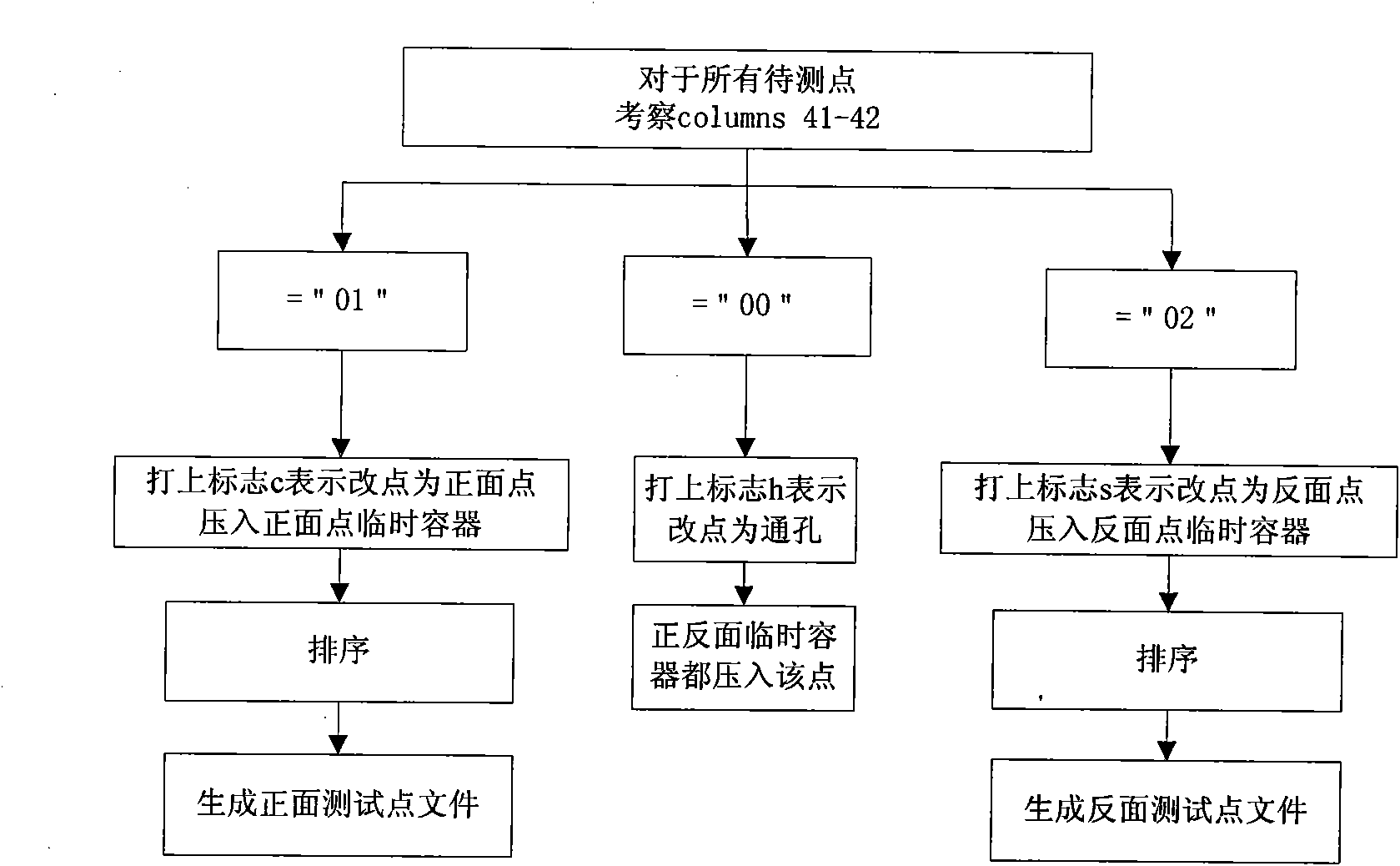

[0065] A. Read the ipc file to obtain the network number, front and back signs, coordinate information, and information of the adjacent network to which the point to be measured belongs;

[0066] The ipc file used in this method is a standard file in the flying probe testing industry, and its standard number is IPC-D-356: Test data format for the bare board of the bottom circuit board. Each line of the file will not exceed 80 characters. For each Character bits have strict definitions, which contain a lot of information, including point location information, size, board layers, etc., according to its strict bit definition, combined with the needs of short-circuit testing, we only need to read the file where the point to be tested belongs to The network number, front and back logo, coordinate information, and information...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More