Semiconductor device

一种半导体、器件的技术,应用在半导体器件领域,能够解决半导体器件特性变化、杂质浓度变化等问题,达到抑制特性变化、抑制峰的出现的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Embodiments of the present invention are now described below with reference to the accompanying drawings. Note that, in the drawings, the same reference numerals denote the same structural components and descriptions thereof are appropriately omitted.

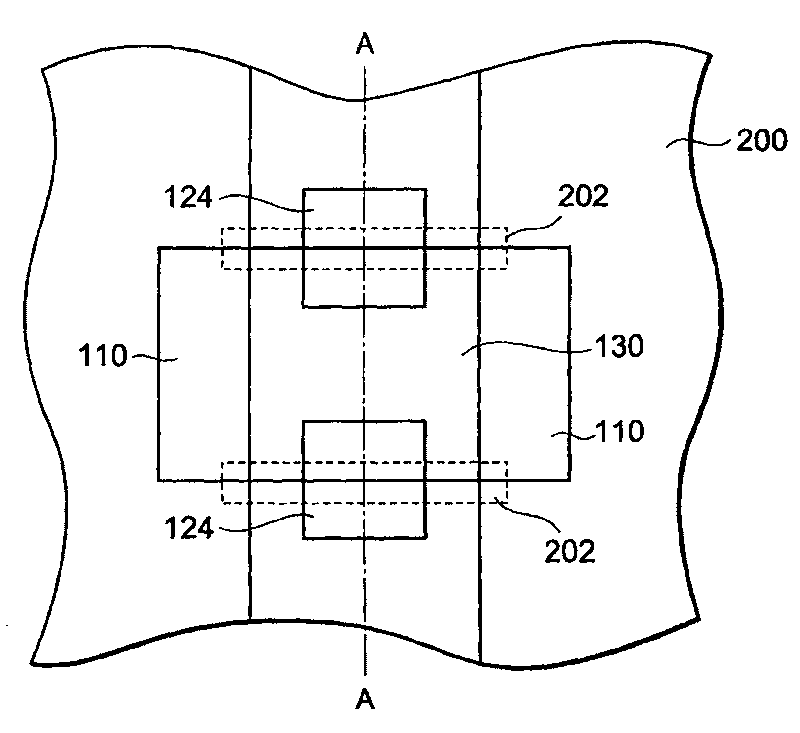

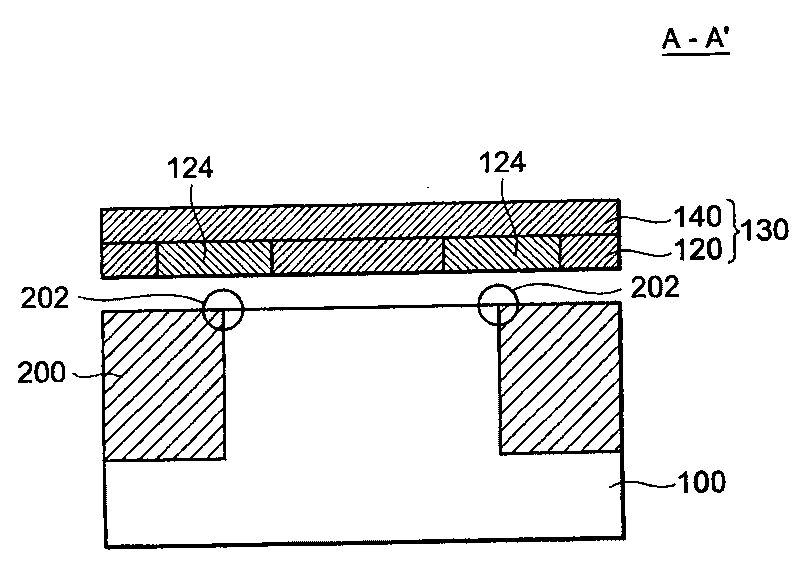

[0019] figure 1 A schematic plan view showing the structure of the semiconductor device according to the present embodiment. figure 1 The semiconductor device shown in includes an element isolation film 200, a gate electrode 130, and two impurity regions 110 which are a source region and a drain region. The element isolation film 200 is formed in the semiconductor layer and defines an element formation region. The gate electrode 130 is formed over the element formation region. Each end of the gate electrode 130 extends over the element isolation film 200 . Impurity region 110 is formed in the element formation region so as to sandwich the channel formation region below gate electrode 130 therebetween.

[0020] Two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More