Bit line cutting buffer

A buffer and bit line technology, applied in the direction of instruments, static memory, digital memory information, etc., can solve the problem of serious impact, reduce the impact, facilitate the rapid reading of register file content, and improve the effect of discharge time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

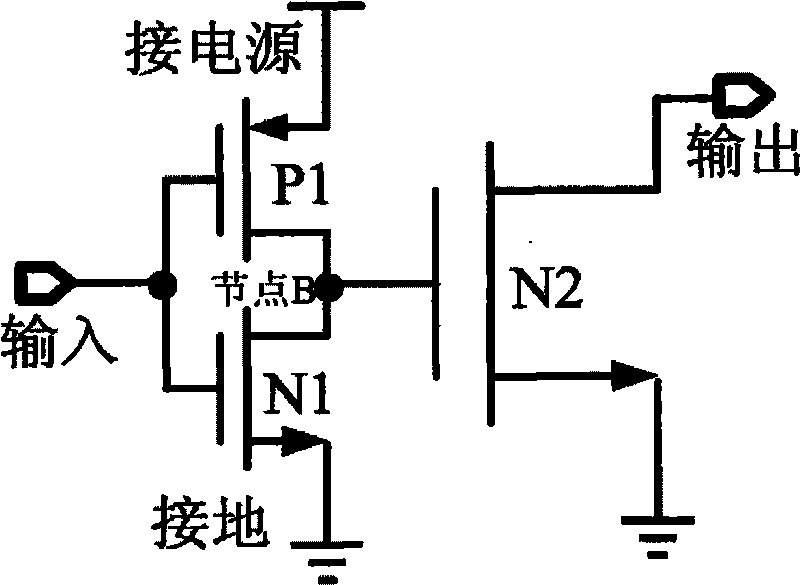

[0023] figure 1 A circuit diagram of a bit line buffer in the present invention is shown. P1 and N1 form a NOT gate, and the input terminal IN is connected to the previous stage bit line. The output of the NOT gate is connected to the gate (node B) of the transistor N2 to control whether N2 discharges the lower bit line connected to the output terminal OUT. Among them, the size of the open-drain transistor N2 is larger, which is beneficial to accelerate the discharge speed of the lower bit line.

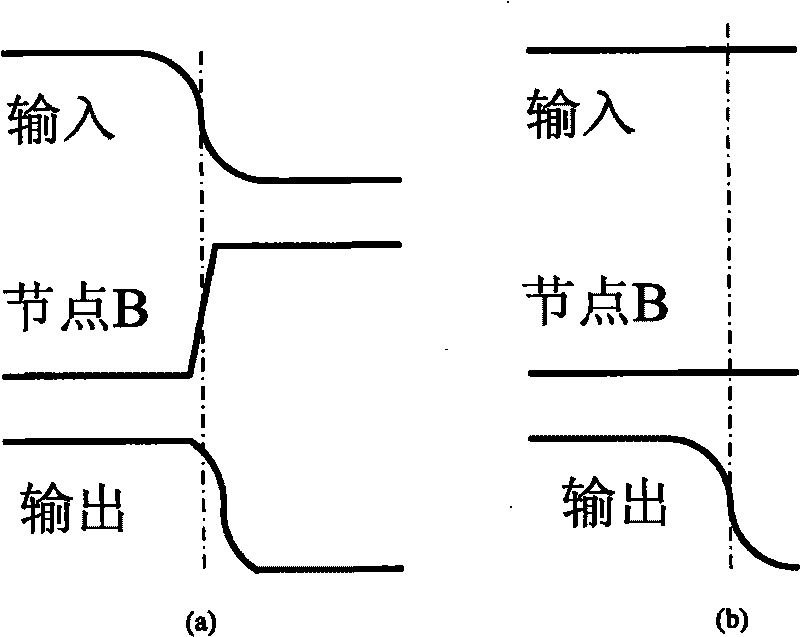

[0024] figure 2 A waveform diagram of the bit line buffer in the present invention is shown. figure 2 (a) shows a waveform diagram in which the input bit line starts to discharge causing the lower bit line to discharge. It can be seen from the figure that the discharge speed of the lower stage has been greatly improved due to N2. figure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More