Esd protection circuit and circuitry of ic applying the ESD protection circuit

An electrostatic discharge protection, electrostatic discharge technology, applied in emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, circuits, etc., can solve the problems of increasing chip size and VLSI circuit size. , to avoid damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The following description is of the preferred contemplated mode of carrying out the invention. This description serves only to illustrate the principles of the present invention, and not to limit the present invention. The protection scope of the present invention should be defined by the scope of the appended claims.

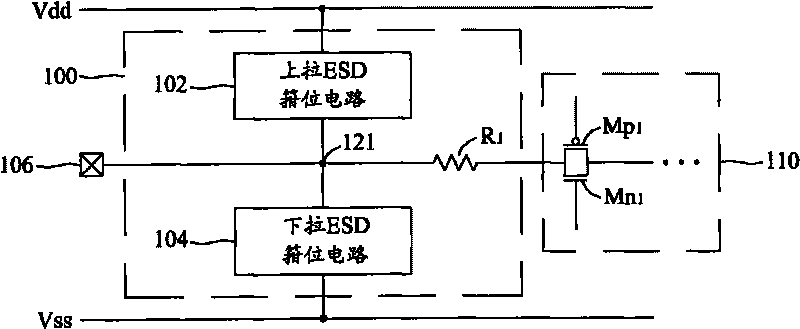

[0018] figure 1 is a schematic diagram of an integrated circuit including an ESD protection circuit 100 . The ESD protection circuit 100 blocks ESD from the input / output pad unit (I / O pad, hereinafter referred to as I / O pad unit) 106 to the internal circuit 110 . The ESD protection circuit 100 includes a pull up (PU) ESD clamp circuit 102 , a pull down (PD) ESD clamp circuit 104 and a resistor R1 . The I / O pad unit 106 is coupled to the node 121 for receiving or transmitting signals. The pull-up ESD clamping circuit 102 is coupled between the first voltage path (ie, the voltage path whose voltage level is Vdd) and the node 121, and is used for clampi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More