Multi-interface memory verification system based on FPGA

A verification system and memory technology, which is applied in the field of multi-interface memory verification systems based on field programmable gate arrays, can solve problems such as waste of resources, inability to test performance completely, and inability to completely simulate the actual use environment of high-speed memory, so as to shorten the effect of time period

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

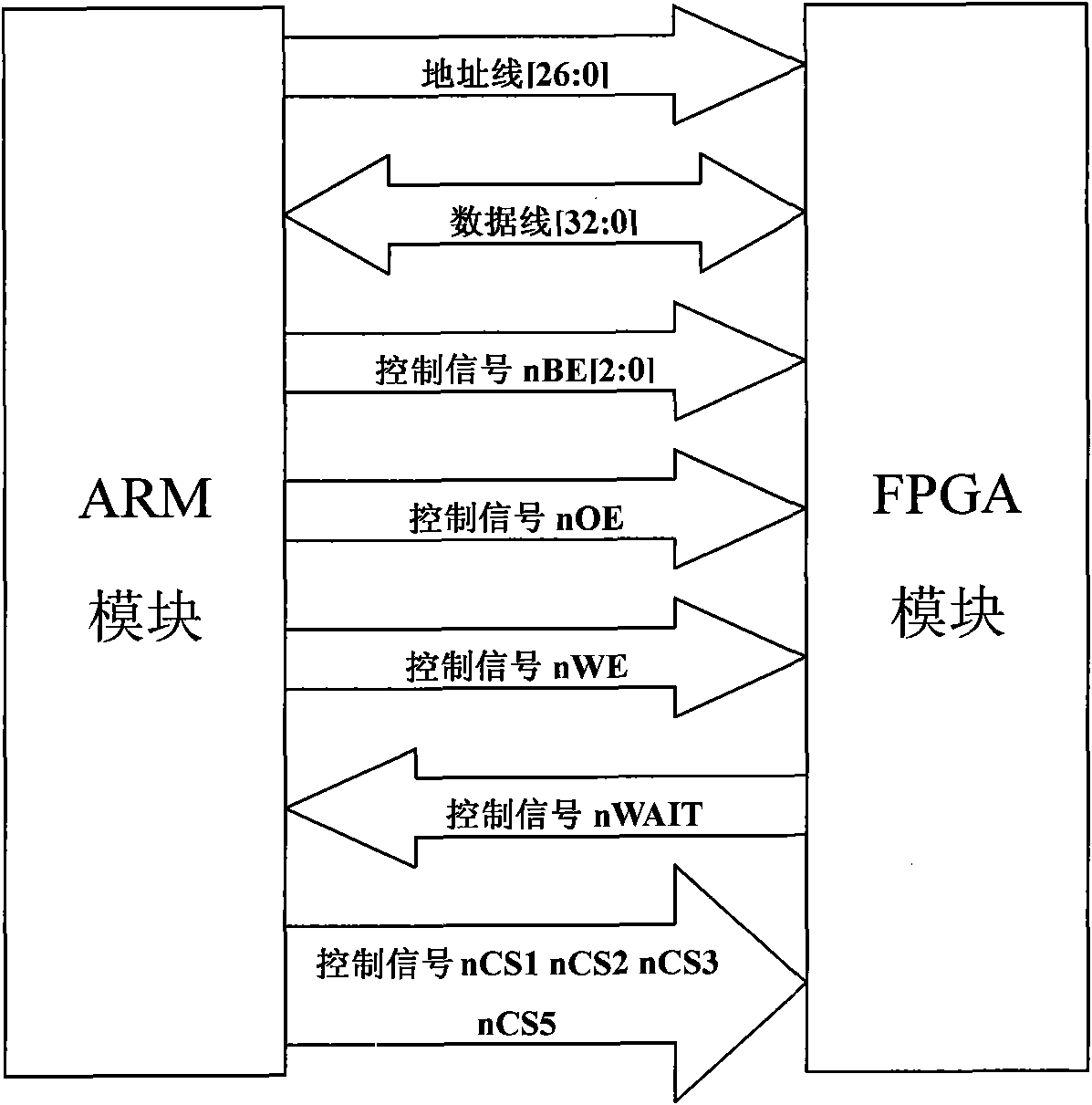

[0025] The invention consists of two modules: ARM module and FPGA module. The two modules are connected by a bus (the FPGA end imitates SRAM memory), and the FPGA end simulates the SRAM external memory, and the FPGA internal controller logic is mapped to the ARM memory to provide data and control access interfaces. Because the access characteristics of various memories are different, the ARM and FPGA communication part adopts a full bus connection, that is, all data lines, address lines, and control lines are all connected to FPGA. Such as figure 1 The overall architecture diagram of the system is shown.

[0026] (1), ARM module

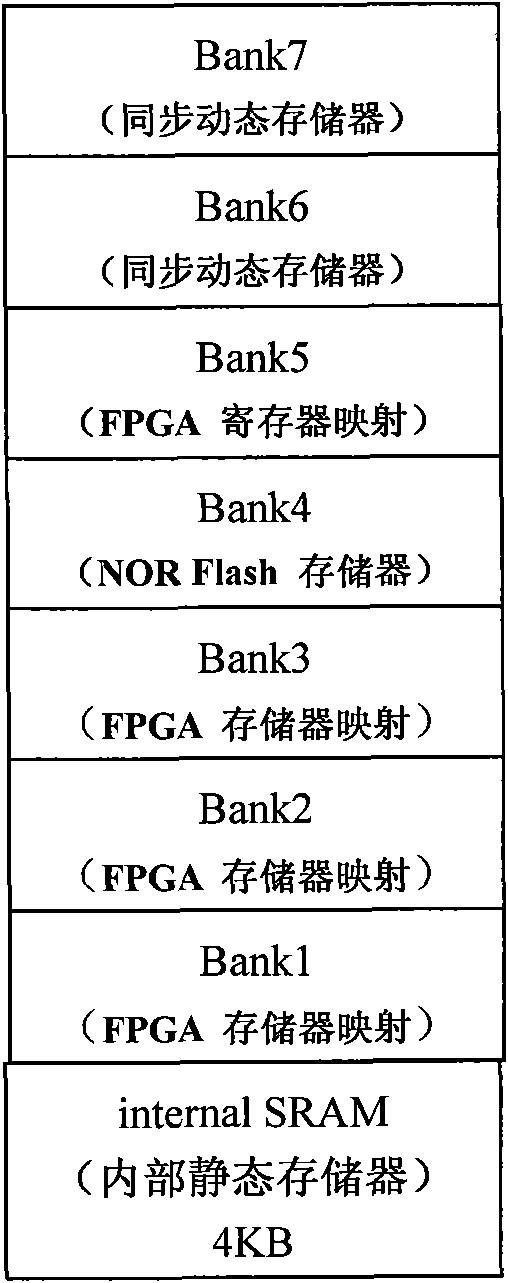

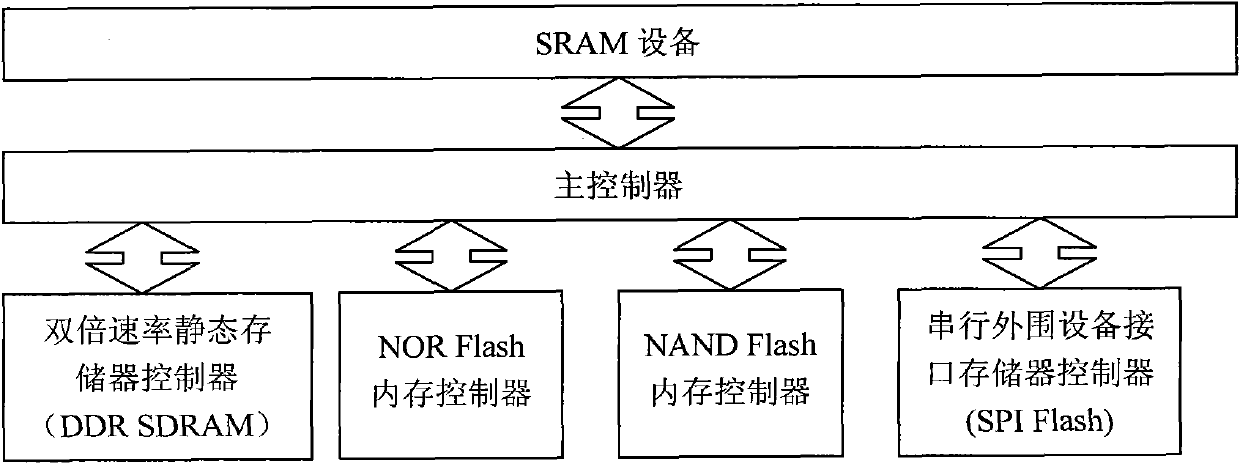

[0027] The ARM module adopts Samsung S3C2440Mobile MCU as the system controller. This MCU is based on the M920T core, has rich on-chip peripherals, supports EBI (External Bus Interface), and provides conditions for FPGA communication. It can run Linux and Windows CE operating systems, providing popular application platform support for the entire v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More